一种基于锁频同步的发变组保护并行处理方法和平台与流程

1.本发明属于电力系统继电保护技术领域,涉及一种基于锁频同步的发变组保护并行处理方法和平台。

背景技术:

2.大型发电机变压器组是现代电力系统最重要的组成部分之一,随着工业水平的不断发展,单台机组的容量和自动化控制程度不断增加,对发电机变压器组继电保护的可靠性要求也越来越高。大型发电机变压器组保护的对象包括主变压器、发电机、高压厂用变压器、励磁变压器,同时主接线和运行工况多样,保护功能类型多、接口复杂等,对发变组保护硬件平台的性能和可靠性提出了更高的要求。

3.目前国内外主流厂家的发变组保护处理平台架构主要分为如下两种方案:

4.方案一是发变组保护的所有功能由一个处理系统,即多cpu串行处理完成,处理系统包括用于模拟量转换的ad模块、用于保护逻辑处理的cpu模块、开关量输入模块、跳闸/信号开关量输出模块、电源模块等,模块之间为串行关系。

5.方案二是发变组保护根据保护对象的不同,由多个异步运行的子处理系统完成,比如主变保护子处理系统、发电机保护子处理系统和高厂变保护子处理系统。每个子处理系统包括独立的用于模拟量转换的ad模块、用于保护逻辑处理的cpu模块;开关量输入模块、跳闸/信号开关量输出模块、电源模块等则为几个子系统共用。

6.方案一的优点是所有的模拟量统一采集、所有的保护逻辑在一个保护处理模块中完成,这样可以保证发变组所有保护处理的同步性、实时性,以及故障录波的一致性。缺点是一旦模拟量转换模块或保护逻辑处理模块出现故障,所有的主变压器保护、发电机保护、高厂变保护等都将失去,降低了整个保护系统的可靠性。

7.方案二的优点是发电机保护由主变保护子处理系统、发电机保护子处理系统和高厂变保护子处理系统组成,某个子处理系统的模拟量转换模块或保护逻辑处理模块出现故障仅退出受影响的子处理系统,而其它子系统还可以正常工作,相较与方案一来讲,方案二整个保护系统的可靠性大大提高。缺点是每个子系统非同步运行,模拟量采集和保护处理模块都以各自的节拍来工作,如想利用其它子系统的模拟量采集结果或保护处理结果进行综合判别则存在困难或增加平台设计的复杂度;同时每个子处理系统的故障录波很难合并,不利于事故的故障分析。

8.为了保证大型发电机变压器保护的可靠性,亟需对现有的发变组保护处理平台架构设计方法予以改进,研究高可靠性的发变组保护并行处理平台架构设计方法。

技术实现要素:

9.本发明提供一种基于锁频同步的发变组保护并行处理方法和平台,每个发变组保护处理子系统既可以锁频同步负载均衡运行,又可以高可靠自治运行。兼顾了整个发变组保护处理的同步性、实时性和可靠性。

10.本发明采用如下技术方案:

11.一种基于锁频同步的发变组保护并行处理方法,所述方法包括以下步骤:

12.步骤1:将发变组保护根据保护对象分成若干个保护处理子系统,每个子系统都连接到同步总线上;

13.步骤2:子系统按序向同步总线发送同步信号及信号的有效标志,并检测接收总线上的同步信号,在预设的延时时间内,若能接收到有效的同步信号,则子系统进入锁频同步运行模式,进行发变组保护并行处理,否则子系统进入自治运行模式。

14.本发明进一步包括以下优选方案:

15.优选地,所述子系统为独立的物理板卡或同一物理板卡上的不同功能区域。

16.优选地,每个子系统包括独立的用于模拟量转换的ad模块、用于保护逻辑处理的cpu模块。

17.优选地,每个子系统可接收同步总线上的同步信号并锁定同步信号频率,亦可发送同步信号及信号的有效标志到同步总线上,用于并行冗余实时计算,并通过同步总线实时交互信息,输出统一的出口结果。

18.优选地,所述同步总线为多模总线smbg。

19.优选地,发变组保护上电后,每个子系统通过预先设定的身份识别标志id来确定本子系统的序号;

20.子系统发送到同步总线的同步信号中包含自身的id,以供其它子系统识别。

21.优选地,所述预设时间为(m+1)*

△

t,其中,m为子系统的总个数,

△

t为同步信号一个最小频率周期的时间。

22.优选地,步骤2具体包括:

23.步骤21:发变组保护上电后,第1个子系统将同步信号及信号的有效标志发送到同步总线上;

24.步骤22:所有子系统检测接收总线上的同步信号,判断是否存在有效的同步信号,若存在,则锁定同步信号,子系统的ad模块、cpu模块根据同步信号的节拍进行工作,进入锁频同步运行模式;

25.步骤23:若第n个子系统在等待n*

△

t时间后,仍然没有收到有效的同步信号,再将本子系统的同步信号及信号有效标志发送到同步总线上,返回步骤22;

26.其中,n为子系统的序号,m≥n≥2,m为子系统的总个数;

27.步骤24:若所有子系统在等待(m+1)*

△

t时间后,仍然没有收到有效的同步信号,则按照本子系统的工作节拍进行模拟量转换、保护逻辑处理工作,进入自治运行模式,返回步骤22。

28.优选地,步骤22中,如果同步总线上同时存在多个有效的同步信号时,则子系统仅接收id序号最小的有效同步信号;

29.在接收到有效同步信号后,子系统锁频同步信号的脉冲沿和频率,使本子系统的ad模块、cpu模块根据同步信号的节拍进行工作,保障子系统的采样、保护逻辑处理工作与发出同步信号的系统处于同步工作状态。

30.基于锁频同步的发变组保护并行处理平台,所述平台包括若干个保护处理子系统和同步总线:

31.所述保护处理子系统根据保护对象划分,且每个子系统都连接到同步总线上;

32.所述保护处理子系统,用于按序向同步总线发送同步信号及信号的有效标志,并检测接收总线上的同步信号,且在预设的延时时间内,若能接收到有效的同步信号,则子系统进入锁频同步运行模式,进行发变组保护并行处理,否则子系统进入自治运行模式。

33.本发明的有益效果在于,与现有技术相比:

34.本发明遵循锁频同步和自治均衡的原则,将发变组保护按多簇冗余并行计算的思路进行架构设计。从之前的串行处理或异步并行处理方式提升到同步并行处理方式。将发变组保护按保护对象划分为多个子系统,在系统没有发生故障时,每个子系统锁频同步运行,实现协同工作,保持子系统负载均衡,保障了整个保护系统的同步性、实时性,以及故障录波的一致性。在有子系统发生故障时,仅影响有故障的子系统,其它子系统仍然可以锁频同步运行;当其它子系统都处于故障状态或同步总线出现故障时,非故障子系统仍然可以自治运行,大幅提升了整个发变组保护系统的安全性及可靠性。

35.本发明将发变组保护平台根据保护对象的分成若干个并行处理的保护子系统,每个子系统都连接到同步总线上;子系统检测总线上的同步信号,若检测到有效的同步信号则进入锁频同步运行模式,否则将本子系统的同步信号发送到总线上;若经过预设的延时时间后总线上仍然不存在有效的同步信号,则所有子系统进入自治运行模式;在自治运行模式下,子系统实时检测总线上的同步信号,检测到有效的同步信号后立即恢复锁频同步运行模式。

附图说明

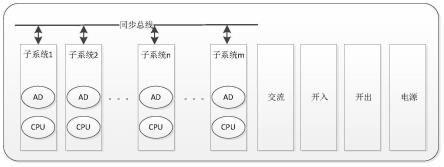

36.图1为本发明发变组并行处理平台架构示意图;

37.图2为本发明发变组保护并行处理逻辑示意图;

38.图3为本发明实施例中所用的发变组保护并行处理平台架构示意图。

具体实施方式

39.为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明的技术方案进行清楚、完整地描述。本技术所描述的实施例仅仅是本发明一部分的实施例,而不是全部实施例。基于本发明精神,本领域普通技术人员在没有作出创造性劳动前提下所获得的有所其它实施例,都属于本发明的保护范围。

40.如图1-2所示,本发明的实施例1提供了一种基于锁频同步的发变组保护并行处理方法,在本发明优选但非限制性的实施方式中,所述方法包括以下步骤:

41.步骤1:将发变组保护平台根据保护对象分成若干个保护处理子系统,每个子系统都连接到同步总线上;

42.进一步优选地,所述子系统可以为独立的物理板卡,也可以为同一物理板卡上的不同功能区域。

43.所述同步总线为多模总线smbg(smart multi-mode bus group)。

44.如图3所述,将发变组保护平台根据保护对象的不同分成发电机保护处理子系统、主变压器保护处理子系统和高厂变保护处理子系统,每个子系统都连接到同步总线上;

45.其中,每个子系统包括独立的用于模拟量转换的ad模块、用于保护逻辑处理的cpu

模块等,并可接收同步总线上的同步信号并锁定同步信号频率,亦可发送同步信号及信号的有效标志到同步总线上,用于并行冗余实时计算,并通过同步总线实时交互信息,输出统一的出口结果。

46.步骤2:子系统按序向同步总线发送同步信号及信号的有效标志,并检测接收总线上的同步信号,在预设的延时时间内,若能接收到有效的同步信号,则子系统进入锁频同步运行模式,进行发变组保护并行处理,否则子系统进入自治运行模式。

47.进一步优选地,所述预设时间为(m+1)*

△

t,其中,m为子系统的总个数,

△

t为同步信号一个最小频率周期的时间。

48.发变组保护平台上电后,每个子系统通过预先设定的身份识别标志id来确定本子系统的序号;

49.子系统发送到同步总线的同步信号中包含自身的id,以供其它子系统识别。

50.步骤2具体包括:

51.步骤21:发变组保护平台上电后,第1个子系统将同步信号及信号的有效标志发送到同步总线上;

52.根据预先设定,发电机保护处理子系统的id为1,主变压器保护处理子系统的id为2,高厂变保护处理子系统的id为3。

53.因而,发电机保护处理子系统首先将同步信号及信号的有效标志发送到总线上;

54.步骤22:所有子系统检测接收总线上的同步信号,在判断信号有效后,锁定该同步信号,ad模块、cpu模块根据同步信号的节拍进行工作,进入锁频同步运行模式;

55.进一步优选地,如果同步总线上同时存在多个有效的同步信号时,则子系统仅接收id序号最小的有效同步信号;这样做是某些异常情况下的防误措施,理论上不会有多个同步信号出现,但是为了防止子系统失控后误向总线发送同步信号,所以增加此条判断。

56.在接收到有效同步信号后,子系统锁频同步信号的脉冲沿和频率,使本子系统的ad模块、cpu模块根据同步信号的节拍进行工作,保障子系统的采样、保护逻辑处理工作与发出同步信号的系统处于同步工作状态。

57.如果总线上同时存在多个有效的同步信号时,也可以采用其它规则,只要能对同步信号源进行唯一性选择即可。

58.步骤23:若第n个子系统在等待n*

△

t时间后,仍然没有收到有效的同步信号,再将本子系统的同步信号及信号有效标志发送到同步总线上,返回步骤22;

59.其中,n为子系统的序号,m≥n≥2,m为子系统的总个数;

60.步骤23可避免多个子系统同时向总线上发送同步信号。

61.在本实施例中,如果发电机保护处理子系统出现故障,没有将同步信号发送到总线上,则主变压器保护处理子系统在2*

△

t时间后将本子系统的同步信号及信号有效标志发送到总线上;假如此时主变压器保护处理子系统也出现故障,没有将同步信号发送到总线上,则高厂变保护处理子系统在3*

△

t时间后将本系统的同步信号及信号有效标志发送到总线上。

62.步骤24:所有保护处理子系统在等待4*

△

t时间后若仍然没有收到有效的同步信号,则按照本子系统的工作节拍进行模拟量转换、保护逻辑处理等工作,进入自治运行模式,返回步骤22,即所有子系统检测接收总线上的同步信号,若检测到有效的同步信号,则

锁定同步信号并进入锁频同步运行模式,否则将本子系统的同步信号和有效标志发送到总线上。

63.步骤24实现了即使其它子系统都处于故障状态或同步总线出现故障时,本子系统仍然可以自治工作。

64.本发明的实施例2提供了一种根据上述的方法得到的基于锁频同步的发变组保护并行处理平台,包括若干个保护处理子系统和同步总线:

65.所述保护处理子系统根据保护对象划分,且每个子系统都连接到同步总线上;

66.所述保护处理子系统,用于按序向同步总线发送同步信号及信号的有效标志,并检测接收总线上的同步信号,且在预设的延时时间内,若能接收到有效的同步信号,则子系统进入锁频同步运行模式,进行发变组保护并行处理,否则子系统进入自治运行模式。

67.本发明的有益效果在于,与现有技术相比:

68.本发明遵循锁频同步和自治均衡的原则,将发变组保护按多簇冗余并行计算的思路进行架构设计。从之前的串行处理或异步并行处理方式提升到同步并行处理方式。将发变组保护按保护对象划分为多个子系统,在系统没有发生故障时,每个子系统锁频同步运行,实现协同工作,保持子系统负载均衡,保障了整个保护系统的同步性、实时性,以及故障录波的一致性。在有子系统发生故障时,仅影响有故障的子系统,其它子系统仍然可以锁频同步运行;当其它子系统都处于故障状态或同步总线出现故障时,非故障子系统仍然可以自治运行,大幅提升了整个发变组保护系统的安全性及可靠性。

69.本发明将发变组保护平台根据保护对象的分成若干个并行处理的保护子系统,每个子系统都连接到同步总线上;子系统检测总线上的同步信号,若检测到有效的同步信号则进入锁频同步运行模式,否则将本子系统的同步信号发送到总线上;若经过预设的延时时间后总线上仍然不存在有效的同步信号,则所有子系统进入自治运行模式;在自治运行模式下,子系统实时检测总线上的同步信号,检测到有效的同步信号后立即恢复锁频同步运行模式。

70.本公开可以是系统、方法和/或计算机程序产品。计算机程序产品可以包括计算机可读存储介质,其上载有用于使处理器实现本公开的各个方面的计算机可读程序指令。

71.计算机可读存储介质可以是可以保持和存储由指令执行设备使用的指令的有形设备。计算机可读存储介质例如可以是――但不限于――电存储设备、磁存储设备、光存储设备、电磁存储设备、半导体存储设备或者上述的任意合适的组合。计算机可读存储介质的更具体的例子(非穷举的列表)包括:便携式计算机盘、硬盘、随机存取存储器(ram)、只读存储器(rom)、可擦式可编程只读存储器(eprom或闪存)、静态随机存取存储器(sram)、便携式压缩盘只读存储器(cd-rom)、数字多功能盘(dvd)、记忆棒、软盘、机械编码设备、例如其上存储有指令的打孔卡或凹槽内凸起结构、以及上述的任意合适的组合。这里所使用的计算机可读存储介质不被解释为瞬时信号本身,诸如无线电波或者其它自由传播的电磁波、通过波导或其它传输媒介传播的电磁波(例如,通过光纤电缆的光脉冲)、或者通过电线传输的电信号。

72.这里所描述的计算机可读程序指令可以从计算机可读存储介质下载到各个计算/处理设备,或者通过网络、例如因特网、局域网、广域网和/或无线网下载到外部计算机或外部存储设备。网络可以包括铜传输电缆、光纤传输、无线传输、路由器、防火墙、交换机、网关

计算机和/或边缘服务器。每个计算/处理设备中的网络适配卡或者网络接口从网络接收计算机可读程序指令,并转发该计算机可读程序指令,以供存储在各个计算/处理设备中的计算机可读存储介质中。

73.用于执行本公开操作的计算机程序指令可以是汇编指令、指令集架构(isa)指令、机器指令、机器相关指令、微代码、固件指令、状态设置数据、或者以一种或多种编程语言的任意组合编写的源代码或目标代码,所述编程语言包括面向对象的编程语言—诸如smalltalk、c++等,以及常规的过程式编程语言—诸如“c”语言或类似的编程语言。计算机可读程序指令可以完全地在用户计算机上执行、部分地在用户计算机上执行、作为一个独立的软件包执行、部分在用户计算机上部分在远程计算机上执行、或者完全在远程计算机或服务器上执行。在涉及远程计算机的情形中,远程计算机可以通过任意种类的网络—包括局域网(lan)或广域网(wan)—连接到用户计算机,或者,可以连接到外部计算机(例如利用因特网服务提供商来通过因特网连接)。在一些实施例中,通过利用计算机可读程序指令的状态信息来个性化定制电子电路,例如可编程逻辑电路、现场可编程门阵列(fpga)或可编程逻辑阵列(pla),该电子电路可以执行计算机可读程序指令,从而实现本公开的各个方面。

74.这里参照根据本公开实施例的方法、装置(系统)和计算机程序产品的流程图和/或框图描述了本公开的各个方面。应当理解,流程图和/或框图的每个方框以及流程图和/或框图中各方框的组合,都可以由计算机可读程序指令实现。

75.这些计算机可读程序指令可以提供给通用计算机、专用计算机或其它可编程数据处理装置的处理器,从而生产出一种机器,使得这些指令在通过计算机或其它可编程数据处理装置的处理器执行时,产生了实现流程图和/或框图中的一个或多个方框中规定的功能/动作的装置。也可以把这些计算机可读程序指令存储在计算机可读存储介质中,这些指令使得计算机、可编程数据处理装置和/或其它设备以特定方式工作,从而,存储有指令的计算机可读介质则包括一个制造品,其包括实现流程图和/或框图中的一个或多个方框中规定的功能/动作的各个方面的指令。

76.也可以把计算机可读程序指令加载到计算机、其它可编程数据处理装置、或其它设备上,使得在计算机、其它可编程数据处理装置或其它设备上执行一系列操作步骤,以产生计算机实现的过程,从而使得在计算机、其它可编程数据处理装置、或其它设备上执行的指令实现流程图和/或框图中的一个或多个方框中规定的功能/动作。

77.附图中的流程图和框图显示了根据本公开的多个实施例的系统、方法和计算机程序产品的可能实现的体系架构、功能和操作。在这点上,流程图或框图中的每个方框可以代表一个模块、程序段或指令的一部分,所述模块、程序段或指令的一部分包含一个或多个用于实现规定的逻辑功能的可执行指令。在有些作为替换的实现中,方框中所标注的功能也可以以不同于附图中所标注的顺序发生。例如,两个连续的方框实际上可以基本并行地执行,它们有时也可以按相反的顺序执行,这依所涉及的功能而定。也要注意的是,框图和/或流程图中的每个方框、以及框图和/或流程图中的方框的组合,可以用执行规定的功能或动作的专用的基于硬件的系统来实现,或者可以用专用硬件与计算机指令的组合来实现。

78.最后应当说明的是,以上实施例仅用以说明本发明的技术方案而非对其限制,尽管参照上述实施例对本发明进行了详细的说明,所属领域的普通技术人员应当理解:依然

可以对本发明的具体实施方式进行修改或者等同替换,而未脱离本发明精神和范围的任何修改或者等同替换,其均应涵盖在本发明的权利要求保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1