一种串联拓扑结构功率模块

本发明涉及电力电子,尤其涉及采用有源箝位均压控制策略的串联拓扑结构功率模块及其结构设计。

背景技术:

1、在工业、交通、电网、国防等领域中存在大量的中高压电力变换应用场景,其电力变换系统对高耐压电力电子器件或者功率模块有着强劲的需求。基于传统硅基器件的电力变换系统在耐压和损耗上受到越来明显的制约。为了实现低损耗的高压大功率输出,新型宽禁带半导体电力电子器件的研究和开发成为了重要的发展趋势。碳化硅(siliconcarbide,sic)器件是新型宽禁带半导体器件的典型代表,具有开关速度快、损耗低的特点,在电力系统中存在广阔的应用前景。当前,1.2kv及其以下耐压等级碳化硅电力电子芯片已完全大规模商业化,其价格也比较合理,但是由于碳化硅材料和芯片工艺技术的制约,低成本的可靠的高耐压碳化硅器件仍旧遥遥无期。因此,采用低耐压低损耗碳化硅器件搭建高压功率变换系统成为了中高压电力变换降低损耗、降低成本、提升系统输出功率的最佳选择。

2、采用低耐压器件搭建高压功率变换系统有两种可能的解决方案,分别是多电平变换器方案(multilevel converter scheme)和电力电子器件串联方案(power devicesseries scheme)。以级联h桥多电平变换器(cascaded h-bridge multilevel converter,chb)和模块化多电平变换器(modular multilevel converter,mmc)为代表的多电平变换器方案具有结构模块化、高效率和高可靠性的特点,已被应用于众多中高功率应用场合。然而,多电平变换器方案通常不得不使用大尺寸的无源元件,例如,chb需要配备较大体积的移相变压器,而mmc中电容器占其子模块尺寸的70%左右,这些缺点阻碍了多电平变换器在一些对重量和体积要求严格的应用场合的使用,例如电气化运输和数据中心等。

3、电力电子器件串联方案是将低压功率器件应用于中高压应用场合的另外一种较为直接的方式。电力电子器件的串联方案提高了功率变换系统的耐压等级,增加了功率变换系统的输出功率,其相对于多电平技术方案的优点在于串联后的功率变换系统体积小、无源元件数量少、电路拓扑简单。但是由于电力电子器件的电性能参数或者外部电路条件存在差异,比如:结电容、栅极的阈值电压、栅极驱动信号延时、施加在栅极的瞬时驱动电压等,结果导致串联电力电子器件的电压极容易出现不均衡,功率变换系统的电气可靠性不高的问题。因此,实现串联器件的电压均衡(voltage balance)成为采用低耐压电力电子器件的功率变换系统进一步提升电压和电流等级的技术关键。

4、均压控制策略和串联拓扑结构功率回路的硬件优化设计是实现电力电子器件的串联均压(voltage balance of power devices in series)的两个主要技术支撑。均压控制策略存在两类技术方案,分别是输入栅极侧均压控制技术方案和输出功率侧均压控制技术方案。

5、输入栅极侧均压控制技术方案的缺点在于:电路设计和控制策略较为复杂、对高速传感器和a/d转换芯片的要求极高、对器件温度和负载电流变化也极为敏感。该技术方案不得不引入额外的电路,增加驱动回路的复杂性,因为涉及到高速控制所以均压控制电路成本较高,缺乏实际可用性。

6、输出功率侧均压控制技术方案包括无源缓冲电路(passive snubber circuit)方案和有源箝位电路(active clamp circuits)方案。无源缓冲电路方案由于借助了rc电路(resistor-capacitance circuit),实际工作中会在会在缓冲电阻(resistor,r)上产生较大的能量损失,无源元件体积大不利于集成,缓冲电容与开关管的功率回路并联导致开关管的开关速度较慢。然而,有源电压箝位电路方案通过在箝位支路引入辅助开关管,将箝位电容的中累积的能量回馈到电路中而不是像rc方案那样直接消耗掉,该方案均压电路引入的损耗小;此外,有源箝位电路只有在电力电子器件两端电压超过箝位电容两端电压时,才会起箝位作用,该方法不会降低主开关管本身的开关速度,不增加主开关的开关损耗。因此,基于有源箝位电路的均压控制策略是解决串联器件均压的一个比较理想的方案。

7、目前关于有源箝位控制策略的研究中在搭建串联拓扑结构功率回路的硬件时基本上都是基于分立器件或者常规商用功率模块来开展的,这也存在诸多的弊端,以至于在某种程度上制约了采用有源箝位控制策略的电力电子起家串联方案的大规模商用。基于分立器件的串联方案存在系统功率密度低、难以大电流运行的劣势,无法满足中高压应用的大功率需求;基于常规商用模块的串联方案虽然解决了中高压应用的大功率需求,但是商业模块功率回路电路拓扑结构与采用有源箝位控制策略的功率变换系统整体架构的不匹配也使得基于商业模块的有源箝位串联方案存在诸多局限,比如功率变换系统电压电流等级扩展不方便、功率变换系统内部功率回路线路较长导致了较大的寄生电感、功率模块主电路拓扑不合理、功率模块及其功率变换系统的功率密度不高或者动态响应较慢等。

8、鉴于此,开发适合于有源箝位控制策略的串联拓扑结构功率模块成为了有源箝位技术方案在高压大功率变换技术领域实现产业化的必经之路。为了将低耐压碳化硅器件的低损耗和低成本优势扩展到高耐压大功率应用领域,逐步取代存在诸多缺点的多电平或者输入栅极侧均压控制等技术方案,亟须研制基于串联低耐压电力电子芯片并采用有源箝位控制策略的低成本的高压大功率模块。因此,基于低耐压电子电子芯片并采用有源箝位均压控制的串联拓扑结构功率模块具有巨大的应用前景和经济价值。

技术实现思路

1、为了解决上述现有技术的一个或多个技术问题,本发明提出了一种串联拓扑结构功率模块及其结构设计。

2、根据本发明一实施例提出了一种串联拓扑结构功率模块,其特征在于,底板;第一焊料层,位于所述底板上表面;绝缘板,包括下部金属层、中间绝缘层、上部金属层,其中所述下部金属层位于所述第一焊料层上表面;第二焊料层,位于所述上部金属层上表面;功率单元,位于所述第二焊料层上表面,其包括第一dbc结构、第二dbc结构、第三dbc结构、第四dbc结构、第五dbc结构、第三焊料层、主开关管电力电子芯片、辅助开关管电力电子芯片、箝位电容、主开关管栅极信号端子、主开关管源极信号端子、辅助开关管栅极信号端子、辅助开关管源极信号端子、电压采样信号端子,其中所述第一dbc结构、第二dbc结构、第三dbc结构第四dbc结构和第五dbc结构均包括下层铜箔、中间层陶瓷和上层铜箔,所述下层铜箔位于所述第二焊料层上表面,用于实现和所述绝缘板上部金属层的连接,所述第三焊料层位于所述上层铜箔上表面,所述主开关管电力电子芯片和辅助开关管电力电子芯片均位于所述第三焊料层上表面,所述功率单元的电路拓扑结构包括串联的第一基本电路单元和第二基本电路单元,所述第一基本电路单元和第二基本电路单元均包括主开关管电力电子芯片和与之并联的有源箝位支路,所述有源箝位支路包括辅助开关管电力电子芯片和与之串联的箝位电容,所述功率单元的主支路包括第一基本电路主开关管电力电子芯片和与之串联的第二基本电路主开关管电力电子芯片;串联连接结构,位于所述第三焊料层上表面,用于实现所述功率单元的串联连接;功率电极,包括“dc+”功率电极和“dc-”功率电极;辅助结构,包括塑料框架结构、盖子、灌封料,所述灌封料填充于由所述塑料框架结构限定的所述功率模块内部;以及所述功率模块内部多个所述功率单元被依次并列在一起并通过串联连接结构实现所述第一基本电路单元和第二基本电路单元的依次串联,所述功率模块的主功率支路由所述功率单元主支路串联而成。

3、根据本发明又一实施例提出了一种串联拓扑结构功率模块,其包括:功率单元,其包括第一dbc结构、第二dbc结构、第三dbc结构、第四dbc结构、第五dbc结构、第三焊料层、主开关管电力电子芯片、辅助开关管电力电子芯片、箝位电容、主开关管栅极信号端子、主开关管源极信号端子、辅助开关管栅极信号端子、辅助开关管源极信号端子、电压采样信号端子,其中所述第一dbc结构、第二dbc结构、第三dbc结构第四dbc结构和第五dbc结构均包括下层铜箔、中间层陶瓷和上层铜箔,所述下层铜箔位于所述第二焊料层上表面,用于实现和所述绝缘板上部金属层的连接,所述第三焊料层位于所述上层铜箔上表面,所述主开关管电力电子芯片和辅助开关管电力电子芯片均位于所述第三焊料层上表面,所述功率单元的电路拓扑结构包括串联的第一基本电路单元和第二基本电路单元,所述第一基本电路单元和第二基本电路单元均包括主开关管电力电子芯片和与之并联的有源箝位支路,所述有源箝位支路包括辅助开关管电力电子芯片和与之串联的箝位电容,所述功率单元的主支路包括第一基本电路主开关管电力电子芯片和与之串联的第二基本电路主开关管电力电子芯片;串联连接结构,位于所述第三焊料层上表面,用于实现所述功率单元的串联连接;功率电极,包括“dc+”功率电极和“dc-”功率电极;以及所述功率模块内部多个所述功率单元被依次并列在一起并通过串联连接结构实现所述第一基本电路单元和第二基本电路单元的依次串联,所述功率模块的主功率支路由所述功率单元主支路串联而成;

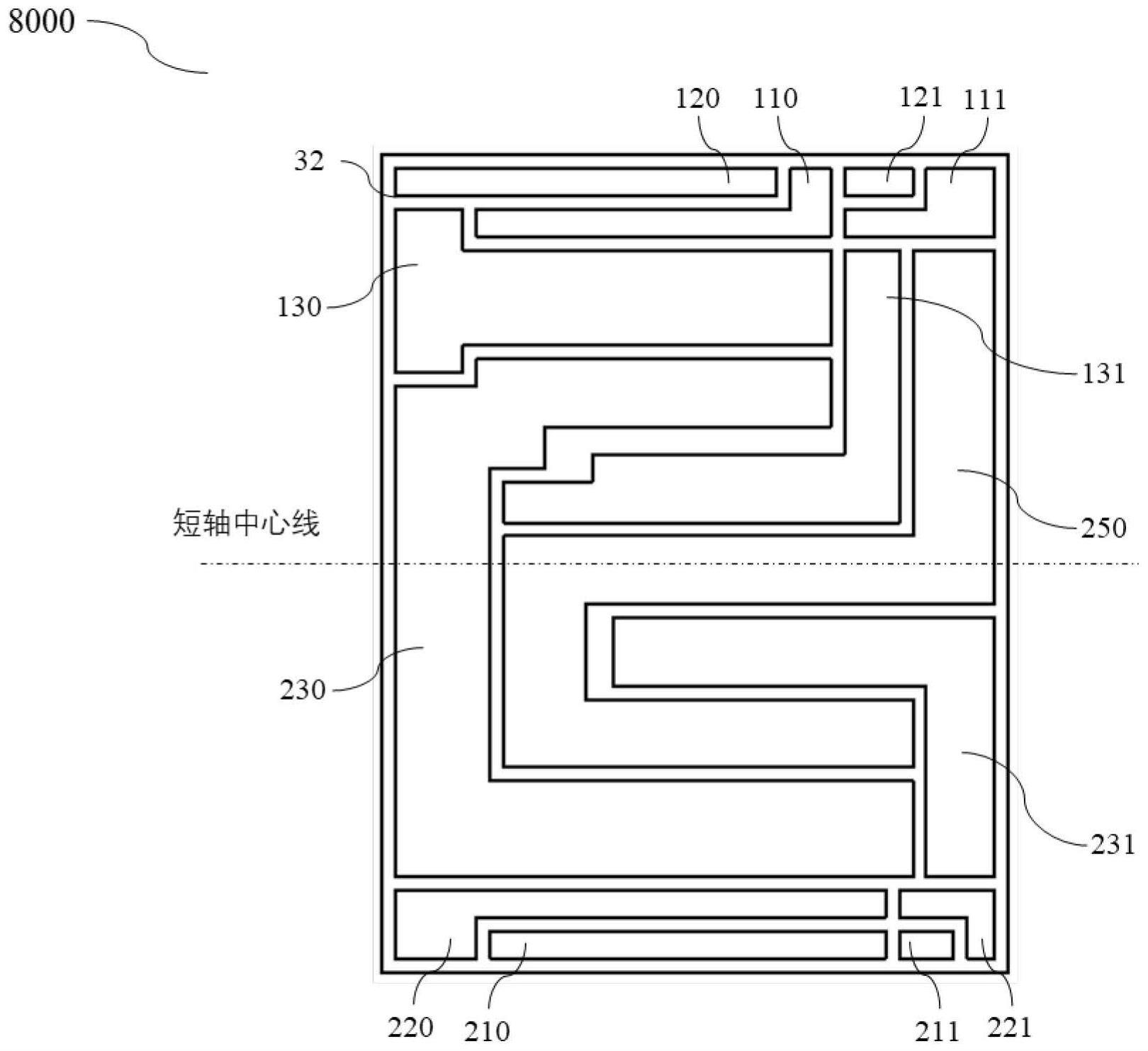

4、进一步地,所述的功率模块中并列的多个所述功率单元的短轴中心线均平行于所述功率模块的长轴中心线,连接所述功率单元的所述串联连接结构均位于所述功率模块的长轴中心线的同一侧;

5、进一步地,所述的功率单元中的所述第一基本电路单元中:主开关管栅极信号端子和源极信号端子被布局在第二dbc结构上、辅助开关管栅极信号端子和源极信号端子被布局在第三dbc结构上,第一基本电路单元中的这些信号端子在水平面投影后的连线为第一信号端子横线;所述第二基本电路单元中:主开关管栅极信号端子和源极信号端子被布局在第四dbc结构上,辅助开关管栅极信号端子和源极信号端子被布局在第五dbc结构上,第二基本电路单元中的这些信号端子在水平面投影后的连线为第二信号端子横线,所述第一信号端子横线和所述第二信号端子横线均平行于所述功率单元的短轴中心线且分别位于所述功率单元的两外侧边区域;所述第一基本电路单元和所述第二基本电路单元中的主开关管电力电子芯片、辅助开关管电力电子芯片、箝位电容及箝位电容的电压采样端子均被布局在第一dbc结构上,所述第一dbc结构位于所述功率单元的中间区域,且所述第一基本电路单元的源极与所述第二基本电路单元的漏极通过所述第一dbc结构的上层铜箔实现电气互连;

6、进一步地,所述功率单元的串联数为n且n为大于等于2的自然数,且所述功率单元中所述主开关管电力电子芯片或者辅助开关管电力电子芯片也可相应的反并联续流二极管芯片,所述反并联是指所述续流二极管芯片的阴极与所述电力电子芯片的漏极相连,所述续流二极管芯片的阳极与所述电力电子芯片的源极相连;

7、进一步地,所述第一dbc结构中所述第一基本电路单元的主开关管电力电子芯片栅-源极路径的源极条和栅极条、辅助开关管电力电子芯片栅-源极路径的源极条和栅极条位于所述第一dbc结构的一短外侧边区域,所述第二基本电路单元的主开关管电力电子芯片栅-源极路径的源极条和栅极条、辅助开关管电力电子芯片栅-源极路径的源极条和栅极条位于所述第一dbc结构的另外一短外侧边区域;由短外侧边向所述功率单元的第一dbc结构短轴中心线的方向,紧挨着第一基本电路单元的主开关管电力电子芯片栅-源极路径的源极条和栅极条的区域为布局第一基本电路单元的主开关管电力电子芯片的区域,紧挨着第一基本电路单元的辅助开关管电力电子芯片栅-源极路径的源极条和栅极条为布局第一基本电路单元的辅助开关管电力电子芯片的区域且该区域呈“l”形,同样的,紧挨着第二基本电路单元的主开关管电力电子芯片栅-源极路径的源极条和栅极条的区域为布局第二基本电路单元主开关管电力电子芯片的区域,紧挨着第二基本电路单元的辅助开关管电力电子芯片栅-源极路径的源极条和栅极条为布局第二基本电路单元辅助开关管电力电子芯片的区域且该区域也呈“l”形;布局所述第一基本电路单元的主开关管电力电子芯片源极的区域和布局所述第二基本电路单元的主开关管电力电子芯片的区域整体组成一个“匚”形的大区域且位于所述第一dbc结构的中心区域的长侧边附近,其中所述“匚”形的上部横边被嵌套于第一基本电路单元的主开关管电力电子芯片布局区域和第一基本电路单元辅助开关管电力电子芯片布局区域之间,所述“匚”形的下部横边区域为所述第二基本电路单元的主开关管电力电子芯片的布局区域,且该区域位于第二基本电路单元的主开关管电力电子芯片栅-源极路径布局区域和第二基本电路单元的源极布局区域之间;布局所述第二基本电路单元的源极的区域整体呈倒置的“ㄕ”形,倒置后的“ㄕ”形下横边位于所述“匚”形下部横边和布局第二基本电路单元辅助管电力电子芯片的“l”形区域之间;

8、进一步地,所述第一dbc结构上层铜箔中布局所述第二基本电路单元的箝位电容的低电压引脚的区域、布局采样箝位电容低电位电压的电容电压采样端子的区域和布局第二基本电路单元的源极的区域为一单一的第一连通区域,该单一的第一连通区域为所述的“ㄕ”形区域且在所述功率单元的电路拓扑上以低电压电位为特征;所述第一dbc结构的上层铜箔中布局第二基本电路单元的主开关管电力电子芯片的区域、布局第一基本电路单元的箝位电容的低电位电压引脚的区域、布局第一基本电路单元的采样箝位电容低电位电压的电容电压采样端子的区域和布局第一基本电路单元的主开关管电力电子芯片源极的区域为一单一的第二连通区域,该单一的第二连通区域为所述的“匚”形区域,所述“匚”形区域被用于实现所述第一基本电路单元的源极和所述第二基本电路单元的漏极的主功率回路的电气连接;所述倒置的“ㄕ”形区域被设置于所述“匚”形内部的中心区域,在所述“ㄕ”形区域与所述“匚”形区域之间又嵌套了两个所述“l”形区域,倒置后的所述“ㄕ”形的竖直边被用于实现与并列的所述功率单元的串联连接;

9、进一步地,所述的功率模块中串联所述功率单元的起点和终点分别为“dc+”功率电极和“dc-”功率电极,其中“dc+”功率电极与功率模块内部并列的第一个功率单元的第一基本电路单元连接而“dc-”功率电极与功率模块内部并列的最后一个功率单元的第二基本电路单元连接,所述功率单元的主支路在所述功率模块的水平面的投影整体呈“s”形,所述功率模块的主功率支路在功率模块的水平面的投影为多个“s”形支路的串联,串联的多个所述“s”形支路对称的分布于所述功率模块的长轴中心线上。

10、相比现有技术方案,本发明公开的一种串联拓扑结构功率模块及其结构设计的有益效果在于:提出的将第一基本电路单元和第二基本电路单元串联在一起组成功率单元的设计保持功率模块耐压不变的前提下大幅降低功率模块在功率单元串联方向上的长度尺寸;提出的将高压主支路与有源箝位支路布局于功率单元内部中心区域而将电力电子芯片的低压的栅极信号端子和源极信号端子布局于功率单元外侧边区域的设计分隔了功率单元内部的高电场区域和低电场区域,从而提升功率模块的电气可靠性;提出的将功率模块主功率回路整体布局成多个“s”形支路串联的串联技术方案缩减了功率模块的长度,降低模块制作中热应力引起的形变,提升模块制作的可靠性,而且“s”形支路中因为存在相互平行且紧挨在一起的电流方向彼此相反的电流路径,所以模块主功率回路虽然长度增加但是其寄生电感却被减小了。

- 还没有人留言评论。精彩留言会获得点赞!