驱动电路的制作方法

1.本实用新型涉及一种驱动电路。

背景技术:

2.进行高电压、大电流的通断的绝缘栅双极晶体管(insulated gate bipolartransistor,igbt)在因连接的负载的短路等导致过电流流通而损坏时,会对周边设备造成很大的阻碍,因此需要极力避免损坏。因此,在驱动igbt的驱动电路中,防备此种情况以保护igbt的功能变得重要。作为检测因负载的短路等导致过电流流通的异常的方法,有检测igbt为导通(on)状态下的vce(集电极-发射极间电压)的上升值的方法。在所述现有方法中,有时会在异常检测之后设置一定的期间直至发送异常检测信号为止。所述一定期间是保持等待异常检测信号的发送的时间,被称为屏蔽时间。就防止误检测以及防止igbt的过负载的观点而言,屏蔽时间被要求一定的精度。

3.图11是基于现有技术的栅极驱动器900驱动igbt 912的驱动电路的电路图。如图11所示,栅极驱动器900包括反相器916、比较器918、晶体管 q901及电流源idesat。向电流源idesat供给电压vdd。另外,在栅极驱动器 900连接有电容器cdesat、缓冲电路920、二极管ddesat及igbt 912。此外,向比较器918的输入端的一端输入基准电压vdesatth。另外,从栅极驱动器 900的输出(out)端子914输入高电平(vgatehigh,vgh)与低电平(vgatelow, vgl)交替的脉冲信号。

4.此处,对igbt 912正常地重复进行导通动作与关断动作时的动作进行说明。在igbt 912进行关断动作的期间,out端子914的输出值为低电平,栅极驱动器900的晶体管q901进行导通动作,将电容器cdesat的电荷放电为0。当igbt 912变为导通动作时,out端子914的值为高电平,因此,经由反相器916向晶体管q901的基极输入低电平的信号。结果,虽然晶体管 q901变为关断动作,但由于igbt 912的vce电压成为饱和电压,因此电流源idesat的电流经由二极管ddesat流向igbt 912的集电极端子。

5.结果,电容器cdesat被充电至将基于电流源idesat的二极管ddesat的正向电压与igbt 912的集电极-发射极间的饱和电压相加后的电压。即,电容器cdesat的端子间电压成为所述饱和电压+二极管ddesat的正向电压。由于栅极驱动器900的短路时间限定(definition of the short-circuit time,desat) 端子的电压维持比基准电压vdesatth低的电压,因此比较器918不使其输出信号的值反转,因此不输出异常检测信号。

6.在与igbt 912连接的负载发生异常而在igbt 912中流通过电流且vce 电压上升而达到正极侧电源vcc电平的情况下,二极管ddesat变为切断(cutoff)状态。然后,电流源idesat的电流流入电容器cdesat,电容器cdesat的端子间电压上升而达到基准电压vdesatth。结果,比较器918使输出的值反转而输出异常检测信号。此外,在电容器cdesat的端子间电压高于基准电压 vdesatth时,比较器918的输出信号变为高电平,其表示异常检测信号。另外,设定了从与igbt 912连接的负载发生异常开始至栅极驱动器900输出异常检测信号为止的屏蔽时间tw。此外,栅极驱动器900将所述异常检测信号输出至外部装置(未

图示)。外部装置基于所输入的异常检测信号,将igbt 912 的栅极的信号切换为低电平。关于屏蔽时间tw,在与igbt 912连接的负载在短路时电感小而为约200(nh)的情况下,为约6.9(μs),在负载在短路时电感大而为约8(nh)的情况下,为约1.0(μs)。此外,在负载短路的情况下,二极管ddesat为开路状态,来自desat端子的信号流向电容器cdesat。

7.[现有技术文献]

[0008]

[专利文献]

[0009]

[专利文献1]日本专利特开2004-140891号公报

技术实现要素:

[0010]

[实用新型所要解决的问题]

[0011]

在所述那样的现有驱动电路中,存在出于防止误检测的目的的屏蔽时间根据短路时的负载条件而变化的课题。

[0012]

本实用新型是鉴于所述问题点而成,其目的在于提供一种可提高屏蔽时间的精度的驱动电路。

[0013]

[解决问题的技术手段]

[0014]

(1)为了达成所述目的,本实用新型的一实施方式的驱动电路为利用脉冲信号驱动开关元件41的驱动电路,其包括:第一二极管d22;第一晶体管 q21以及第二晶体管q22,在所述第一二极管为关断状态时成为关断状态,在所述第一二极管为导通状态时成为导通状态;第一电容器(cdesat);以及控制部30,控制是否向所述开关元件输出所述脉冲信号;在所述开关元件为接通(turn on)状态的情况且所述开关元件的集电极-发射极间电压为第一规定电压值以上的情况下,所述第一二极管成为导通状态,所述第一晶体管以及所述第二晶体管成为导通状态,在开始对所述第一电容器进行来自电流源的电流的充电且两端的电压值成为大于所述第一规定电压值的第二规定电压值以上的屏蔽时间后,将异常检测信号输出至所述控制部,所述控制部根据所述异常检测信号停止向所述开关元件输出所述脉冲信号。

[0015]

(2)为了达成所述目的,本实用新型的一实施方式的驱动电路为利用脉冲信号驱动开关元件41的驱动电路,其包括:第一二极管d22;第一晶体管 q23;第二晶体管q22c;第一电容器(cdesat);以及控制部30,控制是否向所述开关元件输出所述脉冲信号;在所述开关元件为接通状态的情况且所述开关元件的集电极-发射极间电压为第一规定电压值以上的情况下,所述第一二极管成为导通状态,所述第一晶体管成为关断状态,所述第二晶体管成为导通状态,在开始对所述第一电容器进行来自电流源的电流的充电且两端的电压值成为大于所述第一规定电压值的第二规定电压值以上的屏蔽时间后,将异常检测信号输出至所述控制部,所述控制部根据所述异常检测信号停止向所述开关元件输出所述脉冲信号。

[0016]

(3)另外,在本实用新型的一实施方式的驱动电路中,可为:在所述开关元件为接通状态的情况且所述开关元件的集电极-发射极间电压小于所述第一规定电压值的情况下,所述第一二极管成为关断状态,所述第一晶体管以及所述第二晶体管成为关断状态,在来自电流源的电流的两端的电压值达到与所述第一规定电压值以及第二规定电压值不同的第三规定电压值的屏蔽时间后,将所述异常检测信号输出至所述控制部。

[0017]

(4)另外,在本实用新型的一实施方式的驱动电路中,可为:在所述开关元件为接

通状态的情况且所述开关元件的集电极-发射极间电压小于所述第一规定电压值的情况下,所述第一二极管以及所述第二晶体管成为关断状态,所述第一晶体管成为导通状态,在来自电流源的电流的两端的电压值达到与所述第一规定电压值以及所述第二规定电压值不同的第三规定电压值的屏蔽时间后,将所述异常检测信号输出至所述控制部。

[0018]

(5)另外,在本实用新型的一实施方式的驱动电路中,可为:所述第一晶体管q21的基极与第二电阻r202的一端以及第三电阻r203的一端连接,所述第三电阻的另一端与所述第二晶体管q22的集电极连接,所述第二晶体管的发射极接地,且基极与第四电阻r204的一端以及第五电阻r205的一端连接,所述第四电阻的另一端接地,所述第五电阻的另一端与所述第一二极管d22的阳极连接,所述第一二极管的阴极与第六电阻r206的一端以及第二二极管(ddesat)的阳极连接,所述第六电阻的另一端与第三二极管d23 的阴极、所述第一晶体管的发射极以及所述第二电阻的另一端连接,所述第二二极管的阴极与所述开关元件的集电极连接,所述第三二极管中,向阳极输入所述脉冲信号,所述第一电容器(cdesat)的一端与电流源(idesat)以及第四二极管d21的阳极连接,且另一端接地,所述第四二极管的阴极与第一电阻r201的一端以及所述第一晶体管的集电极连接,所述第一电阻的另一端接地。

[0019]

(6)另外,在本实用新型的一实施方式的驱动电路中,可为:所述第一晶体管q21的基极与第二电阻r202的一端以及第三电阻r203的一端连接,且发射极与正电压(vcc1)连接,所述第二电阻的另一端与所述正电压连接,所述第三电阻的另一端与所述第二晶体管q22的集电极连接,所述第二晶体管的发射极接地,且基极与第四电阻r204的一端以及第五电阻r205的一端连接,所述第四电阻的另一端接地,所述第五电阻的另一端与所述第一二极管d22的阳极连接,所述第一二极管的阴极与第六电阻r206的一端以及第二二极管(ddesat)的阳极连接,所述第六电阻的另一端与所述正电压连接,所述第二二极管的阴极与所述开关元件41的集电极连接,所述第一电容器 (cdesat)的一端与电流源(idesat)以及第三二极管d23的阳极连接,且另一端接地,所述第三二极管的阴极与第一电阻r201的一端以及所述第一晶体管的集电极连接,所述第一电阻的另一端接地。

[0020]

(7)另外,在本实用新型的一实施方式的驱动电路中,可为:所述第一电容器(cdesat)的一端与电流源(idesat)以及第一电阻r211连接,且另一端接地,所述第一电阻的另一端与所述第一晶体管q23的集电极连接,所述第一晶体管的发射极接地,且基极与第二电阻r212的一端以及第三电阻 r213的一端连接,所述第三电阻的另一端接地,所述第二晶体管q22c的发射极接地,且基极与第四电阻r204的一端以及第五电阻r205的一端连接,所述第四电阻的另一端接地,所述第五电阻的另一端与所述第一二极管d22 的阳极连接,所述第一二极管的阴极与第六电阻r206的一端以及第二二极管 (ddesat)的阳极连接,所述第六电阻的另一端与第三二极管d23的阴极以及第七电阻r217的一端连接,所述第七电阻的另一端与所述第二电阻的另一端以及所述第二晶体管的集电极连接,所述第二二极管的阴极与所述开关元件的集电极连接,所述第三二极管中,向阳极输入所述脉冲信号。

[0021]

(8)另外,在本实用新型的一实施方式的驱动电路中,可为:所述第一电容器(cdesat)的一端与电流源(idesat)以及第一电阻r211的一端连接,且另一端接地,所述第一电阻的另一端与所述第一晶体管q23的集电极连接,所述第一晶体管的发射极接地,且基极与第二电阻r212的一端以及第三电阻 r213的一端连接,所述第三电阻的另一端接地,所

述第二晶体管q22c的发射极接地,且基极与第四电阻r204的一端以及第五电阻r205的一端连接,所述第四电阻的另一端接地,所述第五电阻的另一端与所述第一二极管d22 的阳极连接,所述第一二极管的阴极与第六电阻r206d的一端以及第二二极管(ddesat)的阳极连接,所述第六电阻的另一端与正电压(vcc1)连接,第七电阻r217d的一端与所述正电压连接,且另一端与所述第二电阻的另一端以及所述第二晶体管的集电极连接,所述第二二极管的阴极与所述开关元件41的集电极连接。

[0022]

[实用新型的效果]

[0023]

根据本实用新型,可提高屏蔽时间的精度。

附图说明

[0024]

图1是实施方式的驱动电路的电路图。

[0025]

图2是表示实施方式的驱动电路的动作例的图。

[0026]

图3是第一实施例的驱动电路的电路图。

[0027]

图4是第二实施例的驱动电路的电路图。

[0028]

图5是表示第一实施例以及第二实施例中在短路时负载的电感值小的情况下的模拟波形的图。

[0029]

图6是表示第一实施例以及第二实施例中在短路时负载的电感值大的情况下的模拟波形的图。

[0030]

图7是第三实施例的驱动电路的电路图。

[0031]

图8是第四实施例的驱动电路的电路图。

[0032]

图9是表示第三实施例以及第四实施例中在短路时负载的电感值小的情况下的模拟波形的图。

[0033]

图10是表示第三实施例以及第四实施例中在短路时负载的电感值大的情况下的模拟波形的图。

[0034]

图11是基于现有技术的栅极驱动器驱动igbt的驱动电路的电路图。

[0035]

[符号的说明]

[0036]

1、1a、1b、1c、1d:驱动电路

[0037]

10:驱动器

[0038]

20、20a、20b、20c、20d:desat电路

[0039]

q11、q21、q22、q21b、q22c:晶体管

[0040]

12:比较器

[0041]

13:反相器

[0042]

14:输出端子

[0043]

idesat:电流源

[0044]

cdesat、c21:电容器

[0045]

d21、d22、d23、ddesat:二极管

[0046]

r201、r202、r203、r204、r206d:电阻

[0047]

30:控制部

[0048]

31:缓冲器

[0049]

41:开关元件

具体实施方式

[0050]

以下,参照附图对本实用新型的实施方式进行说明。

[0051]

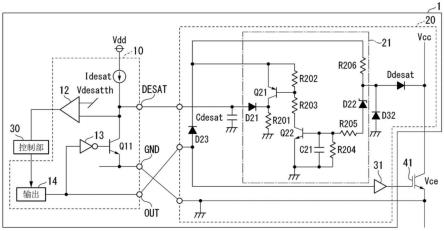

图1是本实施方式的驱动电路的电路图。如图1所示,驱动电路1包括驱动器10、短路时间限定(definition of the short-circuit time,desat)电路 20及控制部30。

[0052]

驱动器10包括晶体管q11、比较器12、反相器13、输出端子14、电流源idesat、desat端子、out端子、及接地(ground,gnd)端子。

[0053]

desat电路20包括电容器cdesat(第一电容器)、二极管d21(第四二极管)、晶体管q21(第一晶体管)、电阻r201(第一电阻)、电阻r202(第二电阻)、电阻r203(第三电阻)、晶体管q22(第二晶体管)、电容器c21、电阻r204(第四电阻)、电阻r205(第五电阻)、二极管d22(第一二极管)、二极管d23(第三二极管)、电阻r206(第六电阻)、缓冲器31、二极管d32 及二极管ddesat(第二二极管)。电路块21包括二极管d21、晶体管q21、电阻r201、电阻r202、电阻r203、晶体管q22、电容器c21、电阻r204、电阻r205、二极管d22、电阻r206。此外,对电路块21将后述。

[0054]

此外,图1所示的电路的结构是一例,驱动电路1也可包括其他零件(例如噪声去除用电容器等)。

[0055]

驱动电路1驱动开关元件41。开关元件41例如是igbt。此外,开关元件41可为其他的功率半导体(例如,金属氧化物半导体场效应晶体管 (metal-oxide-semiconductor field-effect transistor,mosfet))等。

[0056]

驱动器10是驱动开关元件41的、例如驱动集成电路(integrated circuit, ic)。另外,在与开关元件41连接的负载发生了异常的情况下,驱动器10在后述的屏蔽时间后将异常检测信号输出至控制部30。然后,驱动器10根据控制部30的控制将开关元件41的栅极电平切换为低电平。

[0057]

desat电路20是在因负载的短路等导致流通过电流时基于开关元件41 的例如集电极-发射极间的电压的上升而将栅极切断的保护电路。

[0058]

控制部30控制是否向开关元件41输出脉冲信号。控制部30在从驱动器 10获取了异常检测信号的情况下对驱动器10进行控制,以将开关元件41的栅极电平切换为低电平。此外,驱动器10可包括控制部30。

[0059]

接着,对驱动电路1的连接关系进行说明。首先,对驱动器10的连接关系进行说明。

[0060]

比较器12中,在第一输入端子连接有基准电压vdesatth(第二规定电压值),并在第二输入端子连接有电流源idesat、desat端子以及晶体管q11 的集电极。此外,向电流源idesat供给电压vdd。晶体管q11的发射极与gnd 端子连接,且基极与反相器13的输出端子连接。反相器13的输入端子与输出端子14以及out端子连接。从输出端子14输入高电平(vgh)与低电平(vgl)交替的脉冲信号。晶体管q11是负正负(negative-positive-negative, npn)型晶体管。

[0061]

此外,从电流源idesat输出的电流值例如为数百(μa),基准电压vdesatth 的电压值例如为数(v)。另外,关于从驱动器10的out端子输出的电压值,例如vgl为0(v),vgh为十几(v)。

[0062]

接着,对desat电路20的连接关系进行说明。

[0063]

电容器cdesat的一端与驱动器10的desat端子(电流源)以及二极管 d21的阳极连接,且另一端接地。二极管d21的阴极与电阻r201的一端以及晶体管q21的集电极连接。电阻r201的另一端接地。二极管d23的阳极与驱动器10的out端子以及缓冲器31的输入端子连接。晶体管q21的发射极与电阻r202的一端、二极管d23的阴极以及电阻r206的一端连接,且基极与电阻r202的另一端以及电阻r203的一端连接。电阻r203的另一端与晶体管q22的集电极连接。

[0064]

晶体管q22的发射极接地,且基极与电容器c21的一端、电阻r204的一端以及电阻r205的一端连接。电容器c21的另一端以及电阻r204的另一端接地。电阻r205的另一端与二极管d22的阳极连接。二极管d22的阴极与二极管d32的阴极、二极管ddesat的阳极以及电阻r206的另一端连接。二极管d32的阳极接地。二极管ddesat的阴极与开关元件41的集电极连接。

[0065]

二极管d22例如是齐纳二极管(zener diode)。晶体管q21是正负正 (positive-negative-positive,pnp)型晶体管。晶体管q22是npn型晶体管。二极管ddesat例如可为包含多个二极管的二极管阵列,或者也可多个二极管串联连接。

[0066]

此外,二极管ddesat的正向电压vf的电压值例如为约1.5(v),二极管d22的齐纳电压的电压值例如为十几(v)。

[0067]

开关元件41的栅极与缓冲器31的输出端子连接,向集电极供给电源vcc,且发射极接地。此外,电源vcc的电压值例如为数百(v)。

[0068]

此外,如图11所示,现有的desat电路中,desat端子与电容器cdesat 的一端、二极管ddesat的阳极直接连接。

[0069]

接着,对驱动电路1的动作进行说明。

[0070]

图2是表示本实施方式的驱动电路的动作例的图。

[0071]

二极管d22基于两端的电压作为开关元件进行动作。电阻r202以及电阻r203作为施加至晶体管q21的基极的电压的分压电路而进行动作。电阻 r204以及电阻r205作为施加至晶体管q22的基极的电压的分压电路而进行动作。电阻r201具有以不超过驱动器10的基准电压vdesatth的电平来抑制电压的作用。电阻r206具有控制电流以使其不会过度流动的作用。晶体管 q21以及晶体管q22控制对电容器cdesat的充放电。电容器c21用于去除噪声。

[0072]

在开关元件41断开(关断控制)的期间、即来自驱动器10的out端子的输出为低电平(vgl)的期间,由于缓冲器31的输出为低电平,因此开关元件41为关断状态,开关元件41的集电极电压成为高电压。因此,在此期间,desat电路20中,二极管d22为关断状态,晶体管q21以及晶体管q22为关断状态。然后,驱动器10使电流从电流源idesat向晶体管q11流动,而不从desat端子输出至desat电路20。由此,电容器cdesat两端的电压值为约0(v)(线g11)。此外,在开关元件41断开(关断控制)的期间,驱动器10的晶体管q11是导通状态。

[0073]

如此,在本实施方式中,在开关元件41接通且vce小于第一规定电压值而为正常的情况下,二极管d22成为关断状态,晶体管q21成为关断状态,由此使desat端子为0(v)。此外,在开关元件41接通且vce小于第一规定电压值而为正常的情况下,驱动器10的晶体管q11是关断状态。结果,根据本实施方式,将电容器cdesat的初始电压固定为0(v)。由此,根据本实施方式,可控制决定时间常数的电容器cdesat的初始电荷,减少屏蔽时间的变动。

[0074]

在开关元件41接通(导通控制)的期间、即来自驱动器10的out端子的输出为高电平(vgh)的期间,由于缓冲器31的输出为高电平,因此开关元件41为导通状态。另外,在此期间,向晶体管q21的发射极以及电阻r202 施加电压,经由二极管d23向电阻r206施加电压。在此期间,在开关元件 41的vce小于第一规定电压值而为正常的情况下,desat电路20中,二极管d22为关断状态,晶体管q21以及晶体管q22为关断状态。由此,驱动器 10将从电流源idesat供给的电流输出至desat端子。然后,从驱动器10的 desat端子输出的电流被充电至desat电路20的电容器cdesat,直至下式 (1)的第三规定电压值为止(线g12)。

[0075]

[数式1]

[0076]

cdesat充电电压=d21_vf+(idesat

×

r201)...(1)

[0077]

此外,在式(1)中,d21_vf是二极管d21的正向电压vf,idesat是电流源idesat的电流值,r201是电阻r201的电阻值。

[0078]

在开关元件41接通的期间、且开关元件41的vce异常上升至第一规定电压值以上的情况下,desat电路20中,由于二极管ddesat的阳极侧的电压上升,因此二极管d22成为导通状态,晶体管q21以及晶体管q22成为导通状态。通过晶体管q21成为导通状态,二极管d21成为关断状态。然后,电容器cdesat开始进行从驱动器10的desat端子输出的电流的充电,当达到基准电压vdesatth(第二规定电压值)以上时,停止充电动作(线g13)。此外,在开关元件41接通且vce异常上升至第一规定电压值以上的情况下,驱动器10的晶体管q11为关断状态。然后,在电容器cdesat达到第三规定电压值的屏蔽时间tw后,驱动器10向控制部30输出异常检测信号,并根据控制部30的控制将开关元件41的栅极电平切换为低电平。此外,屏蔽时间tw由下式(2)决定。另外,第二规定电压值比第三规定电压值大。另外,第一规定电压值是基于开关元件41的特性的电压值。

[0079]

[数式2]

[0080][0081]

此外,在式(2)中,vdesatth是基准电压值,d21_vf是二极管d21正向电压vf,idesat是电流源idesat的电流值,r201是电阻r201的电阻值。

[0082]

如式(2)所示,根据本实施方式,可实现一定的屏蔽时间tw。另外,在本实施方式中,可根据二极管d21的正向电压vf以及电阻r201的电阻值来任意地选择屏蔽时间。因此,也能够使对于噪声等的误检测界限(margin) 更大。由此,根据本实施方式,能够使从与开关元件41连接的负载发生异常起至驱动器10输出异常检测信号为止的屏蔽时间tw一定。

[0083]

此处,对二极管d21的作用进行说明。

[0084]

在图1中,当晶体管q21成为导通状态时,有时二极管d21的阴极侧的电压会变高。在此情况下,二极管d21的阴极侧的电压有可能会超过驱动器 10的desat端子的耐压。如此,二极管d21是用于保护驱动器10的desat 端子。此外,在驱动器10的desat端子的耐压高的情况下,desat电路 20也可不包括二极管d21。

[0085]

根据以上的结构,在本实施方式中,通过简单的电路结构,可提高屏蔽时间的精度。此外,关于模拟结果将后述。

[0086]

《第一实施例》

[0087]

接着,对第一实施例进行说明。图3是第一实施例的驱动电路的电路图。如图3所

示,驱动电路1a包括驱动器10及desat电路20a。

[0088]

desat电路20a包括电容器cdesat(第一电容器)、二极管d21(第四二极管)、晶体管q21(第一晶体管)、电阻r201(第一电阻)、电阻r202(第二电阻)、电阻r203(第三电阻)、晶体管q22(第二晶体管)、电阻r204(第四电阻)、电阻r205(第五电阻)、二极管d22(第一二极管)、二极管d23 (第三二极管)、电阻r206(第六电阻)、缓冲器31及二极管ddesat(第二二极管)。

[0089]

表g501

[0090][0091]

图3的驱动电路1a的动作如表g501所示与图1的驱动电路1相同。

[0092]

如图1以及图3所示,desat电路20a不包括desat电路20所包括的电容器c21。如此,desat电路20也可不包括电容器c21。另外,在图3 中将二极管ddesat由一个二极管表示,但二极管ddesat也可包含多个二极管。

[0093]

《第二实施例》

[0094]

接着,对第二实施例进行说明。图4是第二实施例的驱动电路的电路图。如图4所示,驱动电路1b包括驱动器10及desat电路20b。

[0095]

desat电路20b包括电容器cdesat(第一电容器)、二极管d21(第四二极管)、晶体管q21b(第一晶体管)、电阻r201(第一电阻)、电阻r202b (第二电阻)、电阻r203(第三电阻)、晶体管q22(第二晶体管)、电阻r204 (第四电阻)、电阻r205(第五电阻)、二极管d22(第一二极管)、电阻r206b (第六电阻)、缓冲器31及二极管ddesat(第二二极管)。

[0096]

如图4所示,相对于图3而言desat电路20b不包括二极管d23,而在晶体管q21b的发射极以及电阻r202b、电阻r206b连接有正电压vcc1。此外,正电压vcc1的电压值例如为十几(v)。

[0097]

第一实施例的desat电路20a在脉冲信号为高电平的期间向晶体管q21 的发射极、电阻r202以及电阻r206施加电压,但在第二实施例的desat 电路20b中,不论脉冲信号的电平如何均向晶体管q21的发射极、电阻r202b 以及电阻r206b供给电压。

[0098]

表g502

[0099][0100]

如表g502所示,在开关元件41断开的情况下,第二实施例的desat电路20b中,二极管d22为导通状态,晶体管q21b以及晶体管q22为导通状态,驱动器10的晶体管q11为导通状

态。

[0101]

如表g502所示,在开关元件41接通且vce小于第一规定电压值而为正常的情况下,第二实施例的desat电路20b中,二极管d22为关断状态,晶体管q21b以及晶体管q22为关断状态,驱动器10的晶体管q11为关断状态。而且,从驱动器10的desat端子输出的电流被充电至desat电路 20b的电容器cdesat,直至式(1)的第三规定电压值为止。

[0102]

如表g502所示,在开关元件41接通且vce异常上升至第一规定电压值以上的情况下,desat电路20b中,二极管d22成为导通状态,晶体管q21b 以及晶体管q22成为导通状态,驱动器10的晶体管q11为关断状态。然后,电容器cdesat开始从驱动器10的desat端子输出的电流的充电,当达到基准电压vdesatth(第二规定电压值)以上时,停止充电动作。然后,在电容器cdesat达到第三规定电压值的屏蔽时间tw后,驱动器10向控制部30输出异常检测信号,并根据控制部30的控制将开关元件41的栅极电平切换为低电平。此外,屏蔽时间tw由式(2)决定。

[0103]

接着,关于第一实施例以及第二实施例的结构,来说明波形的模拟结果例。

[0104]

图5是表示第一实施例以及第二实施例中在短路时负载的电感值小的情况下的模拟波形的图。在图5中,横轴是时刻(μs),纵轴是电压值(v)以及电流值(a)。波形g101是流经开关元件41的集电极的电流ic的波形。波形g102是开关元件41的栅极电压vge的波形。波形g103是desat端子的 vdesat电压的波形。波形g104是开关元件41的集电极-发射极间电压vce 的波形。此外,减饱和(desaturation)状态是指开关元件41为不饱和的状态。

[0105]

如图5所示,在短路时负载的电感值小的情况下的屏蔽时间tw1为约4.6 (μs)。

[0106]

图6是表示第一实施例以及第二实施例中在短路时负载的电感值大的情况下的模拟波形的图。在图6中,横轴是时刻,纵轴是电压值(v)以及电流值(a)。波形g201是电流ic的波形。波形g202是栅极电压vge的波形。波形g203是vdesat电压的波形。波形g204是电压vce的波形。

[0107]

如图6所示,在短路时负载的电感值大的情况下的屏蔽时间tw2为约4.5 (μs)。

[0108]

如图5、图6所示,根据第一实施例、第二实施例的结构,即使负载的电感值发生变化,屏蔽时间也相同。

[0109]

《第三实施例》

[0110]

接着,对第三实施例进行说明。图7是第三实施例的驱动电路的电路图。如图7所示,驱动电路1c包括驱动器10及desat电路20c。

[0111]

desat电路20c包括电容器cdesat(第一电容器)、电阻r211(第一电阻)、晶体管q23(第一晶体管)、电阻r212(第二电阻)、电阻r213(第三电阻)、晶体管q22c(第二晶体管)、电阻r217(第七电阻)、电阻r204(第四电阻)、电阻r205(第五电阻)、二极管d22(第一二极管)、二极管d23 (第三二极管)、电阻r206(第六电阻)、缓冲器31及二极管ddesat(第二二极管)。

[0112]

如图7所示,desat电路20c中,电容器cdesat的一端与电阻r211的一端连接,且另一端接地。晶体管q23例如为npn型,且所述晶体管q23 的集电极与电阻r211的另一端连接,发射极接地,基极与电阻r212的一端以及电阻r213的一端连接。电阻r212的另一端与电阻r217的一端以及晶体管q22c的集电极连接。电阻r213的另一端接地。晶体管q22c的发射极接地,且基极与电阻r204的一端以及电阻r205的一端连接。电阻r204的另一端接地。电阻r217的另一端与二极管d23的阴极以及电阻r206的另一端连接。电阻r205的另一端与二极

管d22的阳极连接。二极管d22的阴极与电阻r206的一端以及二极管ddesat的阳极连接。二极管d23的阳极与驱动器10的out端子以及缓冲器31的输入端子连接。二极管ddesat的阴极与开关元件41的集电极连接。缓冲器31的输出端子与开关元件41的栅极连接。

[0113]

表g503

[0114][0115]

如表g503所示,在开关元件41接通的情况下,第三实施例的desat电路20c中,二极管d22为关断状态,晶体管q23以及晶体管q22c为关断状态,驱动器10的晶体管q11为导通状态。

[0116]

如表g503所示,在开关元件41接通且vce小于第一规定电压值而为正常的情况下,在第三实施例的desat电路20c中,二极管d22以及晶体管 q22c成为关断状态,晶体管q23成为导通状态,驱动器10的晶体管q11成为关断状态。在第三实施例中,如此在开关元件41接通且vce小于第一规定电压值而为正常的情况下,二极管d22为关断状态,晶体管q23为导通状态,由此使desat端子为0(v)。然后,从驱动器10的desat端子输出的电流被充电至desat电路20c的电容器cdesat,直至式(1)的第三规定电压值为止。

[0117]

如表g503所示,在开关元件41接通且vce异常上升至第一规定电压值以上的情况下,desat电路20c中,二极管d22以及晶体管q22c成为导通状态,晶体管q23成为关断状态,驱动器10的晶体管q11成为关断状态。然后,电容器cdesat开始从驱动器10的desat端子输出的电流的充电,当达到基准电压vdesatth(第二规定电压值)以上时,停止充电动作。然后,在电容器cdesat达到第三规定电压值的屏蔽时间tw后,驱动器10向控制部 30输出异常检测信号,并根据控制部30的控制将开关元件41的栅极电平切换为低电平。此外,屏蔽时间tw由下式(3)决定。

[0118]

[数式3]

[0119][0120]

此外,在式(3)中,vdesatth是基准电压值,idesat是电流源idesat的电流值,r211是电阻r211的电阻值。

[0121]

如式(3)所示,第三实施例的屏蔽时间tw不包括二极管d21的项,因此与第一实施例以及第二实施例的屏蔽时间tw相比可更精度良好地设定。

[0122]

《第四实施例》

[0123]

接着,对第四实施例进行说明。图8是第四实施例的驱动电路的电路图。如图8所示,驱动电路1d包括驱动器10及desat电路20d。

[0124]

desat电路20d包括电容器cdesa(第一电容器)、电阻r211(第一电阻)、晶体管q23(第一晶体管)、电阻r212(第二电阻)、电阻r213(第三电阻)、晶体管q22c(第二晶体管)、电阻r217d(第七电阻)、电阻r204 (第四电阻)、电阻r205(第五电阻)、二极管d22(第一二极

管)、电阻r206d (第六电阻)、缓冲器31、及二极管ddesat(第二二极管)。

[0125]

如图8所示,相对于图7而言desat电路20d不包括二极管d23,而在电阻r217d、电阻r206d连接有正电压vcc1。

[0126]

在第三实施例的desat电路20c中,在脉冲信号为高电平的期间向电阻r217以及电阻r206施加电压,但在第四实施例的desat电路20d中,中,不论脉冲信号的电平如何均向电阻r217d以及电阻r206d供给电压。

[0127]

表g504

[0128][0129]

如表g504所示,在开关元件41断开的情况下,第四实施例的desat电路20d中,二极管d22为导通状态,晶体管q23为关断状态,晶体管q22c 为导通状态,驱动器10的晶体管q11为导通状态。

[0130]

如表g504所示,在开关元件41接通且vce小于第一规定电压值而为正常的情况下,在第四实施例的desat电路20d中,二极管d22以及晶体管 q22c成为关断状态,晶体管q23成为导通状态,驱动器10的晶体管q11成为关断状态。在第四实施例中,如此在开关元件41接通且vce小于第一规定电压值而为正常的情况下,二极管d22为关断状态,晶体管q23为导通状态,由此使desat端子为0(v)。然后,从驱动器10的desat端子输出的电流被充电至desat电路20d的电容器cdesat,直至式(1)的第三规定电压值为止。

[0131]

如表g504所示,在开关元件41接通且vce异常上升至第一规定电压值以上的情况下,desat电路20d中,二极管d22以及晶体管q22c成为导通状态,晶体管q23成为关断状态,驱动器10的晶体管q11成为关断状态。然后,电容器cdesat开始从驱动器10的desat端子输出的电流的充电,当达到基准电压vdesatth(第二规定电压值)以上时,停止充电动作。然后,在电容器cdesat达到第三规定电压值的屏蔽时间tw后,驱动器10向控制部 30输出异常检测信号,并根据控制部30的控制将开关元件41的栅极电平切换为低电平。此外,屏蔽时间tw由式(3)决定。第四实施例的屏蔽时间tw 不包括二极管d21的项,因此与第一实施例以及第二实施例的屏蔽时间tw 相比可更精度良好地设定。

[0132]

在第三实施例以及第四实施例的情况下,不包括第一实施例以及第二实施例所包括的二极管d21。不需要二极管d21的理由在于,在第三实施例以及第四实施例的情况下,即使当晶体管q23成为导通状态时,也不会对驱动器10的desat端子施加来自外部的电压。

[0133]

接着,关于第三实施例以及第四实施例的结构,来说明波形的模拟结果例。

[0134]

图9是表示第三实施例以及第四实施例中在短路时负载的电感值小的情况下的模拟波形的图。在图9中,横轴是时刻(μs),纵轴是电压值(v)以及电流值(a)。波形g301是电流ic的波形。波形g302是栅极电压vge的波形。波形g303是vdesat电压的波形。波形g304是电压vce的波形。

[0135]

如图9所示,在短路时负载的电感值小的情况下的屏蔽时间tw3为约4.7 (μs)。

[0136]

图10是表示第三实施例以及第四实施例中在短路时负载的电感值大的情况下的模拟波形的图。在图10中,横轴是时刻(μs),纵轴是电压值(v) 以及电流值(a)。波形g401是电流ic的波形。波形g402是栅极电压vge 的波形。波形g403是vdesat电压的波形。波形g404是电压vce的波形。

[0137]

如图10所示,在短路时负载的电感值大的情况下的屏蔽时间tw4为约 4.7(μs)。

[0138]

如图9、图10所示,根据第三实施例、第四实施例的结构,即使负载的电感值发生变化,屏蔽时间也相同。

[0139]

此处,为了提高屏蔽时间的精度,也考虑例如在图1的desat电路20 中,电路块21的电路例如使用开路集电极型的比较器、电阻、电容器、二极管来构成,且在desat电路内产生阈值电压来进行比较的结构。在此种电路结构中,比较器将开关元件的集电极-发射极间电压与规定的阈值电压进行比较。然而,在此种电路结构中,构成零件数量会变多。例如,构成零件有一个比较器、四个电阻、三个电容器及两个二极管。在此种结构的电路中,构成零件数量多、且电路成本比本实施方式高。此外,在本实施方式中,二极管d22以及晶体管q22起到比较器的作用。另外,在本实施方式中,如上所述,通过二极管d22的两端的电压,设定desat电路20(20a、20b、20c、 20d)。

[0140]

即,根据本实施方式的结构,与如此在desat电路中使用比较器的情况相比较,可降低成本,可减少零件个数。

[0141]

此外,在所述实施方式、各实施例中,对在开关元件41的集电极连接有正电压、且发射极接地的结构例进行了说明,但并不限于此。在开关元件41 的集电极也可连接有其他开关元件(未图示)的发射极,在发射极也可连接有其他开关元件的集电极。

[0142]

以上,使用实施方式、实施例对用以实施本实用新型的方式进行了说明,但本实用新型并不受此种实施方式的任何限定,可在不脱离本实用新型的主旨的范围内实施各种变形及置换。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1