一种无电流采样的无桥PFC变换器系统

一种无电流采样的无桥pfc变换器系统

技术领域

1.本实用新型涉及开关电源技术领域,特别涉及一种无电流采样的无桥pfc变换器系统。

背景技术:

2.随着时代的发展以及更迭,无线通信的使用越来越深入到人们的日常生活中,例如蓝牙、无线局域网(wifi)和全球卫星定位系统等技术。收发机作为实现无线通信的重要设备,而功率放大器又在收发机中扮演着极其重要的角色。

3.目前主流的功率放大器设计工艺为gaas和gan,因为其具有良好的射频性能和能够承受大功率的输出。但是采用主流设计工艺会难以集成整个收发机芯片,面临成本高的问题。硅基工艺设计具有高集成度的优点,但是采用硅基工艺设计功率放大器依然是一个具有挑战性的任务。首先是因为采用硅基工艺设计会面临一个无源器件损耗大的问题,从而导致功率放大器的效率下降。其次,为了提高硅基工艺晶体管的工作频率,需要通过减小晶体管的特征尺寸来提高其射频性能。这样会导致硅基晶体管的击穿电压进一步下降,使基于硅基工艺的功率放大器难以实现输出大功率的效果。采用堆叠式功率放大器和采用功率合成技术是目前能够有效解决问题的一种方法。

4.目前主流的双路功率合成方式是威尔金森合成器,但是威尔金森合成器所占用的面积大,若是更多路进行合成,所占用的面积会更大。采用片上变压器进行多路合成是一个能够有效节省面积的方法,并且片上变压器具有更大的设计自由度。但是采用片上变压器进行多路合成会面临高损耗的问题。电力电子设备在电力系统和日常生活中的广泛使用,在带来了便捷的同时也存在着严重的电流谐波污染问题。由于电网电压直接连接电力电子设备,它们之间通过不受控的整流桥电路结构将交流电压转换为直流电压供电力电子设备使用,此电路结构不仅功率因数低而且会给电网带来电流谐波污染,同时降低了线路传输有源功率的能力,使配电电缆和变电站变压器加速老化。为了用电设备的高效节能,以及电网设备的安全运行与寿命延长,近年来带有功率因数校正(pfc)的交流-直流变换器成为研究热点,其中在无桥pfc变换器中,图图腾柱拓扑以其组件数量少、共模干扰低、传导损耗低、效率高等优点在功率因数校正电路拓扑中备受关注。

5.随着氮化镓(gan)、碳化硅(sic)等第三代宽禁带半导体器件的出现,将制约图腾柱拓扑在连续电流模式下运行的第一大阻力即二极管反向恢复问题迎刃而解,使用该材料的开关器件具有开关速度快、导通电阻小等优点,使图腾柱无桥pfc变换器在连续电流模式下的大功率场合应用成为可能。目前,图腾柱拓扑的无桥pfc变换器常使用数字处理器芯片实现数字控制,为了实现有效的电路控制,对无桥pfc变换器的电压和电流采样是必不可少的,其中包括交流侧的输入电压采样、输入电流采样以及直流侧的输出电压采样,这些采样不但增加了电路制作成本与控制的复杂程度,而且对于电流的采样不仅降低了无桥pfc变换器的电能传输效率,还会因不合理的电路板布线方式而引入开关噪声和振铃。

6.在众多大功率应用场合下,为了提高pfc变换器的电能传输效率,无桥pfc拓扑是

首选的拓扑方案。其中,为了解决无桥pfc变换器的输入电流采样问题,目前已有几种无电流采样的控制方法在不同无桥pfc拓扑上的应用。

7.ieee transactions on power electronics【ieee电力电子学报】于2017年发表的文献“digital current sensorless control for dual-boost half-bridge pfc converter with natural capacitor voltage balancing”【具有自然电容电压平衡的双升压半桥pfc变换器的数字无电流传感器控制】中,介绍了一种双升压半桥pfc变换器的无电流传感器控制方法,利用平均状态空间法得到等效的单开关模型,并在开关管导通压降和电感内阻知悉的条件下,计算出每个开关周期的占空比,最后校正功率因数。专利cn202010778540.8于2020年公开的“一种无电流传感器无桥pfc电路”介绍了一种双升压无桥pfc变换器的无电流传感器控制方法,提出了用时间平均法计算每个开关周期的电感电压,同样在知悉了开关管导通压降和电感内阻的条件下,再根据电感电压推导出每个开关周期的占空比,实现无电流传感器的功率因数校正。这两种方法都是在假设了开关管导通压降和电感内阻已知的条件,才能实现功率因数的校正,但是由于电感内阻、开关管内阻和二极管压降这些寄生参数的难以测量,并且其压降都是随着时间而变化的,所以在计算占空比时只能估计大概的值,这使得计算出的电感电压偏离了实际的电感电压,因而导致功率因数的下降,当输入电压和负载变化时,难以一直保持较高的功率因数。

8.ieee journal of emerging and selected topics in power electronics【ieee电力电子新兴和选定主题杂志】于2019年发表的文献“current-sensorless power factor correction with predictive controllers”【使用预测控制器进行无电流传感器的功率因数校正】中,提出了利用锁相环计算电网电压和无桥拓扑中点电压之间的相位角,并通过不断修正该相位角来计算每个开关周期的占空比,从而实现功率因数的校正。这种方法在计算相位角的过程中忽略了电路的损耗部分,同时利用了升压电感的感量和输出电容的容量参与计算过程,这些损耗的功率和元件参数在电路运行时都会发生变化,因此该方法对这些变化难以作出适应,使得功率因数降低。此外文中还使用了昂贵的模数转换(adc)芯片和数字信号处理器(dsp)芯片,提高了成本。

9.由此可知,上述无电流采样无桥pfc变换器只能在测量电路中部分元器件参数和寄生参数的情况下,借助高性能和昂贵的adc芯片和dsp芯片实现恒压输出和功率因数的校正,这不仅限制了功率因数的提高,还增加了电路成本。

技术实现要素:

10.本实用新型的目的是提供一种无电流采样的无桥pfc变换器系统,旨在解决如下问题:在不采样电流和不测量电路中所有元器件参数和寄生参数的情况下,使用较为廉价的adc芯片和dsp芯片实现恒压输出和功率因数的校正,降低电路的复杂程度和电路成本。

11.为此,本实用新型公开了一种无电流采样的无桥pfc变换器系统,该系统由一个主电路模块和多个子模块共同组成,其主电路模块为图腾柱无桥pfc电路模块,子模块包括辅助供电电源、微处理器控制模块、pwm发生模块、隔离驱动电路、输入电压采样模块、输入过零检测模块和输出电压采样模块;

12.优选地,所述图腾柱无桥pfc电路模块与第一、第二隔离驱动模块的输出端连接,输入电压采样模块的输入端与图腾柱无桥pfc电路模块连接,输出电压采样模块的输入端

与图腾柱无桥pfc电路模块连接,输入过零检测模块的输入端与输入电压采样模块的输出端连接,所述微处理器控制模块与输入电压采样模块、输入过零检测模块和输出电压采样模块的输出端连接,所述pwm发生模块与微处理器控制模块的输出端连接,所述第一隔离驱动模块与pwm发生模块的输出端连接,所述第二隔离驱动模块与pwm发生模块的输出端连接。

13.优选地,所述图腾柱无桥pfc电路模块包括输入交流电源v

in

、高频功率mos管q1、高频功率mos管q2、整流功率mos管q3、整流功率mos管q4、升压电感l、输出滤波电容c和负载电阻r,其中:

14.所述高频功率mos管q1的源极分别与高频功率mos管q2的漏极、升压电感l的一端连接,所述高频功率mos管q1的漏极分别与整流功率mos管q3的漏极、输出滤波电容c的正极、负载电阻r的一端连接,所述高频功率mos管q2的源极分别与整流功率mos管q4的源极、输出滤波电容c的负极、负载电阻r的另一端连接,所述整流功率mos管q3的源极分别与输入交流电源v

in

的一端、整流功率mos管q4的漏极连接,所述整流功率mos管q4的源极分别与高频功率mos管q2的源极、输出滤波电容c的负极、负载电阻r的另一端连接,所述升压电感l的另一端与输入交流电源v

in

的另一端连接;

15.所述输入交流电源v

in

的两端还与输入电压采样模块的输入端连接,所述输出滤波电容的两端还与输出电压采样模块的输入端连接。

16.优选地,所述输入电压采样模块中连接顺序依次为第一隔离差分运放电路、第一滤波电路、第一跟随电路、第二滤波电路和第一限幅电路,其中:

17.所述第一隔离差分运放电路的输入端与输入交流电源v

in

的两端连接,所述第一滤波电路的输入端与第一隔离差分运放电路的输出端连接,所述第一跟随电路的输入端与第一滤波电路的输出端连接,所述第二滤波电路的输入端与第一跟随电路的输出端连接,所述第一限幅电路的输入端与第二滤波电路的输出端连接;

18.所述第一限幅电路的输出端还与微处理器控制模块的输入端连接。

19.优选地,所述输入过零检测模块中连接顺序依次为线性模块电路、比较电路、第一电阻分压电路、第三滤波电路和第二限幅电路,其中:

20.所述线性模块电路的输入端与5v直流电源连接,所述比较电路的输入端与线性模块电路的输出端连接,所述比较电路的另一输入端与第一限幅电路的输出端连接,所述第一电阻分压电路的输入端与比较电路的输出端连接,所述第三滤波电路的输入端与第一电阻分压电路的输出端连接,所述第二限幅电路的输入端与第三滤波电路的输出端连接;

21.所述第二限幅电路的输出端还与微处理器控制模块的输入端连接。

22.优选地,所述输出电压采样模块中连接顺序依次为第二隔离差分运放电路、第四滤波电路、第二跟随电路、第二电阻分压电路、第五滤波电路、第三限幅电路,其中:

23.所述第二隔离差分运放电路的输入端与输出滤波电容的两端连接,所述第四滤波电路的输入端与第二隔离差分运放电路的输出端连接,所述第二跟随电路的输入端与第四滤波电路的输出端连接,所述第二电阻分压电路的输入端与第二跟随电路的输出端连接,所述第五滤波电路的输入端与第二电阻分压电路的输出端连接,所述第三限幅电路的输入端与第五滤波电路的输出端连接;

24.所述第三限幅电路的输出端还与微处理器控制模块的输入端连接。

25.优选地,所述微处理器控制模块包括dsp芯片电路、芯片供电电路、复位电路、jtag下载器电路、外部adc参考电压电路、按键电路、显示屏电路和过压采样保护电路,其中:

26.所述dsp芯片电路分别与芯片供电电路、复位电路、jtag下载器电路、外部adc参考电压电路、按键电路、显示屏电路、过压采样保护电路连接,所述dsp芯片电路作为微处理器控制模块的核心与其他所述电路协同工作,所述dsp芯片电路的输出端还与pwm发生模块连接。

27.优选地,所述pwm发生模块连接顺序依次为pwm使能电路、缓冲电路和上拉电路,其中:

28.所述pwm使能电路的输入端与微处理器控制模块的输出端连接,所述缓冲电路的输入端与pwm使能电路的输出端连接,所述缓冲电路的另一输入端与dsp芯片电路连接,所述上拉电路的输入端与缓冲电路的输出端连接,所述上拉电路的输出端分别与第一隔离驱动模块和第二隔离驱动模块连接。

29.优选地,所述第一隔离驱动模块和第二隔离驱动模块结构相同,其模块内部包括隔离驱动芯片电路、自举电路、mos管驱动电路,其中:

30.所述隔离驱动芯片电路的输入端分别与pwm发生模块的输出端、5v和12v直流电源连接,所述自举电路的输入端与12v直流电源连接,所述自举电路的输出端与隔离驱动芯片电路的输出端连接,所述mos管驱动电路的输入端与隔离驱动芯片电路的输出端连接,所述mos管驱动电路的输出端分别与图腾柱无桥pfc电路模块连接,所述第一隔离驱动模块与图腾柱无桥pfc电路模块中mos管q1和q2的栅极连接,所述第二隔离驱动模块与图腾柱无桥pfc电路模块中mos管q3和q4的栅极连接。

31.优选地,所述辅助供电电源由多个线性电源芯片电路组成,分别提供3.3v直流电源、5v直流电源和12v直流电源。

32.本实用新型提供的图腾柱无桥pfc变换器系统,与传统无桥pfc变换器相比较,本发明减少了输入电流的采样电路,在降低整个系统复杂性的同时,还减少了电路成本,由于不使用电流采样电路,不仅减小了变换器的体积,还在一定程度上提高了系统的转换效率,此外还避免了电流采样电路所造成的噪声引入,提高了系统的稳定性。

附图说明

33.此处的附图被并入说明书中并构成本说明书的一部分,标示出了符合本实用新型的实施例,并与说明书一起用于解释本实用新型的原理。

34.为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,对于本领域普通技术人员而言,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

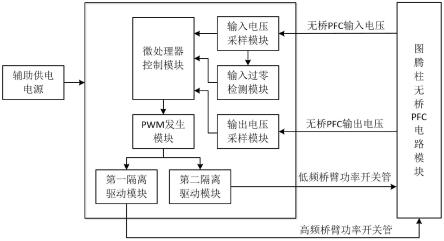

35.图1为本实用新型的无电流采样的无桥pfc变换器系统框图;

36.图2为本实用新型的输入电压采样模块图;

37.图3为本实用新型的输入过零检测模块图;

38.图4为本实用新型的输出电压采样模块图;

39.图5为本实用新型的微处理器控制电路模块和pwm发生电路模块图;

40.图6为本实用新型的隔离驱动电路模块图;

41.图7为本实用新型的图腾柱无桥pfc电路拓扑结构;

42.图8为本实用新型图腾柱无桥pfc电路的工作的第一阶段;

43.图9为本实用新型图腾柱无桥pfc电路的工作的第二阶段;

44.图10为本实用新型图腾柱无桥pfc电路的工作的第三阶段;

45.图11为本实用新型图腾柱无桥pfc电路的工作的第四阶段;

46.图12为本实用新型的无电流采样的无桥pfc变换器系统控制流程图;

47.图13为本实用新型的第n到n+1个工频周期下的平均电感补偿电压的自适应校正流程图。

具体实施方式

48.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型的一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

49.需要说明,本实用新型实施例中所有方向性指示(诸如上、下、左、右、前、后

……

)仅用于解释在某一特定姿态(如附图所示)下各部件之间的相对位置关系、运动情况等,如果该特定姿态发生改变时,则该方向性指示也相应地随之改变。

50.另外,在本实用新型中涉及“第一”、“第二”等的描述仅用于描述目的,而不能理解为指示或暗示其相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一种该特征。另外,各个实施例之间的技术方案可以相互结合,但是必须是以本领域普通技术人员能够实现为基础,当技术方案的结合出现相互矛盾或无法实现时应当认为这种技术方案的结合不存在,也不在本实用新型要求的保护范围之内。

51.本实用新型的图1为无电流采样的无桥pfc变换器系统框图,该系统框图由一个主电路模块和多个子模块共同组成,其主电路模块为图腾柱无桥pfc电路模块,子模块包括辅助供电电源、微处理器控制模块、pwm发生模块、隔离驱动电路、输入电压采样模块、输入过零检测模块和输出电压采样模块;

52.所述图腾柱无桥pfc电路模块与第一、第二隔离驱动模块的输出端连接,输入电压采样模块的输入端与图腾柱无桥pfc电路模块连接,输出电压采样模块的输入端与图腾柱无桥pfc电路模块连接,输入过零检测模块的输入端与输入电压采样模块的输出端连接,所述微处理器控制模块与输入电压采样模块、输入过零检测模块和输出电压采样模块的输出端连接,所述pwm发生模块与微处理器控制模块的输出端连接,所述第一隔离驱动模块与pwm发生模块的输出端连接,所述第二隔离驱动模块与pwm发生模块的输出端连接。

53.优选地,所述图腾柱无桥pfc电路模块包括输入交流电源v

in

、高频功率mos管q1、高频功率mos管q2、整流功率mos管q3、整流功率mos管q4、升压电感l、输出滤波电容c和负载电阻r,其中:

54.所述高频功率mos管q1的源极分别与高频功率mos管q2的漏极、升压电感l的一端连接,所述高频功率mos管q1的漏极分别与整流功率mos管q3的漏极、输出滤波电容c的正极、负载电阻r的一端连接,所述高频功率mos管q2的源极分别与整流功率mos管q4的源极、

输出滤波电容c的负极、负载电阻r的另一端连接,所述整流功率mos管q3的源极分别与输入交流电源v

in

的一端、整流功率mos管q4的漏极连接,所述整流功率mos管q4的源极分别与高频功率mos管q2的源极、输出滤波电容c的负极、负载电阻r的另一端连接,所述升压电感l的另一端与输入交流电源v

in

的另一端连接;

55.所述输入交流电源v

in

的两端还与输入电压采样模块的输入端连接,所述输出滤波电容的两端还与输出电压采样模块的输入端连接。

56.优选地,所述输入电压采样模块中连接顺序依次为第一隔离差分运放电路、第一滤波电路、第一跟随电路、第二滤波电路和第一限幅电路,其中:

57.所述第一隔离差分运放电路的输入端与输入交流电源v

in

的两端连接,所述第一滤波电路的输入端与第一隔离差分运放电路的输出端连接,所述第一跟随电路的输入端与第一滤波电路的输出端连接,所述第二滤波电路的输入端与第一跟随电路的输出端连接,所述第一限幅电路的输入端与第二滤波电路的输出端连接;

58.所述第一限幅电路的输出端还与微处理器控制模块的输入端连接。

59.优选地,所述输入过零检测模块中连接顺序依次为线性模块电路、比较电路、第一电阻分压电路、第三滤波电路和第二限幅电路,其中:

60.所述线性模块电路的输入端与5v直流电源连接,所述比较电路的输入端与线性模块电路的输出端连接,所述比较电路的另一输入端与第一限幅电路的输出端连接,所述第一电阻分压电路的输入端与比较电路的输出端连接,所述第三滤波电路的输入端与第一电阻分压电路的输出端连接,所述第二限幅电路的输入端与第三滤波电路的输出端连接;

61.所述第二限幅电路的输出端还与微处理器控制模块的输入端连接。

62.优选地,所述输出电压采样模块中连接顺序依次为第二隔离差分运放电路、第四滤波电路、第二跟随电路、第二电阻分压电路、第五滤波电路、第三限幅电路,其中:

63.所述第二隔离差分运放电路的输入端与输出滤波电容的两端连接,所述第四滤波电路的输入端与第二隔离差分运放电路的输出端连接,所述第二跟随电路的输入端与第四滤波电路的输出端连接,所述第二电阻分压电路的输入端与第二跟随电路的输出端连接,所述第五滤波电路的输入端与第二电阻分压电路的输出端连接,所述第三限幅电路的输入端与第五滤波电路的输出端连接;

64.所述第三限幅电路的输出端还与微处理器控制模块的输入端连接。

65.优选地,所述微处理器控制模块包括dsp芯片电路、芯片供电电路、复位电路、jtag下载器电路、外部adc参考电压电路、按键电路、显示屏电路和过压采样保护电路,其中:

66.所述dsp芯片电路分别与芯片供电电路、复位电路、jtag下载器电路、外部adc参考电压电路、按键电路、显示屏电路、过压采样保护电路连接,所述dsp芯片电路作为微处理器控制模块的核心与其他所述电路协同工作,所述dsp芯片电路的输出端还与pwm发生模块连接。

67.优选地,所述pwm发生模块连接顺序依次为pwm使能电路、缓冲电路和上拉电路,其中:

68.所述pwm使能电路的输入端与微处理器控制模块的输出端连接,所述缓冲电路的输入端与pwm使能电路的输出端连接,所述缓冲电路的另一输入端与dsp芯片电路连接,所述上拉电路的输入端与缓冲电路的输出端连接,所述上拉电路的输出端分别与第一隔离驱

动模块和第二隔离驱动模块连接。

69.优选地,所述第一隔离驱动模块和第二隔离驱动模块结构相同,其模块内部包括隔离驱动芯片电路、自举电路、mos管驱动电路,其中:

70.所述隔离驱动芯片电路的输入端分别与pwm发生模块的输出端、5v和12v直流电源连接,所述自举电路的输入端与12v直流电源连接,所述自举电路的输出端与隔离驱动芯片电路的输出端连接,所述mos管驱动电路的输入端与隔离驱动芯片电路的输出端连接,所述mos管驱动电路的输出端分别与图腾柱无桥pfc电路模块连接。所述第一隔离驱动模块与图腾柱无桥pfc电路模块中mos管q1和q2的栅极连接,所述第二隔离驱动模块与图腾柱无桥pfc电路模块中mos管q3和q4的栅极连接。

71.优选地,所述辅助供电电源由多个线性电源芯片电路组成,分别提供3.3v直流电源、5v直流电源和12v直流电源。

72.本实用新型在式模块连接关系的基础上,继续公开相应模块的工作原理。

73.图2为输入电压采样模块图,v

in+

和v

in-分别连接图8中输入交流电压源的上端和下端,并经过第一隔离差分运放电路,将输入的交流电压转换为0-3.3v的电压,并在第一隔离差分运放电路中加入1.5v的直流电压偏置,以实现不失真的负输入电压采样。然后将转换后的0-3.3v电压送入第一滤波电路进行滤波,再送入第一跟随电路以降低输出阻抗。最后再送入第二滤波电路和第一限幅电路后得到输入采样电压v

in_adc

。

74.图3为输入过零检测模块图,比较电路的正输入端与输入采样电压v

in_adc

连接,负输入端与线性电源芯片的1.5v输出直流电压连接,比较电路输出0v和5v电平信号,并送入第一电阻分压电路、第三滤波电路和第二限幅电路后,得到输入电压的过零点检测电压电平信号v

priority

。

75.图4为输出电压采样模块图,其中v

o+

和v

o-分别与图8中输出电容c的正极和负极连接,该两点间的电压为图腾柱无桥pfc电路的输出电压,将输出电压送入第二隔离差分运放电路,将输出电压转换为0-5v的电压并送入第四滤波电路滤波,然后将滤波后的电压送入第二跟随电路、第二电阻分压电路得到0-3.3v的采样电压,最后送入第五滤波电路和第三限幅电路得到输出采样电压v

o_adc

。

76.图5左部分为微处理器控制电路模块图,以dsp芯片电路为中心,四周为各自功能的子电路,其中,芯片供电电路为dsp芯片提供电源,复位电路为外部可手动复位dsp程序的电路,jtag下载器电路为电脑与dsp芯片间的程序下载通信电路,外部adc参考电压电路为dsp内的adc采样模块提供准确的3v参考电源,按键电路和显示屏电路为dsp的外扩功能性电路,以实现按键中断触发和必要信息的显示,过压采样保护为dsp的adc引脚提供安全的输入电压以保护dsp的安全运行。

77.图5右部分为pwm发生电路模块图,pwm使能电路的输入端分别连接dsp芯片的两个输出io引脚,以便dsp能通过程序控制pwm使能电路的输出电平,该输出电平信号分别与缓冲电路中的缓冲芯片使能引脚连接,以便控制缓冲芯片的输出引脚产生输出pwm信号。此外缓冲芯片的输入连接dsp芯片的四个pwm输出io引脚,该四路pwm信号由缓冲芯片控制是否输出,同时缓冲芯片的四路pwm输出信号经过上拉电路后,实现0v和5v的电平信号输出,以达到隔离驱动芯片的pwm电平要求。

78.图6为隔离驱动电路模块图,图中u7为半桥隔离驱动芯片,在芯片的via和vib引脚

分别与r28和r29相连构成强制低电平下拉电路的同时,还分别与pwm发生电路模块连接,且pwm发生电路模块的输出信号pwmxa和pwmxb由dsp所决定,其中x为1或2,当x为1时图7为第一隔离驱动电路并与高频桥臂的功率开关管相连接,当x为2时图7为第二隔离驱动电路并与低频桥臂的功率开关管相连接。

79.图6中12v直流电源经过自举电路后连接到芯片的vdda引脚为高低频桥臂中的上管q1和q3提供驱动电源,同时直接利用12v电源为高低频桥臂中的下管q2和q4提供驱动电源。voa和vob为驱动信号,并与驱动电路连接,gndxa和gndxb分别与芯片的gnda和gndb连接,gxa和gxb分别与桥臂的上管栅极控制端和下管栅极控制端连接,以驱动开关管的开通与关断。

80.本实用新型在以上电路模块图的工作原理基础上,继续公开微处理器控制模块中的控制方法并进行说明。

81.图7为本实用新型的图腾柱无桥pfc电路拓扑结构,其包括:高频功率mos管q1和q2、低频整流功率mos管q3和q4,以及q1、q2和q3、q4的体内并联二极管d1、d2和d3、d4,此外还包括功率升压电感l、输出滤波电容c、输入交流电压源v

in

和输出负载电阻r,考虑实际电路中可能存在的寄生参数,还有电感内阻r

l

和mos管的导通内阻r

ds

;q1和q2组成高频桥臂,q3和q4组成低频整流桥臂,输入交流电压源与升压电感串联,并与两个桥臂的中点相连构成输入部分的闭合回路;两个桥臂与滤波电容c、输出负载电阻r并联,构成输出部分的闭合回路;两部分闭合回路的共同组成部分由两组桥臂所构成,即为交流-直流变换部分。

82.优选地,参考图8-11,当输入交流电压在正半周时,q2、q4导通,q1、q3关断,电流由左向右流过升压电感l,电感上的电压为左正右负,该过程对升压电感l进行储能;电流从电容c的正极流向负载电阻r,最后回到电容c的负极,该过程电容为负载提供能量,并维持输出电压的恒定;

83.输入交流电压仍在正半周,q1、q4导通,q2、q3关断,电流由左向右流过升压电感l,电感上的电压为左负右正,该过程升压电感l进行释能;续流电流一部分流入输出滤波电容c,为电容c进行充电储能;另一部分电流流入输出负载电阻r,为负载提供能量,维持输出电压的恒定;

84.当输入交流电压在负半周时,q1、q3导通,q2、q4关断,电流由右向左流过升压电感l,电感上的电压为左负右正,该过程对升压电感l进行储能;电流从电容c的正极流向负载电阻r,最后回到电容c的负极,该过程电容为负载提供能量,并维持输出电压的恒定;

85.输入交流电压仍在负半周,q2、q3导通,q1、q4关断,电流由右向左流过升压电感l,电感上的电压为左正右负,该过程升压电感l进行释能;与此同时,续流电流一部分流入输出滤波电容c,为电容c进行充电储能;另一部分电流流入输出负载电阻r,为负载提供能量,维持输出电压的恒定。

86.本实用新型公开了一种无桥pfc变换器系统的控制,参考图12-13,包括:

87.步骤100,利用时间平均法建立图腾柱无桥pfc电路中平均电感电压的数学模型;

88.步骤200,将采样的输出电压送入dsp计算出实际的输出电压,输出电压与参考电压差值输入pid控制器,pid控制器的输出为平均电感峰值电压;

89.步骤300,设置补偿项补偿平均电感电压,补偿项为平均电感补偿电压,使得在任意时刻下所计算出的平均电感电压与实际电路运行时的平均电感电压相同;

90.步骤400,补偿项进行自适应校正控制;通过比较平均电感补偿峰值电压与平均电感参考补偿峰值电压来判断输出电压纹波相位角是否为零,若不为零,则以平均电感参考补偿峰值电压作为下一个工频周期的平均电感补偿峰值电压,在经过有限个工频周期后,有平均电感补偿峰值电压等于平均电感参考补偿峰值电压,即输出电压纹波相位角在有限时间内趋向于零,使得图图腾柱无桥pfc电路的功率因数趋向于1,从而实现平均电感补偿峰值电压的自适应校正。

91.步骤500,根据平均电感峰值电压计算结果和平均电感补偿峰值电压计算结果计算出每个开关周期下的占空比,并经过pwm驱动模块输出对应的控制信号对电路进行控制。

92.本实用新型提供的图腾柱无桥pfc变换器系统,使用图腾柱无桥pfc电路拓扑结构,在考虑寄生参数,如电感内阻、开关管内阻的情况下,进行电路拓扑的数学模型建模,利用时间平均法下算出电感电压的表达式,并在该表达式上增加合理的补偿电压去补偿计算的电感电压和实际电路中电感电压两者间的偏差,进一步提高功率因数。再通过输出电压纹波的相位信息计算出相应的补偿参考电压,使得补偿电压逼近补偿参考电压,直到稳态时补偿电压稳定在补偿参考电压处,实现功率因数的校正,减小寄生参数对功率因数的影响。包括以下优点:(1)减少了输入电流的采样电路,降低整个系统复杂性。(2)由于不使用电流采样电路,不仅减小了变换器的体积,还在一定程度上提高了系统的转换效率。(3)避免了电流采样电路所造成的噪声引入,提高了系统的稳定性。(4)不使用高精度adc采样芯片对输入电压和输出电压进行采样,节省电路成本。

93.优选地,步骤100,利用时间平均法建立图腾柱无桥pfc电路中平均电感电压的数学模型,包括:图腾柱无桥pfc电路拓扑的四个工作阶段,用t表示一个工频周期内的第t时刻,列出四个阶段的电感电压v

l

(t):

94.第一阶段:v

l

(t)=v

in

(t)-i

l

(t)

×

(r

l

+r

ds

);

95.第二阶段:v

l

(t)=v

in

(t)-i

l

(t)

×

(r

l

+r

ds

)-vo(t);

96.第三阶段:v

l

(t)=v

in

(t)-i

l

(t)

×

(r

l

+r

ds

);

97.第四阶段:v

l

(t)=v

in

(t)-i

l

(t)

×

(r

l

+r

ds

)+vo(t);

98.式中i

l

(t)表示输出电压直流量为v

dc

时所对应的电感电流,也为输入电流。

99.用x

ts

表示变量x在一个开关周期内的平均值,设一个开关周期内的导通时间为t

on

,开关周期为ts,则一个开关周期的输入交流电压和输入交流电流的平均值分别表示为:

[0100][0101][0102]

合并四个阶段的电感电压v

l

(t),得到一个开关周期的平均电感电压为:

[0103]vl

(t)

ts

=v

in

(t)

ts-i

l

(t)

ts

(r

l

+r

ds

)-sign(v

in

(t))(1-d(t))vo(t)(1)

[0104]

其中占空比d(t)为导通时间与开关周期的比值,sign(v

in

)为关于v

in

的符号函数:

[0105][0106]

优选地,步骤200将采样的输出电压送入dsp计算出实际的输出电压,输出电压与

参考电压差值输入pid控制器,pid控制器的输出为平均电感峰值电压;包括:使用隔离差分采样电路对输入和输出电压采样,将采样信号经过电阻分压电路转换为0到3.3v的电压信号,并传入到dsp芯片中;然后dsp芯片将反馈的输出电压经过adc转换后,计算出实际的输出电压vo,用设定的参考输出电压v

ref

与输出电压vo相减得到输出电压的误差值v

err

,再将v

err

输入pid控制器中进行运算,得到的输出结果作为电感的平均峰值电压vm;在输出电压稳定后,输出直流电压v

dc

等于参考输出电压v

ref

。

[0107]

设工频周期为tg,当输入交流电压与输入交流电流同为正弦波且相位相同时,求出一个开关周期下电感电流的平均值:

[0108][0109]

其中表示正弦输入电流的平均电流峰值。设电感的阻抗为ωl,根据欧姆定律,求出平均电感电压的峰值vm,并代入式(2)可得:

[0110][0111][0112]

根据电感电压公式求出平均电感电压:

[0113][0114]

设v

in

为输入交流电压峰值,io为输出负载电流,当电路转换效率为100%,有输入功率等于输出功率:结合式(3),推导出输出电压直流量的表达式:

[0115][0116]

由式(5)可以看出,当输入交流电压增大或负载电流减小时,可通过减小维持输出电压v

dc

不变;当输入交流电压减小或负载电流增大时,可通过增大维持输出电压v

dc

不变。

[0117]

根据上述公式推导设计出相应的pid电压控制器:使用隔离差分采样电路对输入和输出电压采样,将采样信号经过电阻分压电路转换为0到3.3v的电压信号,并传入到dsp芯片中。然后dsp芯片将反馈的输出电压经过adc转换后,计算出实际的输出电压vo,用设定的参考输出电压v

ref

与输出电压vo相减得到输出电压的误差值v

err

,再将v

err

输入pid程序进行运算,得到的输出结果作为电感的平均峰值电压在输出电压稳定后,输出直流电压v

dc

等于参考输出电压v

ref

。

[0118]

优选地,步骤300设置补偿项补偿平均电感电压,补偿项为平均电感补偿电压,使得在任意时刻下所计算出的平均电感电压与实际电路运行时的平均电感电压相同,包括:为了令输入电流为正弦电流即功率因数为1,需使相位角为零,并有推导的等式为:

[0119]

[0120]

在输入电压峰值时刻ta处,输出电压的瞬时值为v

dc

,此时所对应的占空比为da,将其代入式(6)求出电感的平均补偿峰值电压的参考值:

[0121][0122]

上式中即为下一个工频周期的平均电感补偿电压参考值,根据的计算结果,可在下一个工频周期对做出相应的校正。

[0123]

具体地,由于电路中总会存在各种损耗,因此电路的转换效率难以达到100%,而这些损耗主要由各种寄生参数所造成。在不降低输出功率的条件下,需要增大输入功率来补偿电路中损耗掉的功率。因此,在式(1)中,计算的平均电感电压与实际电路的平均电感电压会存在偏差。

[0124]

为了提高功率因数,让输入交流电流呈现出标准的正弦波,需要对各个开关周期的平均电感电压进行补偿,使计算的平均电感电压与实际的平均电感电压相同。

[0125]

设补偿的平均电感电压《δv

l

(t)》

ts

为:

[0126]

《δv

l

(t)》

ts

=(r

l

+r

ds

)《δi

l

(t)》

ts

ꢀꢀꢀ

(9)

[0127]

式中《δi

l

(t)》

ts

为为对应的平均电感补偿电流,设为补偿的平均电感电压峰值,则《δi

l

(t)》

ts

可表示为:

[0128][0129]

将式(10)加入到式(1)中,可得新的平均电感电压表达式:

[0130]

《v

l

(t)》

ts

=《v

in

(t)》

ts-(《i

l

(t)》

ts

+《δi

l

(t)》

ts

)(r

l

+r

ds

)-(1-d(t))vo(t)

ꢀꢀꢀ

(11)

[0131]

对上式作变形,求出实际的占空比d

real

(t)为:

[0132][0133]

令电感内阻和mos管内阻的和为r

par

,则上式中包含内阻的一项,即实际电路中电感内阻和mos管内阻上的平均电压总和《v

par

(t)》

ts

可表示为:

[0134][0135]

分析式(1)和式(11),当加入合适的平均电感补偿电压《δv

l

(t)》

ts

时,使得计算的平均电感电压与实际的平均电感电压相等,令输入交流电流呈现出标准的正弦波。

[0136]

但由于在实际电路中不采样输入电流,故对输入电流的信息是未知的,不能直接判断输入交流电流是否为标准的正弦波。为了解决该问题,可以从输出电压的低频纹波相位中找到关于输入交流电流的信息,并判断输入电流是否为标准的正弦波,从而间接地控制输入交流电流。

[0137]

对输出电压的低频纹波进行推导。求出输出的低频纹波电压v

ripple

(t)为:

[0138]

[0139]

由上式可知,当功率因数等于1时,输出电压的低频纹波相位角为零,而当电路中存在元器件损耗时,功率因数小于1,且输出电压的低频纹波产生一相位角因此实际的输出电压vo(t)为:

[0140][0141]

对比式(14)和式(15)可知,为了令输入电流为正弦电流即功率因数为1,需使相位角为零,因此,将式(15)和代入式(11),化简求出以下等式:

[0142][0143]

在输入电压峰值时刻ta处,输出电压的瞬时值为v

dc

,此时所对应的占空比为da,将其代入式(12)求出电感的平均补偿峰值电压的参考值为式(8):

[0144]

式(8)中即为下一个工频周期的平均电感补偿电压参考值,根据的计算结果,可在下一个工频周期对做出相应的校正。

[0145]

优选地,步骤400补偿项进行自适应校正控制,包括:设电路处于第n个工频周期,将采样的输入电压v

in

(t)和输出电压vo(t)代入式才计算每个开关周期的占空比,并对电路进行控制,直到最后一个开关周期结束时,把第n个工频周期中时刻ta[n]所对应的占空比da[n]代入式(8)计算出电感的平均补偿参考峰值电压

[0146]

然后判断与是否相等,若相等则不需要修正若不相等则根据与的差值计算第n个工频周期的修正量α,并在第n+1个工频周期使经过有限个工频周期的修正,使得逐渐逼近于最终电路进入稳态后满足

[0147]

具体地,根据上述和的公式推导以及与功率因数之间的关系,可以得出以下结论:当平均电感补偿峰值电压等于平均电感参考补偿峰值电压时,功率因数等于1,输入交流电流为标准的正弦波。

[0148]

优选地,步骤500包括:所述根据平均电感峰值电压计算结果和平均电感补偿峰值电压计算结果计算出每个开关周期下的占空比,并经过pwm驱动模块输出对应的控制信号对电路进行控制,包括:占空比表达式(12)。

[0149]

在输入交流电压正负半周的情况下,上式占空比均适用,因此在dsp中可直接利用式(12)来计算每个开关周期下的占空比,虽然式中l、r

l

和r

ds

都未知,但通过上述分析可知,只需调节使得补偿后的平均电感电压等于实际电路的平均电感电压即可实现功率因数的校正,因此避免了元件参数和寄生参数对功率因数的影响。

[0150]

优选的,在dsp的程序中,可对l、r

l

和r

ds

设置一个合理的初始值,如l=1mh、r

l

=0.1ω和r

ds

=1ω即可,然后由输出电压控制模块的输出和输入电流校正模块的输出共同参与占空比的计算,将计算出的占空比经过pwm模块转换成对应的方波信号,再通过驱动芯片输出驱动信号对开关管q1和q2进行控制。与此同时,通过输入电压过零检测电

平信号分别对开关管q3和q4给与驱动信号,即在输入交流电压正半周时,q4导通,q3关断,在输入交流电压负半周时,q3导通,q4关断。

[0151]

以上所述仅是本实用新型的具体实施方式,使本领域技术人员能够理解或实现本实用新型。对这些实施例的多种修改对本领域的技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本实用新型的精神或范围的情况下,在其它实施例中实现。因此,本实用新型将不会被限制于本文所示的这些实施例,而是要符合与本文所申请的原理和新颖特点相一致的最宽的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1