本技术涉及功率半导体,尤其涉及一种功率半导体模块中覆铜陶瓷基板的优化结构。

背景技术:

1、功率半导体模块是将功率半导体芯片按照一定的功能组合封装成一个整体,具有尺寸小、功率密度高等优点,因此在新能源汽车领域有着广泛的应用。随着新能源汽车高功率、长续航的发展,功率半导体模块的应用环境日益严苛,功率半导体模块的均流特性及耐压能力得到广泛关注。

2、随着新能源汽车的快速发展,si基和sic基功率半导体模块得到持续发展。在这些大功率的应用领域,对功率半导体模块的开关频率提出了越来越高的要求。为了获得更高的额定电流和更低的制造成本,这些功率半导体模块通常采用多芯片并联的封装结构。然而,由于覆铜陶瓷基板的电流回路不对称、功率芯片的动静态参数不一致,并联芯片间会出现较大的暂态不平衡电流及杂散电感,给功率半导体模块的安全和稳定带来不小的挑战。

3、在三相交流电动机控制系统中,功率半导体模块的电路图如图1所示,各相回路中并联连接多个上桥功率半导体芯片a1~a5以及下桥功率半导体芯片b1~b5;如图2和图3所示为u相电路图,在图2的电路图中,当上桥功率半导体芯片导通,下桥功率半导体芯片断开时,电流ia从正极母排流向三相母排。其中,各功率半导体芯片的源极与门极驱动回路信号的电阻值、长度产生的电感、功率半导体芯片之间的电阻和电感等决定了各功率半导体的开管时间。若功率半导体芯片a1的开关时间早于其他功率半导体芯片a2~a5,则大电流集中流过功率半导体芯片a1,极端情况下,会导致功率半导体芯片a1的损坏;此时若上桥电流回路的杂散电感过大,则功率半导体芯片a1~a5均存在电压过充的风险,因此会进一步增大功率半导体芯片a1的损坏风险。同理,如图3所示,当下桥功率半导体芯片导通,上桥功率半导体芯片断开时,电流ib从三相母排流向负极母排。在这种情况下,如上所述,当最靠近三相母排的功率半导体芯片b5的开关时间早于其他功率半导体芯片b1~ b4时,电流集中流过功率半导体芯片b5,极端情况下,会对功率半导体芯片b5造成破坏;此时若下桥电流回路的杂散电感过大,则功率半导体芯片b1~b5均存在电压过充的风险,因此会进一步增大功率半导体芯片b5的损坏风险。

4、在以高速驱动为目的的sic功率半导体模块中,有些在功率半导体芯片中设计开尔文源极。开尔文源极连接是将功率半导体芯片的源极分离成两部分,一部分用于流过大电流的主路径,另一部分用于门极驱动信号的返回路径。通过从功率半导体芯片门极、开尔文源极到门极、开尔文源极信号端子的信号线长度之和均匀化,能够削弱不同功率半导体芯片开关时间的偏差。在进行开尔文源极连接的情况下,优选在各功率半导体芯片门极信号线和开尔文源极信号线及信号纹路的合计长度ltn相等的设计方案。ltn定义如下:

5、ltn=lgn+lkn

6、其中,ltn为合计长度;lgn为芯片gate门极到门极信号端子的信号线及信号纹路长度之和;lkn为芯片开尔文源极到开尔文源极信号端子的信号线及信号纹路长度之和。

7、另外,当sic功率半导体模块高速驱动时,功率半导体芯片两端电压u=ldi/dt,若包括覆铜陶瓷基板的整个电流回路设计不合理,则杂散电感l过大,会导致整个电流回路产生较大的电压过充,严重时甚至击穿功率半导体芯片。在进行覆铜陶瓷基板设计的时候,可通过芯片排布、电流纹路对称、简化电流纹路及绑定连接方式等设计结构,减小整个电流回路的杂散电感。

技术实现思路

1、本实用新型所要解决的技术问题是提供一种功率半导体模块中覆铜陶瓷基板的优化结构,本结构通过覆铜陶瓷基板的芯片排布方式、电流纹路设计以及邦定线连接,调整门极与开尔文源极回路信号线的长度,确保各个功率半导体芯片开管时间的一致性,降低上桥、下桥及整个回路的寄生电感,实现均流特性和低电感特性,保证功率半导体模块的开管可靠性。

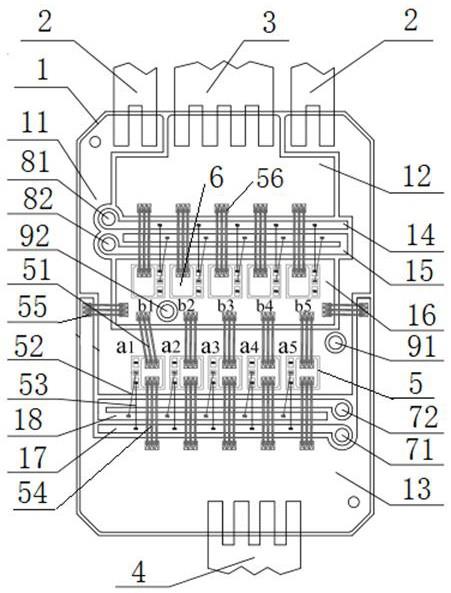

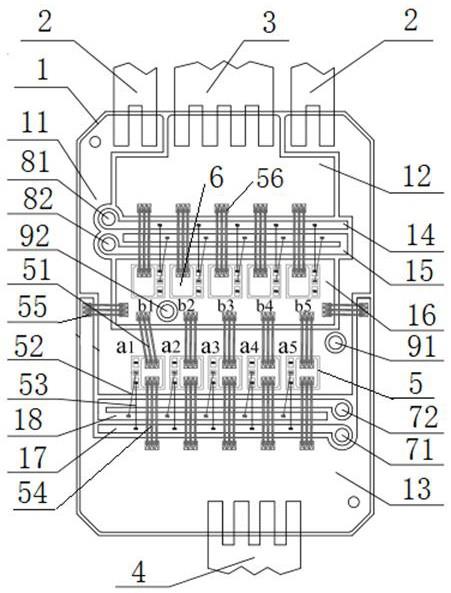

2、如图4所示,本实用新型适用于在一侧具有正极母排p和负极母排n、在相反侧具有三相母排u、v、w并且上下桥臂并联有3~5个功率半导体芯片的功率半导体模块,以承载大电流流过。

3、为解决上述技术问题,本实用新型功率半导体模块中覆铜陶瓷基板的优化结构,包括覆铜陶瓷基板、正极母排、负极母排、三相母排、若干上桥功率半导体芯片和若干下桥功率半导体芯片,所述覆铜陶瓷基板两侧从上部向中部延伸设有上桥覆铜纹路,所述覆铜陶瓷基板上部在两侧的上桥覆铜纹路之间设有负极覆铜纹路,所述正极母排分别连接所述覆铜陶瓷基板两侧的上桥覆铜纹路并位于覆铜陶瓷基板上部,所述负极母排连接负极覆铜纹路并位于覆铜陶瓷基板上部,所述覆铜陶瓷基板下部并向两侧延伸设有三相覆铜纹路,所述三相母排连接三相覆铜纹路并位于覆铜陶瓷基板下部,所述负极覆铜纹路下方并在覆铜陶瓷基板两侧的上桥覆铜纹路之间依次设有下桥开尔文源极信号纹路、下桥门极信号纹路和下桥覆铜纹路,所述三相覆铜纹路上方依次设有上桥开尔文源极信号纹路和上桥门极信号纹路,所述若干上桥功率半导体芯片横向间隔排布于所述覆铜陶瓷基板中部的上桥覆铜纹路,并且漏极连接上桥覆铜纹路、门极经门极信号线连接上桥门极信号纹路、开尔文源极经开尔文源极信号线连接上桥开尔文源极信号纹路、源极分别经第二绑定线连接三相覆铜纹路、经第一绑定线连接下桥覆铜纹路,所述若干下桥功率半导体芯片横向间隔排布于所述下桥覆铜纹路,并且漏极连接下桥覆铜纹路、门极经门极信号线连接下桥门极信号纹路、开尔文源极经开尔文源极信号线连接下桥开尔文源极信号纹路,源极经第三绑定线连接负极覆铜纹路,所述下桥覆铜纹路与三相覆铜纹路之间通过第一邦定线、上桥功率半导体芯片源极和第二邦定线连接或通过第四绑定线连接。

4、进一步,所述上桥开尔文源极信号纹路、上桥门极信号纹路、下桥开尔文源极信号纹路和下桥门极信号纹路平行布置。

5、进一步,所述上桥门极信号纹路和下桥门极信号纹路在通长范围内折弯成180度,所述若干上桥功率半导体芯片的门极和若干下桥功率半导体芯片的门极通过门极信号线分别连接所述上桥门极信号纹路和下桥门极信号纹路的折弯段。

6、进一步,所述若干上桥功率半导体芯片和若干下桥功率半导体芯片等距排布于所述上桥覆铜纹路和下桥覆铜纹路。

7、进一步,所述若干上桥功率半导体芯片和若干下桥功率半导体芯片上下交错排布于所述上桥覆铜纹路和下桥覆铜纹路。

8、进一步,所述上桥开尔文源极信号纹路和上桥门极信号纹路在同侧设有上桥开尔文源极信号端子和上桥门极信号端子,所述下桥开尔文源极信号纹路和下桥门极信号纹路在同侧设有下桥开尔文源极信号端子和下桥门极信号端子。

9、进一步,所述上桥覆铜纹路和下桥覆铜纹路分别设有上桥漏极信号端子和下桥漏极信号端子。

10、进一步,所述若干上桥功率半导体芯片中每个上桥功率半导体芯片的门极通过门极信号线、上桥门极信号纹路到上桥门极信号端子的长度加该上桥功率半导体芯片的开尔文源极通过开尔文源极信号线、上桥开尔文源极信号纹路到上桥开尔文源极信号端子的长度之和相近或相等;所述若干下桥功率半导体芯片中每个下桥功率半导体芯片的门极通过门极信号线、下桥门极信号纹路到下桥门极信号端子的长度加该下桥功率半导体芯片的开尔文源极通过开尔文源极信号线、下桥开尔文源极信号纹路到下桥开尔文源极信号端子的长度之和相近或相等。

11、进一步,所述上桥开尔文源极信号纹路和上桥门极信号纹路可互换,即上桥开尔文源极信号纹路作为上桥门极信号纹路,上桥门极信号纹路作为上桥开尔文源极信号纹路;所述下桥开尔文源极信号纹路和下桥门极信号纹路可互换,即下桥开尔文源极信号纹路作为下桥门极信号纹路,下桥门极信号纹路作为下桥开尔文源极信号纹路。

12、进一步,所述下桥覆铜纹路与三相覆铜纹路之间的第四绑定线位于所述三相覆铜纹路向覆铜陶瓷基板两侧延伸部的左侧、右侧或两侧。

13、由于本实用新型功率半导体模块中覆铜陶瓷基板的优化结构采用了上述技术方案,即本结构在覆铜陶瓷基板上分别设置上桥覆铜纹路、下桥覆铜纹路、负极覆铜纹路、三相覆铜纹路以及上桥开尔文源极信号纹路、上桥门极信号纹路、下桥开尔文源极信号纹路、下桥门极信号纹路,若干上桥功率半导体芯片和若干下桥功率半导体芯片分别设于上桥覆铜纹路和下桥覆铜纹路,并且开尔文源极、门极与相应的信号纹路连接,正极母排连接覆铜陶瓷基板两侧的上桥覆铜纹路,负极母排连接负极覆铜纹路,三相母排连接三相覆铜纹路,下桥覆铜纹路与三相覆铜纹路之间通过绑定线连接。本结构通过覆铜陶瓷基板的芯片排布方式、电流纹路设计以及邦定线连接,调整门极与开尔文源极回路信号线的长度,确保各个功率半导体芯片开管时间的一致性,降低上桥、下桥及整个回路的寄生电感,实现均流特性和低电感特性,保证功率半导体模块的开管可靠性。