用于具有主动驱动同步整流的有源箝位复位正向拓扑的耐辐射栅极驱动方案的制作方法

本技术涉及脉宽调制(pwm)控制器,更具体地,涉及一种pwm控制器,该pwm控制器使用用于具有主动驱动同步整流的有源箝位复位正向拓扑的耐辐射栅极驱动方案。

背景技术:

1、可使用可执行有源箝位复位的集成pwm控制器,以便实现90%或更高的效率。这些pwm控制器通常需要在输出侧上的伴随控制器来提供主动同步整流。另外,这些控制器通常在工作频率上被限制在不超过500khz。另外,这些控制器不耐辐射。

技术实现思路

1、本发明可应用于例如印刷电路板(pcb)和混合直流(dc)到直流(dc)转换器的集成pwm控制器。本公开提供了对常规集成pwm控制器的改进。例如,本公开使得执行有源箝位复位的集成pwm控制器在500khz以上工作。另外,本公开使得执行有源箝位复位的集成pwm控制器能够耐受辐射。

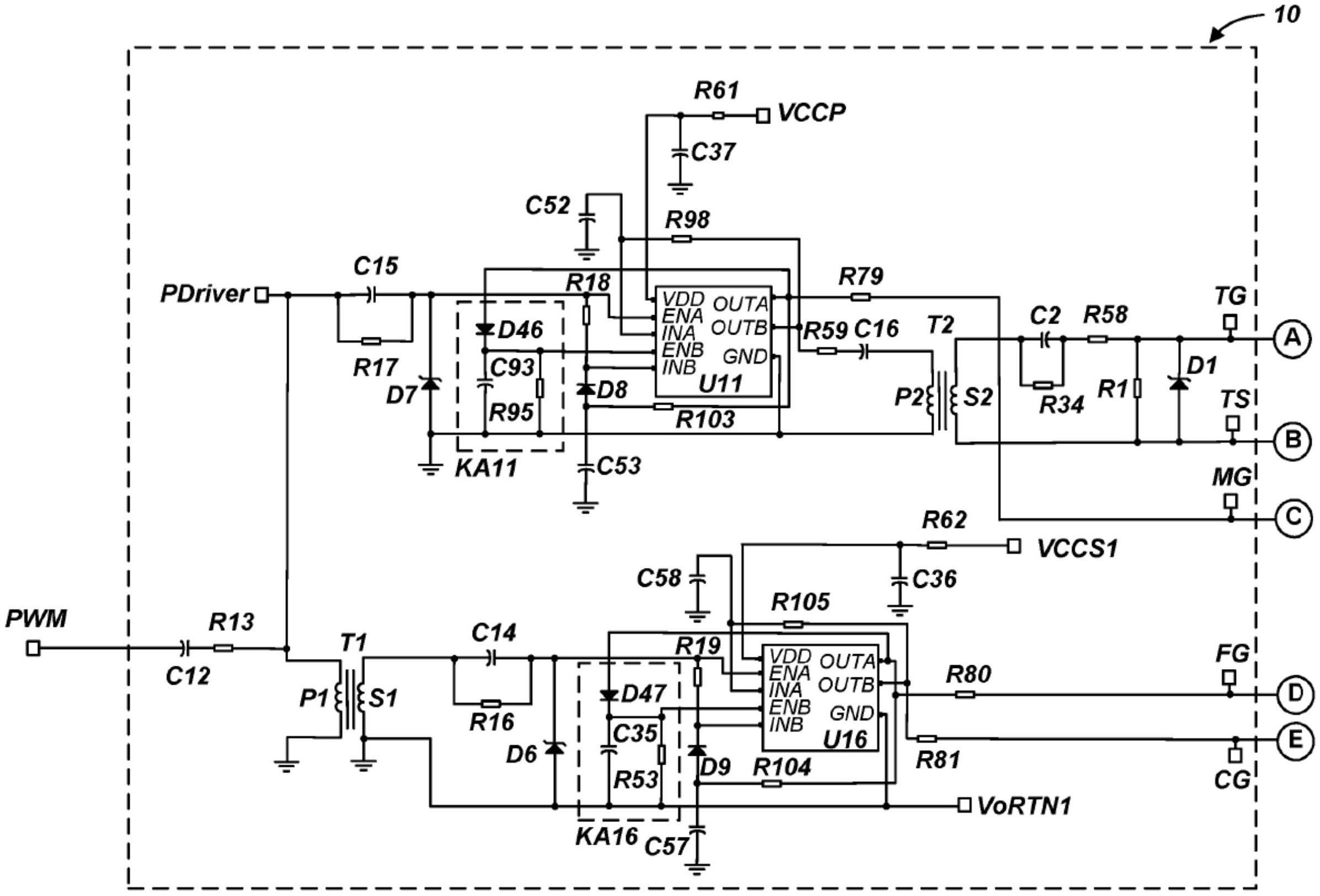

2、根据本公开的用于具有有源箝位复位和有源驱动同步整流的功率转换器的耐辐射栅极驱动器使用用于高效率和宽输入范围的集成逻辑驱动器。每个集成逻辑驱动器均包括两个栅极驱动器电路,且所述栅极驱动器电路中的每一个均使用所述栅极驱动器电路中的另一个的输出作为所述集成逻辑驱动器的逻辑表的输入,以确保在相应开关接通和断开时不进行直通。根据本公开的保持活动电路防止动力系开关在瞬态或欠压锁定(uvlo)事件之后在延长的持续时间内保持接通。保持活动电路可用于对dc到dc转换器的动力系命令三态状态。

3、一种栅极驱动器装置,其基于输入到根据本发明的栅极驱动器装置的信号而输出多个驱动信号,其特征在于,所述栅极驱动器装置包括:第一栅极驱动器电路,包括输入端子、启用端子和输出端子,其中所述第一栅极驱动器电路的输出端子处的电压电平取决于第一栅极驱动器电路的输入端子处的电压电平和第一栅极驱动器电路的启用端子处的电压电平;第二栅极驱动器电路,包括输入端子、启用端子和输出端子,其中第二栅极驱动器电路的输出端子处的电压电平取决于第二栅极驱动器电路的输入端子处的电压电平和第二栅极驱动器电路的启用端子处的电压电平,其中第一栅极驱动器电路的输出端子电联接至输出第一驱动信号的第一节点,其中第二栅极驱动器电路的输出端子电联接至输出第二驱动信号的第二节点,其中第一栅极驱动器电路的输出端子电联接至第二栅极驱动器电路的输入端子,其中第二栅极驱动器电路的输出端子电联接至第一栅极驱动器电路的输入端子,以及其中第一栅极驱动器电路的启用端子电联接至输入到栅极驱动器装置的信号;以及第三栅极驱动器电路,包括输入端子、启用端子和输出端子,其中,第三栅极驱动器电路的输出端子的电压电平取决于第三栅极驱动器电路的输入端子的电压电平和第三栅极驱动器电路的启用端子的电压电平;第四栅极驱动器电路,包括输入端子、启用端子和输出端子,其中,第四栅极驱动器电路的输出端子处的电压电平取决于第四栅极驱动器电路的输入端子处的电压电平和第四栅极驱动器电路的启用端子处的电压电平,其中,第三栅极驱动器电路的输出端子电联接至输出第三驱动信号的第三节点,其中第四栅极驱动器电路的输出端子电联接至输出第四驱动信号的第四节点,其中第三栅极驱动器电路的输出端子电联接至第四栅极驱动器电路的输入端子,其中第四栅极驱动器电路的输出端子电联接至第三栅极驱动器电路的输入端子,以及其中第三栅极驱动器电路的启用端子电联接至输入到栅极驱动器装置的信号。

4、在操作中,第一栅极驱动器电路可使第一栅极驱动器电路的输出端子具有第一电压电平或大于第一电压电平的第二电压电平,第一栅极驱动器电路可使第一栅极驱动器电路的输出端子具有第一电压电平,除非第一栅极驱动器电路的启用端子具有第二电压电平,并且第一栅极驱动器电路的输入端子同时具有第一电压电平。在操作中,第二栅极驱动器电路可使第二栅极驱动器电路的输出端子具有第一电压电平或第二电压电平,第二栅极驱动器电路可使第二栅极驱动器电路的输出端子具有第一电压电平,除非第二栅极驱动器电路的启用端子具有第二电压电平,并且第二栅极驱动器电路的输入端子同时具有第一电压电平。在操作中,第三栅极驱动器电路可使第三栅极驱动器电路的输出端子具有第一电压电平或第二电压电平,第三栅极驱动器电路可使第三栅极驱动器电路的输出端子具有第一电压电平,除非第三栅极驱动器电路的启用端子具有第二电压电平,并且第三栅极驱动器电路的输入端子同时具有第一电压电平,以及在操作中,第四栅极驱动器电路可使第四栅极驱动器电路的输出端子具有第一电压电平或第二电压电平,第四栅极驱动器电路可使第四栅极驱动器电路的输出端子具有第一电压电平,除非第四栅极驱动器电路的启用端子具有第二电压电平,且第四栅极驱动器电路的输入端子同时具有第一电压电平。

5、栅极驱动器装置可进一步包括:第一保持活动电路,包括第一二极管、第一电容器和第一电阻器,其中第一二极管的第一端子电联接至第一栅极驱动器电路的输出端子,以及第一二极管的第二端子电联接至第二栅极驱动器电路的启用端子,其中第一电容器的第一端子电联接至第二栅极驱动器电路的启用端子,以及第一电容器的第二端子电联接至第一栅极驱动器电路的接地端子,以及其中第一电阻器的第一端子电联接至第二栅极驱动器电路的启用端子,且第一电阻器的第二端子电联接至第一栅极驱动器电路的接地端子。栅极驱动器装置还可包括:第二保持活动电路,包括第二二极管、第二电容器和第二电阻器,其中第二二极管的第一端子电联接至第三栅极驱动器电路的输出端子,并且第二二极管的第二端子电联接至第三栅极驱动器电路的启用端子,其中第二电容器的第一端子电联接至第四栅极驱动器电路的启用端子,以及第二电容器的第二端子电联接至第四栅极驱动器电路的接地端子,以及其中第二电阻的第一端子电联接至第四栅极驱动器电路的启用端子,且第二电阻的第二端子电联接至第四栅极驱动器电路的接地端子。

6、栅极驱动器装置还可包括:第一变压器,包括初级线圈和次级线圈,初级线圈电联接至输入到栅极驱动器装置的信号和第一栅极驱动器电路的启用端子,次级线圈电联接至第三栅极驱动器电路的启用端子;以及第二变压器,包括初级线圈和次级线圈,初级线圈电联接至第二栅极驱动器电路的输出端子,次级线圈电联接至输出第二驱动信号的第二节点。

7、栅极驱动器装置还可包括:正向转换器动力系,包括变压器、主晶体管、有源复位晶体管、正向同步晶体管和捕获同步晶体管,其中变压器包括初级线圈和次级线圈,其中主晶体管的漏极端子电联接至变压器的初级线圈的第一端子,主晶体管的源极端子电联接至基准电势,以及主晶体管的栅极端子电联接至输出第一驱动信号的第一节点,其中有源复位晶体管的漏极端子电联接至变压器的初级线圈的第二端子,有源复位晶体管的源极端子电联接至变压器的初级线圈的第一端子,并且有源复位晶体管的栅极端子电联接至输出第二驱动信号的第二节点,其中,正向同步晶体管的漏极端子电联接至变压器的次级线圈的第一端子,并且正向同步晶体管的栅极端子电联接至输出第三驱动信号的第三节点,并且其中,捕获同步晶体管的漏极端子电联接至变压器的次级线圈的第二端子,捕获同步晶体管的源极端子电联接至正向同步晶体管的源极端子,以及捕获同步晶体管的栅极端子电联接至输出第四驱动信号的第四节点。主晶体管、有源复位晶体管、正向同步晶体管和捕获同步晶体管中的每一个均可为相同类型的晶体管。

8、第一栅极驱动器电路和第二栅极驱动器电路可包括于第一集成电路芯片中设置的第一集成逻辑驱动器中,并且第三栅极驱动器电路和第四栅极驱动器电路可包括于第二集成电路芯片中设置的第二集成逻辑驱动器中。

9、一种栅极驱动器装置基于输入到根据本发明的栅极驱动器装置的信号而输出多个驱动信号,其特征在于,包括:第一栅极驱动器电路,包括输入端子、启用端子和输出端子,其中第一栅极驱动器电路的输出端子处的电压电平取决于第一栅极驱动器电路的输入端子处的电压电平和第一栅极驱动器电路的启用端子处的电压电平,以及其中第一栅极驱动器电路的输出端子电联接至输出第一驱动信号的第一节点;第二栅极驱动器电路,包括输入端子、启用端子和输出端子,其中第二栅极驱动器电路的输出端子处的电压电平取决于第二栅极驱动器电路的输入端子处的电压电平和第二栅极驱动器电路的启用端子处的电压电平,并且其中第二栅极驱动器电路的输出端子电联接至输出第二驱动信号的第二节点;第三栅极驱动器电路,包括输入端子、启用端子和输出端子,其中第三栅极驱动器电路的输出端子的电压电平取决于第三栅极驱动器电路的输入端子的电压电平和第三栅极驱动器电路的启用端子的电压电平,并且其中第三栅极驱动器电路的输出端子电联接至输出第三驱动信号的第三节点;第四栅极驱动器电路,包括输入端子、启用端子和输出端子,其中第四栅极驱动器电路的输出端子处的电压电平取决于第四栅极驱动器电路的输入端子处的电压电平和第四栅极驱动器电路的启用端子处的电压电平,并且其中第四栅极驱动器电路的输出端子电联接至输出第四驱动信号的第四节点;第一保持活动电路,包括第一二极管、第一电容器和第一电阻器,其中第一二极管的第一端子电联接至第一栅极驱动器电路的输出端子,并且第一二极管的第二端子电联接至第二栅极驱动器电路的启用端子,其中第一电容器的第一端子电联接至第二栅极驱动器电路的启用端子,以及第一电容器的第二端子电联接至第二栅极驱动器电路的接地端子,以及其中第一电阻器的第一端子电联接至第二栅极驱动器电路的启用端子,以及第一电阻器的第二端子电联接至第二栅极驱动器电路的接地端子;以及第二保持活动电路,包括第二二极管、第二电容器和第二电阻器,其中第二二极管的第一端子电联接至第三栅极驱动器电路的输出端子,并且第二二极管的第二端子电联接至第四栅极驱动器电路的启用端子,其中第二电容器的第一端子电联接至第四栅极驱动器电路的启用端子,以及第二电容器的第二端子电联接至第四栅极驱动器电路的接地端子,以及其中第二电阻的第一端子电联接至第四栅极驱动器电路的启用端子,以及第二电阻的第二端子电联接至第四栅极驱动器电路的接地端子。

10、第一栅极驱动器电路的输出端子可电联接至第二栅极驱动器电路的输入端子,第二栅极驱动器电路的输出端子可电联接至第一栅极驱动器电路的输入端子,第三栅极驱动器电路的输出端子可电联接至第四栅极驱动器电路的输入端子,并且第四栅极驱动器电路的输出端子可电联接至第三栅极驱动器电路的输入端子。

11、栅极驱动器装置还可包括:第一变压器,包括初级线圈和次级线圈,初级线圈电联接至输入到栅极驱动器装置的信号和第一栅极驱动器电路的启用端子,次级线圈电联接至第三栅极驱动器电路的启用端子;以及第二变压器,包括初级线圈和次级线圈,初级线圈电联接至第二栅极驱动器电路的输出端子,以及次级线圈电联接至输出第二驱动信号的第二节点。

12、栅极驱动器装置还可包括:正向转换器动力系,包括变压器、主晶体管、有源复位晶体管、正向同步晶体管和捕获同步晶体管,其中变压器包括初级线圈和次级线圈,其中主晶体管的漏极端子电联接至变压器的初级线圈的第一端子,主晶体管的源极端子电联接至基准电势,以及主晶体管的栅极端子电联接至输出第一驱动信号的第一节点,其中有源复位晶体管的漏极端子电联接至变压器的初级线圈的第二端子,有源复位晶体管的源极端子电联接至变压器的初级线圈的第一端子,以及有源复位晶体管的栅极端子电联接至输出第二驱动信号的第二节点,其中,正向同步晶体管的漏极端子电联接至变压器的次级线圈的第一端子,并且正向同步晶体管的栅极端子电联接至输出第三驱动信号的第三节点,并且其中,捕获同步晶体管的漏极端子电联接至变压器的次级线圈的第二端子,捕获同步晶体管的源极端子电联接至正向同步晶体管的源极端子,以及捕获同步晶体管的栅极端子电联接至输出第四驱动信号的第四节点。主晶体管、源复位晶体管、正向同步晶体管和捕获同步晶体管中的每一个均可为相同类型的晶体管。

13、一种操作根据本发明的栅极驱动器装置的方法,其特征在于,包括:向第一栅极驱动器电路提供输入信号,第一栅极驱动器电路包括输入端子、启用端子和输出端子,其中输入信号被提供给第一栅极驱动器电路的启用端子,其中第一栅极驱动器电路的输出端子处的电压电平取决于第一栅极驱动器电路的输入端子处的电压电平和第一栅极驱动器电路的启用端子处的电压电平,其中第一栅极驱动器电路的输出端子电联接至包括输入端子、启用端子和输出端子的第二栅极驱动器电路,其中第一栅极驱动器电路的输出端子电联接至第二栅极驱动器电路的启用端子,其中第二栅极驱动器电路的输出端子处的电压电平取决于第二栅极驱动器电路的输入端子处的电压电平和第二栅极驱动器电路的启用端子处的电压电平,其中第二栅极驱动器电路的输出端子电联接至第一栅极驱动器电路的输入端子,其中第一栅极驱动器电路的输出端子电联接至第一节点,以及其中第二栅极驱动器电路的输出端子电联接至第二节点;从第一节点输出第一驱动信号;从第二节点输出第二驱动信号;将输入信号提供给包括输入端子、启用端子和输出端子的第三栅极驱动器电路,其中输入信号被提供给第三栅极驱动器电路的启用端子,其中第三栅极驱动器电路的输出端子的电压电平取决于第三栅极驱动器电路的输入端子的电压电平和第三栅极驱动器电路的启用端子的电压电平,其中第三栅极驱动器电路的输出端子电联接至第四栅极驱动器电路,第四栅极驱动器电路包括输入端子、启用端子和输出端子,其中第三栅极驱动器电路的输出端子电联接至第四栅极驱动器电路的输入端子,其中第四栅极驱动器电路的输出端子处的电压电平取决于第四栅极驱动器电路的输入端子处的电压电平和第四栅极驱动器电路的启用端子处的电压电平,其中,第四栅极驱动器电路的输出端子电联接至第三栅极驱动器电路的输入端子,其中第三栅极驱动器电路的输出端子电联接至第三节点,并且其中第四栅极驱动器电路的输出端子电联接至第四节点;从第三节点输出第三驱动信号;以及从第四节点输出第四驱动信号。

14、该方法还可包括:使第一栅极驱动器电路的输出端子具有第一电压电平或大于第一电压电平的第二电压电平,包括使第一栅极驱动器电路的输出端子具有第一电压电平,除非第一栅极驱动器电路的启用端子具有第二电压电平,并且第一栅极驱动器电路的输入端子同时具有第一电压电平;使第二栅极驱动器电路的输出端子具有第一电压电平或第二电压电平,包括使第二栅极驱动器电路的输出端子具有第一电压电平,除非第二栅极驱动器电路的启用端子具有第二电压电平,且第二栅极驱动器电路的输入端子同时具有第一电压电平;使第三栅极驱动器电路的输出端子具有第一电压电平或第二电压电平,包括使第三栅极驱动器电路的输出端子具有第一电压电平,除非第三栅极驱动器电路的启用端子具有第二电压电平,且第三栅极驱动器电路的输入端子同时具有第一电压电平;以及使第四栅极驱动器电路的输出端子具有第一电压电平或第二电压电平,包括使第四栅极驱动器电路的输出端子具有第一电压电平,除非第四栅极驱动器电路的启用端子具有第二电压电平,且第四栅极驱动器电路的输入端子同时具有第一电压电平。

15、第一驱动信号可具有第一电压电平,而第二驱动信号具有不同于第一电压电平的第二电压电平。第一驱动信号可具有第二电压电平,而第二驱动信号具有第一电压电平。第三驱动信号可具有第一电压电平,而第四驱动信号具有第二电压电平。第三驱动信号可具有第二电压电平,而第四驱动信号具有第一电压电平。第一驱动信号可具有第一电压电平,而第二驱动信号具有不同于第一电压电平的第二电压电平,第一驱动信号可具有第二电压电平,而第二驱动信号具有第一电压电平,第三驱动信号可具有第一电压电平,而第四驱动信号具有第二电压电平,并且第三驱动信号可具有第二电压电平,而第四驱动信号具有第一电压电平。

- 还没有人留言评论。精彩留言会获得点赞!