高频交流母线型电能路由器的多端解耦控制方法及装置

1.本技术涉及电力系统配电网技术领域,特别涉及一种高频交流母线型电能路由器的多端解耦控制方法及装置。

背景技术:

2.大量分布式可再生能源的入网,要求传统配电网具备更好的稳定性与更高的灵活度。采用新型电力电子技术的电能路由器,具有灵活的调配与控制能力,可用于对当前“源-网-荷-储”一体的新型电力系统协调优化。此外,电能路由器还具备多端口、多级联、多流向与多形态的功能特性,能够实现端口电气隔离与复杂电能变换。

3.相关技术中对现有的基于高频交流母线的四端口电能路由器的拓扑与控制进行了分析,相比于传统直流母线型电能路由器,现有的高频母线电能路由器具有更少的电能变换单元,具备更高的功率密度。高频母线型电能路由器的核心为模块化多有源桥,当下其各个端口均采用单移相控制。在单移相控制下,各端口对于工况变换的暂态响应速度较慢。

技术实现要素:

4.本技术提供一种高频交流母线型电能路由器的多端解耦控制方法及装置,以解决在各个端口均采用单移相控制下,各端口对于工况变换的暂态响应速度较慢的问题。

5.本技术第一方面实施例提供一种高频交流母线型电能路由器的多端解耦控制方法,所述高频交流母线型电能路由器包括通过高频母线相连的多个功率子模块,所述多个功率子模块通过级联或并联的方式组成多电压等级和多功率等级的多个直流端口,所述多端解耦控制方法包括以下步骤:利用50%占空比的移相调制方式对所述多个直流端口进行调制,且直流端口的全桥结构中同一桥臂的器件开关信号互反;采样所述高频母线电压和所述高频母线电流,将所述高频母线视为电压源,对所述多个直流端口的拓扑结构进行简化,将所述直流端口内部的模块化多有源桥拆分为多个端口子系统,进行结构解耦;建立微分算子、所述高频母线电压、高频电感电流和高频电感关系的回路电压方程,对所述回路电压方程进行变换后去除高频分量,并加入锁相环,令所述高频母线电压的q轴分量为零,得到所述高频母线电压的d轴分量,对所述高频电感电流作park变换,得到所述高频电感电流的dq轴电流分量,在所述高频母线电压的d轴分量和所述高频电感电流的dq轴电流分量中加入pi控制,得到所述直流端口的dq轴电压分量。

6.可选地,在本技术的一个实施例中,所述高频母线电压为各个直流端口交流输出电压的叠加值。

7.可选地,在本技术的一个实施例中,所述高频母线电压为:

[0008][0009]

其中,v

sk

为端口k向高频母线侧输出的三电平交流电压,lk为端口k的电感系数,n为直流的端口数,vk为端口k的直流电压稳定值,ωs为开关角频率,αk为直流端口k的内移相

角,βk为直流端口k的外移相角。

[0010]

可选地,在本技术的一个实施例中,所述直流端口的内移相角为所述直流端口中的开关信号相位差,第一直流端口的内移相角中点为相位零点,除所述第一直流端口外的直流端口的内移相角中点滞后于相位零点的相位为对应直流端口的外移相角。

[0011]

可选地,在本技术的一个实施例中,所述回路电压方程为:

[0012]vs

=v

h-pli

l

[0013]

其中,p为微分算子,vh为高频母线电压,l为电感,i

l

为高频母线电感电流。

[0014]

可选地,在本技术的一个实施例中,所述直流端口的dq轴电压分量为:

[0015][0016]

其中,i

ld

为电感电流d轴分量,i

lq

为电感电流q轴分量,v

hd

为高频母线电压基波幅值d轴分量,v

hq

为高频母线电压基波幅值q轴分量,k

p

为电流pi控制器的比例系数,ki为电流pi控制器的积分系数。

[0017]

本技术第二方面实施例提供一种高频交流母线型电能路由器的多端解耦控制装置,所述高频交流母线型电能路由器包括通过高频母线相连的多个功率子模块,所述多个功率子模块通过级联或并联的方式组成多电压等级和多功率等级的多个直流端口,所述多端解耦控制装置包括:调制模块,用于利用50%占空比的移相调制方式对所述多个直流端口进行调制,且直流端口的全桥结构中同一桥臂的器件开关信号互反;采样模块,用于采样所述高频母线电压和所述高频母线电流,将所述高频母线视为电压源,对所述多个直流端口的拓扑结构进行简化,将所述直流端口内部的模块化多有源桥拆分为多个端口子系统,进行结构解耦;控制模块,用于建立微分算子、所述高频母线电压、高频电感电流和高频电感关系的回路电压方程,对所述回路电压方程进行变换后去除高频分量,并加入锁相环,令所述高频母线电压的q轴分量为零,得到所述高频母线电压的d轴分量,对所述高频电感电流作park变换,得到所述高频电感电流的dq轴电流分量,在所述高频母线电压的d轴分量和所述高频电感电流的dq轴电流分量中加入pi控制,得到所述直流端口的dq轴电压分量。

[0018]

可选地,在本技术的一个实施例中,所述高频母线电压为各个直流端口交流输出电压的叠加值。

[0019]

本技术第三方面实施例提供一种电子设备,包括:存储器、处理器及存储在所述存储器上并可在所述处理器上运行的计算机程序,所述处理器执行所述程序,以执行如上述实施例所述的高频交流母线型电能路由器的多端解耦控制方法。

[0020]

本技术第四方面实施例提供一种计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行,以执行如上述实施例所述的高频交流母线型电能路由器的多端解耦控制方法。

[0021]

本技术实施例的高频交流母线型电能路由器的多端解耦控制方法及装置,通过采集高频母线信息,使得各端口能够实现解耦控制,不再依赖于全体的具体控制参数;并且能在各端口工况变化时,使得模块化多有源桥具备更好的暂态特性,提升系统的稳定性。由此,解决了在各个端口均采用单移相控制下,各端口对于工况变换的暂态响应速度较慢的

问题。

[0022]

本技术附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本技术的实践了解到。

附图说明

[0023]

本技术上述的和/或附加的方面和优点从下面结合附图对实施例的描述中将变得明显和容易理解,其中:

[0024]

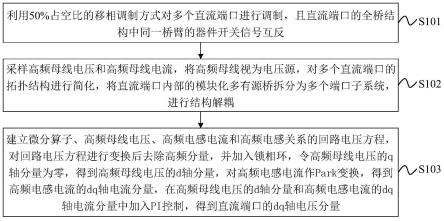

图1为根据本技术实施例提供的一种高频交流母线型电能路由器的多端解耦控制方法的流程图;

[0025]

图2为根据本技术实施例提供的一种多端口高频交流母线型电能路由器的拓扑结构图;

[0026]

图3为根据本技术实施例提供的一种多端口高频交流母线型电能路由器的单个直流端口的等效结构图;

[0027]

图4为根据本技术实施例提供的一种高频物理量的选频滤波流程图;

[0028]

图5为根据本技术实施例提供的一种pi控制策略框图;

[0029]

图6为传统单移相控制实施例中各端口全桥输出电压vs和电感电流i

l

的暂态波形图;

[0030]

图7为根据本技术实施例各端口全桥输出电压vs和电感电流i

l

暂态波形图;

[0031]

图8为根据本技术实施例各端口全桥输出电压vs和电感电流i

l

在工况一稳态下的细节波形图;

[0032]

图9为根据本技术实施例各端口全桥输出电压vs和电感电流i

l

在工况二稳态下的细节波形图;

[0033]

图10为根据本技术实施例的高频交流母线型电能路由器的多端解耦控制装置的示例图;

[0034]

图11为申请实施例提供的电子设备的结构示意图。

具体实施方式

[0035]

下面详细描述本技术的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,旨在用于解释本技术,而不能理解为对本技术的限制。

[0036]

图1为根据本技术实施例提供的一种高频交流母线型电能路由器的多端解耦控制方法的流程图。

[0037]

如图1所示,该高频交流母线型电能路由器的多端解耦控制方法包括以下步骤:

[0038]

在步骤s101中,利用50%占空比的移相调制方式对多个直流端口进行调制,且直流端口的全桥结构中同一桥臂的器件开关信号互反。

[0039]

如图2所示,展示了基于高频母线的电能路由器核心级模块化多有源桥的拓扑,高频交流母线型电能路由器包括通过高频母线相连的多个功率子模块,多个功率子模块通过级联或并联的方式组成多电压等级和多功率等级的多个直流端口。其中,功率子模块包括直流电容、全桥结构的功率半导体器件以及带漏感的高频变压器。各直流端口由高频变压

器实现电气隔离,且端口数量不受限制。部分直流端口可通过前级整流或后级逆变的方式接入交流电网或交流负载,以此形成多电压等级与多电压形态的电能路由器。

[0040]

为了解决相关技术中在各个端口均采用单移相控制下,各端口对于工况变换的暂态响应速度较慢的问题。基于频域理论,本技术对各直流端口采用50%占空比的移相调制方式,全桥结构中同一桥臂的器件开关信号互反。

[0041]

在步骤s102中,采样高频母线电压和高频母线电流,将高频母线视为电压源,对多个直流端口的拓扑结构进行简化,将直流端口内部的模块化多有源桥拆分为多个端口子系统,进行结构解耦。

[0042]

在本技术的实施例中,s1与s4的开关信号相位差为该直流端口的内移相角α。设端口1的内移相角中点为相位零点,其余端口的内移相角中点滞后于相位零点的相位为该直流端口的外移相角β。假设端口的直流电压为稳定值v,端口向高频母线侧输出三电平准方波,设ωs为开关角频率,端口i向高频母线侧输出的三电平电压可表示为:

[0043][0044]

定义端口i的电感系数为:

[0045][0046]

高频母线电压可以表示为多电平方波:

[0047][0048]

其中,v

sk

为端口k向高频母线侧输出的三电平交流电压,lk为端口k的电感系数,n为直流的端口数,vk为端口k的直流电压稳定值,ωs为开关角频率,αk为直流端口k的内移相角,βk为直流端口k的外移相角。

[0049]

将高频母线视为方波电压源,则对于任意端口,其拓扑可以简化为图3所示。该等效结构将模块化多有源桥拆分为多个端口子系统,在认为高频母线电压为源的情况下,各个系统不与其它系统产生交互,可等效视为结构解耦。

[0050]

在步骤s103中,建立微分算子、高频母线电压、高频电感电流和高频电感关系的回路电压方程,对回路电压方程进行变换后去除高频分量,并加入锁相环,令高频母线电压的q轴分量为零,得到高频母线电压的d轴分量,对高频电感电流作park变换,得到高频电感电流的dq轴电流分量,在高频母线电压的d轴分量和高频电感电流的dq轴电流分量中加入pi控制,得到直流端口的dq轴电压分量。

[0051]

设p为微分算子,建立回路电压方程:

[0052]vs

=v

h-pli

l

(4)

[0053]

根据式(3),不妨设高频母线电压为:

[0054]

vh(t)=vhsin(ωst-βh)+o[sinωst](5)

[0055]

其中,vh为高频母线电压基波幅值,βh为其基波相位。同理,设i

l

为高频电感电流基波幅值,β

l

为其基波相位,高频电感电流可表示为:

[0056]il

(t)=i

l

sin(ωst-β

l

)+o[sinωst](6)

[0057]

其中。在只考虑各物理量基波分量的情况下,式(4)可表示为:

[0058][0059]

如图4所示,将(7)两边同乘2sinωst,有:

[0060][0061]

滤除掉高频分量,式(8)为:

[0062][0063]

同理,将(7)两边同乘-2cosωst,再滤除掉高频分量,有:

[0064][0065]

对(9)与(10)作以下定义:

[0066][0067]

综上,有:

[0068][0069]

加入锁相环,令高频母线电压vh的q轴分量为零,有:

[0070][0071]

对高频电感电流作park变换,得到dq轴电流分量:

[0072][0073]

加入pi控制器,则有:

[0074][0075]

设计双闭环控制器,控制结构如图5所示。

[0076]

下面通过具体实施例和附图6-9对本技术的高频交流母线型电能路由器的多端解耦控制方法进行箱子说明。

[0077]

基于图2所示的一种四端口高频母线型电能路由器,采用rtlab实时仿真平台进行验证。其中端口1为松弛端口,接入直流电源,其余端口均为功率端口,接入直流负载或电源。仿真参数如表1所示。

[0078]

表1仿真参数

[0079]

实验参数参数值实验参数参数值端口1直流电源电压700v端口2直流电源电压750v端口3直流电源电压750v端口4直流电压参考值750v

[0080]

实验工况一:端口2的直流输入电流25a,端口3的直流输入电流25a,端口4的直流负载30ω。各端口功率均为18.75kw。实验结果如图8所示。

[0081]

实验工况二:端口2的直流输入电流25a,端口3的直流输入电流-25a,端口4的直流负载30ω。端口2和端口4功率为18.75kw,端口3功率为-18.75kw。实验结果如图9所示。

[0082]

具体实验中,由实验工况一调整至实验工况二。由图6和图7可见,相比于单移相控制,本发明提出的多端口解耦控制具备更好的暂态特性。

[0083]

根据本技术实施例提出的高频交流母线型电能路由器的多端解耦控制方法,通过采集高频母线信息,使得各端口能够实现解耦控制,不再依赖于全体的具体控制参数;并且能在各端口工况变化时,使得模块化多有源桥具备更好的暂态特性,提升系统的稳定性。由此,解决了在各个端口均采用单移相控制下,各端口对于工况变换的暂态响应速度较慢的问题。

[0084]

其次参照附图描述根据本技术实施例提出的高频交流母线型电能路由器的多端解耦控制装置。

[0085]

图10为根据本技术实施例的高频交流母线型电能路由器的多端解耦控制装置的示例图。

[0086]

如图10所示,高频交流母线型电能路由器包括通过高频母线相连的多个功率子模块,多个功率子模块通过级联或并联的方式组成多电压等级和多功率等级的多个直流端口,多端解耦控制装置10包括:调制模块100、采样模块200和控制模块300。

[0087]

其中,调制模块100,用于利用50%占空比的移相调制方式对多个直流端口进行调制,且直流端口的全桥结构中同一桥臂的器件开关信号互反。采样模块200,用于采样所述高频母线电压和所述高频母线电流,将高频母线视为电压源,对多个直流端口的拓扑结构进行简化,将直流端口内部的模块化多有源桥拆分为多个端口子系统,进行结构解耦;控制模块300,用于建立微分算子、高频母线电压、高频电感电流和高频电感关系的回路电压方程,对回路电压方程进行变换后去除高频分量,并加入锁相环,令高频母线电压的q轴分量为零,得到高频母线电压的d轴分量,对高频电感电流作park变换,得到高频电感电流的dq轴电流分量,在高频母线电压的d轴分量和高频电感电流的dq轴电流分量中加入pi控制,得到直流端口的dq轴电压分量。

[0088]

可选地,在本技术的一个实施例中,高频母线电压为各个直流端口交流输出电压的叠加值。

[0089]

可选地,在本技术的一个实施例中,高频母线电压为:

[0090][0091]

其中,v

sk

为端口k向高频母线侧输出的三电平交流电压,lk为端口k的电感系数,n为直流的端口数,vk为端口k的直流电压稳定值,ωs为开关角频率,αk为直流端口k的内移相角,βk为直流端口k的外移相角。

[0092]

可选地,在本技术的一个实施例中,直流端口的内移相角为直流端口中的开关信号相位差,第一直流端口的内移相角中点为相位零点,除第一直流端口外的直流端口的内移相角中点滞后于相位零点的相位为对应直流端口的外移相角。

[0093]

可选地,在本技术的一个实施例中,回路电压方程为:

[0094]vs

=v

h-pli

l

[0095]

其中,p为微分算子,vh为高频母线电压,l为电感,i

l

为高频母线电感电流。

[0096]

可选地,在本技术的一个实施例中,直流端口的dq轴电压分量为:

[0097][0098]

其中,i

ld

为电感电流d轴分量,i

lq

为电感电流q轴分量,v

hd

为高频母线电压基波幅值d轴分量,v

hq

为高频母线电压基波幅值q轴分量,k

p

为电流pi控制器的比例系数,ki为电流pi控制器的积分系数。

[0099]

需要说明的是,前述对高频交流母线型电能路由器的多端解耦控制方法实施例的解释说明也适用于该实施例的高频交流母线型电能路由器的多端解耦控制装置,此处不再赘述。

[0100]

根据本技术实施例提出的高频交流母线型电能路由器的多端解耦控制装置,通过采集高频母线信息,使得各端口能够实现解耦控制,不再依赖于全体的具体控制参数;并且能在各端口工况变化时,使得模块化多有源桥具备更好的暂态特性,提升系统的稳定性。由此,解决了在各个端口均采用单移相控制下,各端口对于工况变换的暂态响应速度较慢的问题。。

[0101]

图11为本技术实施例提供的电子设备的结构示意图。该电子设备可以包括:

[0102]

存储器1101、处理器1102及存储在存储器1101上并可在处理器1102上运行的计算机程序。

[0103]

处理器1102执行程序时实现上述实施例中提供的高频交流母线型电能路由器的多端解耦控制方法。

[0104]

进一步地,电子设备还包括:

[0105]

通信接口1103,用于存储器1101和处理器1102之间的通信。

[0106]

存储器1101,用于存放可在处理器1102上运行的计算机程序。

[0107]

存储器1101可能包含高速ram存储器,也可能还包括非易失性存储器(non-volatile memory),例如至少一个磁盘存储器。

[0108]

如果存储器1101、处理器1102和通信接口1103独立实现,则通信接口1103、存储器

1101和处理器1102可以通过总线相互连接并完成相互间的通信。总线可以是工业标准体系结构(industry standard architecture,简称为isa)总线、外部设备互连(peripheral component,简称为pci)总线或扩展工业标准体系结构(extended industry standard architecture,简称为eisa)总线等。总线可以分为地址总线、数据总线、控制总线等。为便于表示,图11中仅用一条粗线表示,但并不表示仅有一根总线或一种类型的总线。

[0109]

可选的,在具体实现上,如果存储器1101、处理器1102及通信接口1103,集成在一块芯片上实现,则存储器1101、处理器1102及通信接口1103可以通过内部接口完成相互间的通信。

[0110]

处理器1102可能是一个中央处理器(central processing unit,简称为cpu),或者是特定集成电路(application specific integrated circuit,简称为asic),或者是被配置成实施本技术实施例的一个或多个集成电路。

[0111]

本实施例还提供一种计算机可读存储介质,其上存储有计算机程序,其特征在于,该程序被处理器执行时实现如上的高频交流母线型电能路由器的多端解耦控制方法。

[0112]

在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本技术的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任一个或n个实施例或示例中以合适的方式结合。此外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。

[0113]

此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。在本技术的描述中,“n个”的含义是至少两个,例如两个,三个等,除非另有明确具体的限定。

[0114]

流程图中或在此以其他方式描述的任何过程或方法描述可以被理解为,表示包括一个或更n个用于实现定制逻辑功能或过程的步骤的可执行指令的代码的模块、片段或部分,并且本技术的优选实施方式的范围包括另外的实现,其中可以不按所示出或讨论的顺序,包括根据所涉及的功能按基本同时的方式或按相反的顺序,来执行功能,这应被本技术的实施例所属技术领域的技术人员所理解。

[0115]

应当理解,本技术的各部分可以用硬件、软件、固件或它们的组合来实现。在上述实施方式中,n个步骤或方法可以用存储在存储器中且由合适的指令执行系统执行的软件或固件来实现。如,如果用硬件来实现和在另一实施方式中一样,可用本领域公知的下列技术中的任一项或他们的组合来实现:具有用于对数据信号实现逻辑功能的逻辑门电路的离散逻辑电路,具有合适的组合逻辑门电路的专用集成电路,可编程门阵列(pga),现场可编程门阵列(fpga)等。

[0116]

本技术领域的普通技术人员可以理解实现上述实施例方法携带的全部或部分步骤是可以通过程序来指令相关的硬件完成,所述的程序可以存储于一种计算机可读存储介质中,该程序在执行时,包括方法实施例的步骤之一或其组合。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1