一种自适应SiC-MOSFET管并联均流的控制电路及控制方法与流程

一种自适应sic-mosfet管并联均流的控制电路及控制方法

技术领域

1.本发明属于电力电子功率器件应用的技术领域,具体而言,涉及一种自适应sic-mosfet管并联均流的控制电路及控制方法。

背景技术:

2.随着电力电子技术的飞速发展,电力电子应用领域对电压等级和容量等级的需求越来越多,诸如各种变换器,各种电机驱动系统,采用单个分立式sic-mosfet管的通流能力有限,无法满足较大功率的设备需求,故一般情况下会采用对sic-mosfet管并联的方式进行扩容,以满足这些场合的应用。

3.sic-mosfet器件特征参数差异性对其并联均流特性影响较大,电流不均衡会导致sic-mosfet管的导通损耗和开关损耗分配不均衡,进而会导致部分器件过热。另外,瞬态电流不均衡还会使器件的电流尖峰过大,很可能超出器件的安全工作区,影响电路的可靠性,因此,解决sic-mosfet管的均流问题对于其并联以扩大功率等级有着重要的意义,本发明提出对于采用的sic-mosfet管组成并联电路均流控制技术,尤其是一种自适应sic-mosfet管并联均流控制技术。

技术实现要素:

4.鉴于此,为了解决现有技术存在的上述问题,本发明的目的在于提供一种自适应sic-mosfet管并联均流的控制电路及控制方法以达到对并联电路进行自适应均流控制的目的。

5.本发明所采用的技术方案为:一种自适应sic-mosfet管并联均流的控制电路,该控制电路包括:sic-mosfet管并联电路,该该控制电路还包括:高速单片机;分别与sic-mosfet管并联电路中各路sic-mosfet管对应的栅极驱动电路,各所述栅极驱动电路分别通过vgs电压控制电路与高速单片机之间通信连接;分别与sic-mosfet管并联电路中各路sic-mosfet管对应的电流采集电路,各所述电流采集电路分别通过信号调理电路与高速单片机之间通信连接;其中,通过vgs电压控制电路对并联sic-mosfet管的各栅源电压vgs进行调节,以实现并联sic-mosfet管的均流控制。

6.进一步地,各所述栅极驱动电路分别电连接有vgs延迟电路,且vgs延迟电路与高速单片机之间通信连接,以进一步控制每个sic-mosfet管的栅极加载电压延迟时间,达到解决并联sic-mosfet管因器件参数不一致所造成的不均流问题。

7.进一步地,所述栅极驱动电路至少包括:驱动芯片,所述驱动芯片与对应sic-mosfet管的栅极电连接,且该sic-mosfet管对应的vgs电压控制电路和vgs延迟电路分别与驱动芯片之间电连接。采用ucc5350mc驱动芯片具有米勒钳位功能,可防止sic-mosfet管误

开通,米勒钳位功能主要通过采样栅极的电压并与阈值电压相比较,当栅极电压低于阈值电压后比较器反转,使得内置的米勒钳位导通,形成一条低导通阻抗的路径,这条低阻抗路径可以将sic-mosfet管的栅极关断,从而避免误导通。

8.进一步地,所述vgs延迟电路至少包括:与高速单片机通信连接的触发器,所述触发器的pwm信号端与驱动芯片之间通信连接,以达到控制输出pwm1信号和pwm2信号两者之间的时间差,进一步可以控制后级sic-mosfet管的栅极驱动信号上升沿延迟时间;所述vgs电压控制电路至少包括:与高速单片机通信连接的降压变换器,所述降压变换器的vcc输出端与驱动芯片之间电连接,通过i2c接口实现采用软件调整其输出的电压,可以配置操作参数,即采用mcu的i2c接口控制的集成降压变换器的输出vcc。

9.进一步地,所述sic-mosfet管的源极经电流采样电阻串联接地;所述电流采集电路包括:差分放大器,所述差分放大器的两个输入端分别连接至电流采样电阻的两端,差分放大器的输出端与信号调理电路之间电连接。

10.进一步地,所述信号调理电路包括:同相放大电路和低通滤波器,所述差分放大器的输出端依次经同相放大电路和低通滤波器串联至高速单片机;该信号调理电路可对各sic-mosfet管的电流检测输出信号再次进行调理,使其适合mcu的adc输入范围。

11.进一步地,所述单片机连接有rs-232接口,通过该rs-232接口与外部pc机之间通信,以实现外部pc机与mcu通信,利用配置软件可对各种参数进行采集以及调整。

12.在本发明中还提供了一种自适应sic-mosfet管并联均流的控制方法,该控制方法基于上述所述的自适应sic-mosfet管并联均流的控制电路,该控制方法包括:s1:对sic-mosfet管并联电路中各个sic-mosfet管的稳态工作电流ids进行实时采集;s2:对采集的稳态工作电流ids经信号调理至adc采样范围;s3:将adc采样范围内的信号输入至高速单片机进行判断比较;s4:通过高速单片机对并联sic-mosfet管的各栅源电压vgs进行控制,以实现并联sic-mosfet管的均流控制。

13.进一步地,在s1中,通过高速单片机切换各个sic-mosfet管所对应栅极驱动的通断,以对各个sic-mosfet管的稳态工作电流ids进行轮流采集。

14.进一步地,在s4中,还包括:高速单片机控制触发器输出具有时间差的栅极驱动信号,通过sic-mosfet管并联电路中sic-mosfet管所对应栅极驱动信号的上升沿延迟,实现各路sic-mosfet管的电流均衡。

15.本发明的有益效果为:采用本发明所提供的自适应sic-mosfet管并联均流的控制电路及控制方法,该控制电路一方面通过对并联sic-mosfet管的工作电流ids进行判断比较,以对并联sic-mosfet管的栅极电压vgs进行调整,进而达到从静态控制实现各路并联sic-mosfet管的电流均流;另一方面,控制各路sic-mosfet管的pwm信号产生时间差,以解决由于各sic-mosfet管的栅源阈值电压ugs(th)不一致所导致的不均流问题,从动态控制实现各路并联sic-mosfet管的电流均流。

附图说明

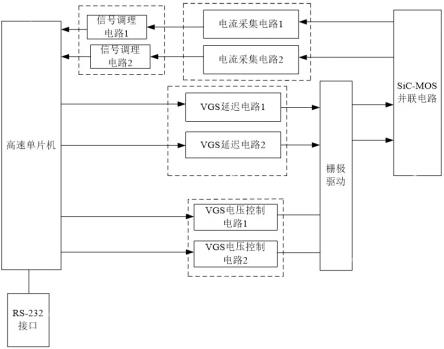

16.图1是自适应sic-mosfet管并联均流的控制电路的整体电路架构图;图2是自适应sic-mosfet管并联均流的控制电路中栅极驱动的电路原理图;图3a是自适应sic-mosfet管并联均流的控制电路中vgs电压控制电路的第一部分原理图;图3b是自适应sic-mosfet管并联均流的控制电路中vgs电压控制电路的第二部分原理图;图4是自适应sic-mosfet管并联均流的控制电路中vgs与rds(on)的曲线关系图;图5是自适应sic-mosfet管并联均流的控制电路中均流过程中各项参数的曲线关系图;图6是自适应sic-mosfet管并联均流的控制电路中电流采集电路的原理图;图7是自适应sic-mosfet管并联均流的控制电路中信号调理电路的原理图;图8是自适应sic-mosfet管并联均流的控制电路中vgs延迟电路的原理图;图9是自适应sic-mosfet管并联均流的控制电路中pwm信号曲线图。

实施方式

17.下面详细描述本技术的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的模块或具有相同或类似功能的模块。下面通过参考附图描述的实施例是示例性的,仅用于解释本技术,而不能理解为对本技术的限制。相反,本技术的实施例包括落入所附加权利要求书的精神和内涵范围内的所有变化、修改和等同物。

18.实施例1在本实施例中具体提供了一种自适应sic-mosfet管并联均流的控制电路,该控制电路旨在实现sic-mosfet管并联电路中各路sic-mosfet管的电流均衡,以提高sic-mosfet管的使用稳定性,减少sic-mosfet管的器件损伤。

19.因此,如图1所示,该控制电路是基于sic-mosfet管并联电路所实现其相应功能的,该该控制电路主要包括:高速单片机,所述高速单片机由mcu

‑ⅰ

(u1a)、mcu

‑ⅱ

(u1b)和mcu

‑ⅲ

(u1c)三部分组成。

20.在sic-mosfet管并联电路中有两路sic-mosfet管,分别为sic-mosfet管q8和sic-mosfet管q9,该sic-mosfet管(型号为:ceb25m120pr4)为to247-4pin的开尔文结构且sic-mosfet管的开尔文极接地,sic-mosfet管的源极接电流采样电阻并实现开尔文极与源极彼此解耦。各路sic-mosfet管均对应连接有栅极驱动电路,如图2所示,该栅极驱动电路包括:驱动芯片,sic-mosfet管q8和sic-mosfet管q9分别对应驱动芯片u32和驱动芯片u30,驱动芯片为驱动集成(如ucc5350mc驱动芯片), 该驱动芯片为具有米勒钳位的单通道隔离式栅极驱动器,用于驱动、igbt、sic-mosfet;该驱动芯片的输出端允许供电范围为电压范围:15v ~ 33v。ucc5350mc驱动芯片还具有欠压保护点uvlo,为驱动芯片的欠压保护点uvlo决定了开关管可以正常工作时最小的驱动电压,为了防止sic-mosfet管的误开通,sic-mosfet管驱动一般会使用负电压供电,但是对于大部分无单独com脚的驱动芯片来说,驱动芯片的uvlo通常参考的是驱动芯片的vee/vss引脚。

21.驱动芯片u32的clamp引脚与sic-mosfet管q8的栅极电连接,驱动芯片u32的vcc2引脚(vcc2是连接正电压端,通过外接供电电源来为sic-mosfet提供正的驱动电压)与降压变换器的vcc-l引脚连接,驱动芯片u32的in+引脚与vgs延迟电路的pwm2端口连接,驱动芯片u32的in-引脚与mcu

‑ⅱ

(u2b)的drv2-en引脚连接。同理,驱动芯片u32的clamp引脚与sic-mosfet管q9的栅极电连接,驱动芯片u30的vcc2引脚(vcc2是连接正电压端,通过外接供电电源来为sic-mosfet提供正的驱动电压)与降压变换器的vcc-h引脚连接,驱动芯片u30的in+引脚与vgs延迟电路的pwm1端口连接,驱动芯片u30的in-引脚与mcu

‑ⅱ

(u1b)的drv1-en引脚连接。

22.mcu

‑ⅰ

(u1a)与栅极驱动中(驱动芯片u30和驱动芯片u32)结合可实现sic-mosfet管的软关闭功能,采用软关闭可以有效防止在关闭的瞬间造成电路的电压升高的情况。当检测到了短路或过流信号,mcu

‑ⅰ

(u1a)输出的pwm并未软关闭或直接关闭,而是立即将此时对应的栅极电压vgs先降低,并由此来判断sic-mosfet是否还在过流或短路,如果还是,根据sic-mosfet短路承受时间,mcu通过控制驱动芯片u30与u32来关闭pwm信号。

23.具体实施:当检测到了短路或过流信号,通过mcu

‑ⅱ

(u1b)分别控制驱动芯片u30与驱动芯片u32的in+引脚与in-引脚,进行不同时间段检测两支路sic-mosfet管的稳态工作电流ids的大小,例如:在检测sic-mosfet管q9的稳态工作电流ids或检测sic-mosfet管q8的稳态工作电流ids,当其中sic-mosfet管出现短路或过流,mcu

‑ⅱ

(u1b)通过控制驱动芯片u32的in+引脚与in-引脚实现关闭驱动芯片u32输出;mcu

‑ⅱ

(u1b)通过控制驱动芯片u30的in+引脚与in-引脚关闭驱动芯片u30输出。

24.相比于开关瞬态过程,导通电阻对sic-mosfet在稳态后的均流影响更大,导通电阻较小的器件将承担更大的电流,这将影响支路器件的可靠性,并联的sic-mosfet各管的导通电阻的差异性对稳态均流的影响较大,为此可采用对并联的各个sic-mosfet的栅极电压vgs进行控制,来达到各并联的sic-mosfet支路均流;如下图4所示,为vgs与rds(on)的关系,可看出门极电压vgs越高,rds(on)越小。

25.电阻值rds(on)因电流不同而不同,如下图5所示,在t1-t2时间段内,随着栅极电压vgs从阈值电压vgs(th)逐渐增大至米勒平台电压vgp,电流ids从0开始逐渐增大,sic-mosfet管开始导通,米勒平台t3时间内,栅极电压vds开始下降,t3之后米勒平台结束,sic-mosfet管进入可变电阻区,栅极电压vgs电压在栅极电荷的驱动下继续升高至最大值,使 sic-mosfet进一步完全导通;在可变电阻区,相应的栅极电压vgs对应着一定的漏源极电压vds,即漏极d和源极s之间的电阻值rds(on)受控于栅极电压vgs;那么对于不同导通电阻值rds(on)的sic-mosfet并联,为达到均流,即电流ids相同,可通过调整并联sic-mosfet的各栅源电压vgs来实现。

26.因此,驱动芯片与对应支路所在sic-mosfet管的栅极电连接,且该sic-mosfet管对应的vgs电压控制电路和vgs延迟电路分别与驱动芯片之间电连接。

27.通过vgs电压控制电路对并联sic-mosfet管的各栅源电压vgs进行调节,以实现并联sic-mosfet管的均流控制,如图3a和图3b所示,该vgs电压控制电路设计如下:采用mcu

‑ⅱ

(u1b)的i2c接口控制的集成降压变换器(型号为mp8849)的输出vcc电路为驱动芯片供电,分别为集成降压变换器u23与集成降压变换器u24(型号为mp8849),集

成降压变换器u23与集成降压变换器u24的输出电压vcc_h和vcc_l分别连接在驱动芯片u30与驱动芯片u32的vcc2引脚,通过调整vcc_h和vcc_l的电压,可以实现两个并联sic-mosfet( q8与q9 )的栅源电压vgs大小。其中,集成降压变换器(型号为mp8849)支持2.8v至22v的宽工作输入电压范围,可提供1v至20.47v范围内的输出电压,以10mv为步长。

28.为实现上述的栅源电压vgs大小调节,需要对先采集sic-mosfet管q8和sic-mosfet管q9的稳态工作电流ids,因此,sic-mosfet管并联电路中各支路sic-mosfet管分别对应连接有电流采集电路,各所述电流采集电路分别通过信号调理电路与高速单片机之间通信连接。

29.由于sic-mosfet管的源极经电流采样电阻串联接地;如图6所示,所述电流采集电路包括:两个差分放大器,分别为差分放大器u29b和差分放大器u31b,所述差分放大器u29b的两个输入端分别连接至电流采样电阻r148的两端(vin1+和vin1-),差分放大器u29b的输出端vout1与信号调理电路之间电连接。所述差分放大器u31b的两个输入端分别连接至电流采样电阻r147的两端(vin2+和vin2-),差分放大器u31b的输出端vout2与信号调理电路之间电连接。上述中,经过差分放大器放大的输出直流信号分别为输出端vout1和输出端vout2。

30.现有的高性能分流电阻中,有可消耗高达5w功率值的大功率型号电阻,以及具有0.1mω超低电阻值的高精度分流电阻(如rohm电流检测贴片电阻lrt18系列),可以根据实际工况需求选择相应的分流电阻。通过降低分流电阻的阻值来降低损耗,但分流电阻的压降也会降低,电压检测会变得更小,为此在本实施例中,差分放大器选择高精度运算放大器,同时注意选择带宽较宽的运算放大器。以下对于差分放大器的设计予以说明:在本电路设计,选择r139=r146,r137=r149,通过叠加定理可得:vout1=r137/r139 x [(vin1+)-(vin1-)]+vref在运算放大器的正端加电压偏移量vref,目的是对于电路在采集中存在着负直流电压,为使得输出电压为正值可保证mcu采集到正电压,因而在同相端的电阻r149接一个电压值vref即偏移电压;增加二极管d25去除前级串入的交流部分,r140与c104组成低通是防止运放输出电容引起过冲。差分放大器u31b的电路设计同理,不再赘述。

[0031]

进一步,上述的信号调理电路包括:同相放大电路和低通滤波器,所述差分放大器u29b的输出端vout1依次经同相放大电路和低通滤波器串联至mcu

‑ⅲ

(u1c)的adc1引脚,所述差分放大器u31b的输出端vout2依次经同相放大电路和低通滤波器串联至mcu

‑ⅲ

(u1c)的adc2引脚。在本实施例中,为了提高测量精度,电路采用了具有低噪声,高精度,单电源条件下工作,输出摆幅大,并具有轨到轨输出,以及较高的开环增益的运算放大器【如ti的opa2356】对输入信号进行检测。其中,如图7所示,由运算放大器u25c与电阻r123、电阻r117、电阻r118组成同相放大电路,其增益为(电阻r117/电阻r118),可以调整r117改变放大倍数,调整增益使输入vout1电压放大以满足后级mcu

‑ⅲ

(u1c)的采样要求。另一方面,由运算放大器u25b与电阻r121、电阻c86构成一个二阶有源低通滤波器,可以滤除前端采样信号中的高频干扰信号,较好地保持信号的纯度;电阻r121与电容c86的时间常数网络目的是给adc 足够的采样时间,否则会导致adc 的精度降低,电容c86应尽量小避免电压残留。另一路信号调理电路的电路设计原理相同,此处不再赘述。

[0032]

各所述栅极驱动电路分别电连接有vgs延迟电路,即驱动芯片u30和驱动芯片u32

的pwm1信号与pwm2信号分别来自vgs延迟电路,且vgs延迟电路与mcu

‑ⅰ

(u1a)之间通信连接。vgs延迟电路设计如下:与高速单片机通信连接的触发器,所述触发器的pwm信号端与驱动芯片之间通信连接。具体的,如图8所示,触发器u27的d触发端与mcu

‑ⅰ

(u1a)的gpio1相连,脉冲信号输入端与mcu

‑ⅰ

(u1a)的时钟输出端clk相连,触发器u27与mcu控制端组成vgs延迟电路;另一路vgs延迟电路的电路设计原理相同,此处不再赘述。

[0033]

该vgs延迟电路采用触发器和mcu组成并输出栅极延迟控制源信号,其中,触发器采用t1的sn74lvc1g79触发器,该器件是一种的单路正沿触发 d 型触发器,电源电压可从 1.65v 到 5.5v ;两个触发器的时钟clk连接到mcu

‑ⅰ

(u1a)同一时钟clk,通过mcu

‑ⅰ

(u1a)不同gpio1和gpio2接口控制两个触发器输出pwm1信号与pwm2信号,通过mcu

‑ⅰ

(u1a)控制pwm1延时的波形如图9所示。

[0034]

高速单片机连接有rs-232接口,通过该rs-232接口与外部pc机之间通信,通过该接口可以连接到pc机,实现pc机与高速单片机通信,利用配置软件可对各种参数进行采集以及调整。

[0035]

实施例2在本发明中还提供了一种自适应sic-mosfet管并联均流的控制方法,该控制方法基于上述实施例1中所述的自适应sic-mosfet管并联均流的控制电路,该控制方法包括:s1:对sic-mosfet管并联电路中各个sic-mosfet管的稳态工作电流ids进行实时采集;具体为:通过电流采集电路1与电流采集电路2分别连接到sic-mosfet管q8和sic-mosfet管q9的源极所接电阻r147与电阻r148的两端采集点,对sic-mosfet管q8和sic-mosfet管q9的稳态工作电流ids进行实时采集;在实际应用时,通过高速单片机配置adc的采样模式为同步规则采样,adc1和adc2采样模式相同,该模式可在高速单片机adc_cr1寄存器中配置;从而实时检测两支路sic-mosfet管的稳态工作电流ids的大小,s2:对采集的稳态工作电流ids经信号调理至adc采样范围,对各支路sic-mosfet管采集的电流转换为电压输出信号进行放大、滤波,使其适合mcu的adc输入范围并由mcu进行数据处理;s3:将adc采样范围内的信号输入至高速单片机进行判断比较,以对各支路sic-mosfet管的输出电流大小进行比较;s4:从动态控制均流:通过高速单片机对并联sic-mosfet管的各栅源电压vgs进行控制,以实现并联sic-mosfet管的均流控制。其控制逻辑如下:由于漏极d和源极s之间的电阻值rds(on)受控于栅源电压vgs,若检测到某支路sic-mosfet管的输出电流偏大,根据栅源电压vgs与电阻值rds(on)的关系(栅极电压vgs越高,电阻值rds(on)越小),则需要对栅源电压vgs调小,使电阻值rds(on)升高,进而降低该支路sic-mosfet管的输出电流,以实现电流均衡;反之同理,此处不再赘述。

[0036]

采用动态控制均流:通过高速单片机控制触发器输出具有时间差的栅极驱动信号,使sic-mosfet管并联电路中sic-mosfet管所对应栅极驱动信号的上升沿延迟,实现各路sic-mosfet管的电流均衡,以解决并联sic-mosfet管因器件参数不一致所造成的不均流问题。采集并联各支路sic-mosfet管的工作电流,并对各sic-mosfet管的输出电流大小进行比较,进一步控制每个支路sic-mosfet管的栅极加载电压延迟时间(通过控制gpio1和

gpio2的触发时间,可以达到控制输出pwm1信号和pwm2信号两者之间的时间差,以控制后级sic-mosfet管的栅极驱动信号上升沿延迟时间)。其控制逻辑如下:通常各sic-mosfet管的栅源阈值电压ugs(th)不一致,若在两个sic-mosfet管并联电路中,某只sic-mosfet管的栅源阈值电压ugs(th)较低,而另一只sic-mosfet管的栅源阈值电压ugs(th)较高,则通过控制栅源阈值电压ugs(th)较低的sic-mosfet管的栅极驱动信号上升沿延迟时间,这样可以避免该管承受更大的开通电流,在实际工况中,通常两支路所选的sic-mosfet管的栅源阈值电压ugs(th)存在差异较大,因此,通过对某一支路动态延迟控制,两支路sic-mosfet管可实现均流的效果。

[0037]

需要说明的是,流程图中或在此以其他方式描述的任何过程或方法描述可以被理解为,表示包括一个或更多个用于实现特定逻辑功能或过程的步骤的可执行指令的代码的模块、片段或部分,并且本技术的优选实施方式的范围包括另外的实现,其中可以不按所示出或讨论的顺序,包括根据所涉及的功能按基本同时的方式或按相反的顺序,来执行功能,这应被本技术的实施例所属技术领域的技术人员所理解。

[0038]

应当理解,本技术的各部分可以用硬件、软件、固件或它们的组合来实现。在上述实施方式中,多个步骤或方法可以用存储在存储器中且由合适的指令执行系统执行的软件或固件来实现。例如,如果用硬件来实现,和在另一实施方式中一样,可用本领域公知的下列技术中的任一项或他们的组合来实现:具有用于对数据信号实现逻辑功能的逻辑门电路的离散逻辑电路,具有合适的组合逻辑门电路的专用集成电路,可编程门阵列(pga),现场可编程门阵列(fpga)等。

[0039]

本技术领域的普通技术人员可以理解实现上述实施例方法携带的全部或部分步骤是可以通过程序来指令相关的硬件完成,所述的程序可以存储于一种计算机可读存储介质中,该程序在执行时,包括方法实施例的步骤之一或其组合。

[0040]

此外,在本技术各个实施例中的各功能单元可以集成在一个处理模块中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个模块中。上述集成的模块既可以采用硬件的形式实现,也可以采用软件功能模块的形式实现。所述集成的模块如果以软件功能模块的形式实现并作为独立的产品销售或使用时,也可以存储在一个计算机可读取存储介质中。

[0041]

上述提到的存储介质可以是只读存储器,磁盘或光盘等。

[0042]

尽管上面已经示出和描述了本技术的实施例,可以理解的是,上述实施例是示例性的,不能理解为对本技术的限制,本领域的普通技术人员在本技术的范围内可以对上述实施例进行变化、修改、替换和变型。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1