一种伪恒频控制电路的制作方法

本技术涉及驱动技术,应用于电学领域,尤其涉及一种伪恒频控制电路。

背景技术:

1、当接入的负载从重载变为中载,基于恒定关断时间(constant off-time cft)控制的升压boost变换电路的输出电流会变小,其工作模式则会从连续导通模式(continuousconduction mode,ccm)切换至断续导通模式(discontinuous conduction mode,dcm),功率开关管的开通时间会减小而关断时间不变,进而使功率开关管的开关频率会发生变化。因此,基于cft控制的boost变换电路无法适用于对开关频率要求较高的应用场景。

技术实现思路

1、本技术实施例公开了一种伪恒频控制电路,用于提高boost变换电路工作时功率开关管的开关频率的稳定性。

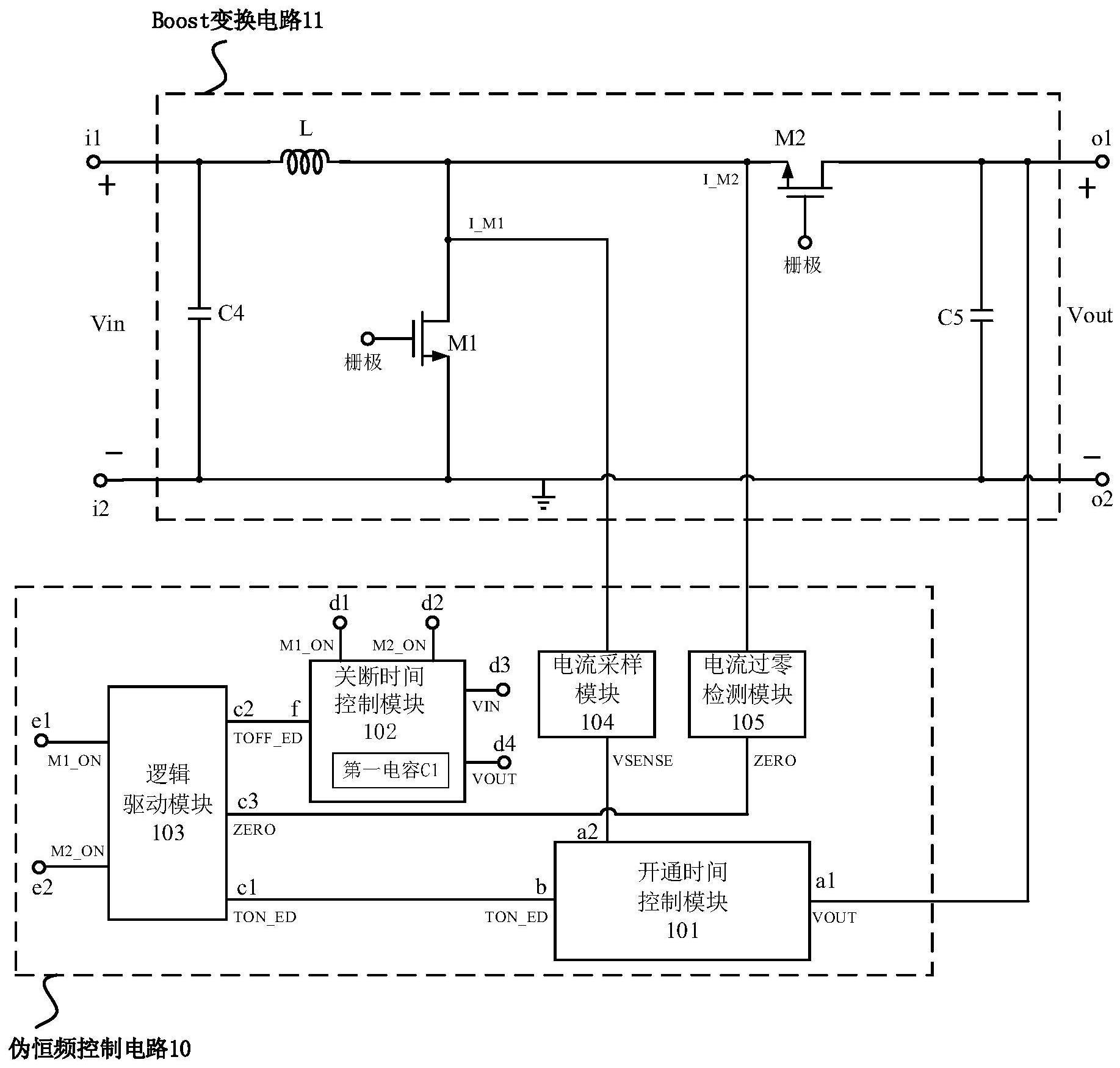

2、第一方面,本技术实施例提供了一种伪恒频控制电路,伪恒频控制电路包括开通时间控制模块101、关断时间控制模块102和逻辑驱动模块103,关断时间控制模块102包括第一电容c1,其中,开通时间控制模块101用于输出第一控制信号ton_ed,当流经升压boost变换电路中第一开关管m1的第一电流信号i_m1转换得到的第一电压信号vsense的电压值达到第一电压值时第一控制信号ton_ed的电压值由低电平突变为高电平,boost变换电路的输出电流信号的电流值变小,则第一电压值变小;逻辑驱动模块103用于在第一控制信号ton_ed的电压值由低电平突变为高电平时控制第一开关管m1关断;关断时间控制模块102用于输出第二控制信号toff_ed,当第一电容c1输出的第二电压信号ripple达到预设电压阈值时第二控制信号toff_ed的电压值由低电平突变为高电平,boost变换电路的输出电流信号的电流值变小,则第一电容c1的充电速度变慢;逻辑驱动模块103用于在第二控制信号toff_ed的电压值由低电平突变为高电平的情况下控制第一开关管m1导通。

3、上述伪恒频控制电路中第一电压信号vsense的电压值达到第一电压值所用的时间为第一开关管m1的导通时间,第一电容c1输出的第二电压信号ripple达到预设电压阈值所用的时间为第一开关管m1的关断时间。当接入boost变换电路的负载从重载变为中载后,boost变换电路的输出电流会变小,第一电压值变小,第一电压信号vsense的电压值达到第一电压值所用的时间减少,第一开关管m1的导通时间则随之缩短。进一步的,第一开关管m1断开后,第一电容c1的充电速度变慢,第二电压信号ripple达到预设电压阈值所用的时间变长,第一开关管m1的关断时间则随之延长。

4、因此,在接入boost变换电路的负载从重载变为中载的情况下,上述伪恒频控制电路在缩短第一开关管m1(可视为功率开关管)的导通时间后可以延长第一开关管m1的关断时间,以减小第一开关管m1的开关频率的变化幅度,进而提高boost变换电路工作时第一开关管m1的开关频率的稳定性。

5、结合第一方面,在一种可能的实现方式中,伪恒频控制电路还包括电流采样模块104;开通时间控制模块101的第一输入端a1连接boost变换电路的正极输出端o1,开通时间控制模块101的第二输入端a2通过电流采样模块104连接第一开关管m1的漏极,开通时间控制模块101的输出端b连接逻辑驱动模块103的第一输入端c1,逻辑驱动模块103的第一输出端e1连接第一开关管m1的栅极;其中,电流采样模块104用于将第一电流信号i_m1转换为第一电压信号vsense,第一电流信号i_m1的电流值变大,则第一电压信号vsense的电压值变大;boost变换电路的输出电压信号vout的电压值变大,则第一电压值变小。

6、boost变换电路的输出电流变小,进而使boost变换电路的输出电压受到扰动而变大,即输出电压的变化响应于输出电流的变化,上述伪恒频控制电路的开通时间控制模块101可以基于输出电压的变化情况,在输出电流变小时减小第一电压值,缩短第一开关管m1的开通时间。

7、结合第一方面,或者第一方面的上述任一种可能的实现方式,在另一种可能的实现方式中,伪恒频控制电路还包括电流过零检测模块105;关断时间控制模块102的第一输入端d1连接逻辑驱动模块103的第一输出端e1,关断时间控制模块102的第二输入端d2连接逻辑驱动模块103的第二输出端e2,关断时间控制模块102的输出端f连接逻辑驱动模块103的第二输入端c2,逻辑驱动模块103的第二输出端e2连接boost变换电路中第二开关管m2的栅极,逻辑驱动模块103的第三输入端c3通过电流过零检测模块105连接boost变换电路中第二开关管m2的源极,其中,电流过零检测模块105用于输出第三控制信号zero,流经第二开关管m2的第二电流信号i_m2的电流值变为零,则第三控制信号zero的电压值由低电平突变为高电平,逻辑驱动模块103用于在第一开关管m1处于关断状态且第三控制信号zero的电压值为低电平的情况下,控制第二开关管m2导通,以及在第一开关管m1处于关断状态且第三控制信号zero的电压值由低电平突变为高电平的情况下,控制第二开关管m2关断。

8、boost变换电路的输出电流变小,进而使boost变换电路从连续导通模式切换至断续导通模式,上述伪恒频控制电路中,逻辑驱动模块103在断续导通模式时控制第一开关管m1关断后控制第二开关管m2(可视为同步整流开关管)先导通再关断,而在连续导通模式时控制第一开关管m1关断后控制第二开关管m2导通,即逻辑驱动模块103输出的控制信号的变化可以响应于输出电流的变化。又因为关断时间控制模块102可以接收逻辑驱动模块103输出的控制信号,进而可以基于控制信号的变化情况在输出电流变小时减慢第一电容c1的充电速度,从而延长第一开关管m1的关断时间。

9、结合第一方面,或者第一方面的上述任一种可能的实现方式,在又一种可能的实现方式中,关断时间控制模块102的第三输入端d3连接boost变换电路的正极输入端i1,关断时间控制模块102的第四输入端d4连接boost变换电路的正极输出端o1,其中,关断时间控制模块102用于在第一开关管m1处于关断状态且第二开关管m2处于导通状态的情况下基于boost变换电路的输出电压向第一电容c1充电,以及在第一开关管m1和第二开关管m2均处于关断状态的情况下基于boost变换电路的输入电压向第一电容c1充电。

10、上述伪恒频控制电路中,在连续导通模式下第一开关管m1和第二开关管m2不可能同时处于关断状态,而在断续导通模式下第一开关管m1和第二开关管m2可以在一段时间内同时处于关断状态。也即是说,boost变换电路的输出电流较大时关断时间控制模块102仅基于输出电压向第一电容c1充电,而boost变换电路的输出电流变小时关断时间控制模块102先基于输出电压向第一电容c1充电再基于输入电压向第一电容c1充电。

11、boost变换电路为升压电路,其输入电压小于输出电压,那么基于输入电压向第一电容c1充电时的充电速度小于基于输出电压向第一电容c1充电时的充电速度,由此可见,上述伪恒频控制电路中的关断时间控制模块102可以在输出电流变小时减慢第一电容c1的充电速度。

12、结合第一方面,或者第一方面的上述任一种可能的实现方式,在又一种可能的实现方式中,关断时间控制模块102还包括第一转换模块201、第二转换模块202、逻辑控制模块203、第一比较器cmp1、第三开关管m3、第四开关管m4和第五开关管m5;第一转换模块201的输入端g连接关断时间控制模块102的第三输入端d3,第二转换模块202的输入端h连接关断时间控制模块102的第四输入端d4,逻辑控制模块203的第一输入端j1连接关断时间控制模块102的第一输入端d1,逻辑控制模块203的第二输入端j2连接关断时间控制模块102的第二输入端d2,第一比较器cmp1的输出端连接关断时间控制模块102的输出端f;第一转换模块201的第一输出端k1连接第三开关管m3的源极,第一转换模块201的第二输出端k2连接参考地,第二转换模块202的第一输出端n1连接第四开关管m4的源极,第二转换模块202的第二输出端n2连接参考地,逻辑控制模块203的第一输出端m1连接第三开关管m3的栅极,逻辑控制模块203的第二输出端m2连接第四开关管m4的栅极,逻辑控制模块203的第三输出端m3连接第五开关管m5的栅极;第四开关管m4的漏级连接第三开关管m3的漏级和第一电容c1的一端,第一比较器cmp1的正极输入端连接第一电容c1的一端和第五开关管m5的漏级,第一比较器cmp1的负极输入端连接关断时间控制模块102的第三输入端d3,第一电容c1的另一端和第五开关管m5的源极连接参考地;

13、其中,预设电压阈值为boost变换电路的输入电压,第一转换模块201的第一输出端k1输出的第一电流值与boost变换电路的输入电压成正比,第二转换模块202的第一输出端n1输出的第二电流值与boost变换电路的输出电压成正比;在第一开关管m1处于导通状态且第二开关管m2处于关断状态的情况下,逻辑控制模块203用于控制第三开关管m3和第四开关管m4均关断且控制第五开关管m5导通;在第一开关管m1处于关断状态且第二开关管m2处于导通状态的情况下,逻辑控制模块203用于控制第三开关管m3和第五开关管m5均关断且控制第四开关管m4导通;在第一开关管m1和第二开关管m2均处于关断状态的情况下,逻辑控制模块203用于控制第四开关管m4和第五开关管m5均关断且控制第三开关管m3导通。

14、结合第一方面,或者第一方面的上述任一种可能的实现方式,在又一种可能的实现方式中,第一转换模块201包括第一放大器op1、第六开关管m6、第七开关管m7、第一电阻r1和第一电源s1;第一放大器op1的负极输入端为第一转换模块201的输入端g,第七开关管m7的漏级为第一转换模块201的第一输出端k1,第一电阻r1的一端为第一转换模块201的第二输出端k2;第一放大器op1的输出端连接第六开关管m6的栅极和第七开关管m7的栅极,第六开关管m6的源极连接第七开关管m7的源级和第一电源s1,第六开关管m6的漏极连接第一电阻r1的另一端和第一放大器op1的正极输入端。

15、结合第一方面,或者第一方面的上述任一种可能的实现方式,在又一种可能的实现方式中,第二转换模块202包括第二放大器op2、第八开关管m8、第九开关管m9、第二电阻r2和第二电源s2;第二放大器op2的负极输入端为第二转换模块202的输入端h,第九开关管m9的漏级为第二转换模块202的第一输出端n1,第二电阻r2的一端为第二转换模块202的第二输出端n2;第二放大器op2的输出端连接第八开关管m8的栅极和第九开关管m9的栅极,第八开关管m8的源极连接第九开关管m9的源级和第二电源s2,第八开关管m8的漏极连接第二电阻r2的另一端和第二放大器op2的正极输入端。

16、结合第一方面,或者第一方面的上述任一种可能的实现方式,在又一种可能的实现方式中,逻辑控制模块203包括第一反相器inv1、第一或门or1、第二或门or2、第一与非门nd1和第二与非门nd2;第一反相器inv1的输入端连接逻辑控制模块203的第二输入端j2,第一反相器inv1的输出端连接第一或门or1的第一输入端,第一或门or1的第二输入端连接逻辑控制模块203的第一输入端j1,第一或门or1的第三输入端连接第二与非门nd2的输出端,第一或门or1的输出端连接逻辑控制模块203的第二输出端m2和第一与非门nd1的第一输入端;第一与非门nd1的第二输入端连接第二或门or2的输出端,第一与非门nd1的输出端连接第二与非门nd2的第一输入端,第二与非门nd2的第二输入端连接逻辑控制模块203的第一输入端j1,第二与非门nd2的输出端连接逻辑控制模块203的第三输出端m3,第二或门or2的第一输入端连接逻辑控制模块203的第二输入端j2,第二或门or2的第二输入端和第三输入端分别连接逻辑控制模块203的第一输入端j1。

17、结合第一方面,或者第一方面的上述任一种可能的实现方式,在又一种可能的实现方式中,开通时间控制模块101包括第三电阻r3、第四电阻r4、第五电阻r5、第二电容c2、第三电容c3、第三电源s3、第三放大器ea、第二比较器cmp2;第三电阻r3的一端连接开通时间控制模块101的第一输入端a1,第二比较器cmp2的正极输入端连接开通时间控制模块101的第二输入端a2,第二比较器cmp2的输出端连接开通时间控制模块101的输出端b;第三电阻r3的另一端连接第三放大器ea的负极输入端和第四电阻r4的一端,第三放大器ea的正极输入端连接第三电源s3的正极,第三电源s3的负极和第四电阻r4的另一端均连接参考地,第三放大器ea的输出端连接第五电阻r5的一端,第三电容c3的一端和第二比较器cmp2负极输入端,第五电阻r5的另一端连接第二电容c2的一端,第二电容c2的另一端连接第三电容c3的另一端,第三电容c3的另一端连接参考地;其中,第一电压值为第三电源s3的输出电压和所述第四电阻r4两端电压之间的差值。

18、结合第一方面,或者第一方面的上述任一种可能的实现方式,在又一种可能的实现方式中,逻辑驱动模块103包括第三或门or3、第四或门or4、第五或门or5、第六或门or6、第七或门or7、第二反相器inv2、第一缓冲器buf1和第二缓冲器buf2;第三或门or3的第一输入端连接逻辑驱动模块103的第二输入端c2,第三或门or3的第二输入端连接第四或门or4的输出端,第三或门or3的输出端连接第二反相器inv2的输入端和第四或门or4的第一输入端or4,第四或门or4的第二输入端连接逻辑驱动模块103的第一输入端c1,第二反相器inv2的输出端连接第一缓冲器buf1的输入端、第五或门or5的第一输入端和第七或门or7的第一输入端,第一缓冲器buf1的输出端连接逻辑驱动模块103的第一输出端e1;第五或门or5的第二输入端连接第六或门or6的输出端,第五或门or5的输出端连接第六或门or6的第一输入端和第七或门or7的第二输入端,第七或门or7的输出端连接第二缓冲器buf2的输入端,第二缓冲器buf2的输出端连接逻辑驱动模块103的第二输出端e2,第六或门or6的第二输入端连接逻辑驱动模块103的第三输入端c3。

19、结合第一方面,或者第一方面的上述任一种可能的实现方式,在又一种可能的实现方式中,boost变换电路包括第一开关管m1、第二开关管m2、电感l、第四电容c4和第五电容c5;电感l的一端连接boost变换电路的正极输入端i1和第四电容c4的一端,电感l的另一端连接第一开关管m1的漏级和第二开关管m2的源极,第二开关管m2的漏极连接第五电容c5的一端和boost变换电路的正极输出端o1;boost变换电路的负极输入端i2、第四电容c4的另一端、第一开关管m1的源极、第五电容c5的另一端和boost变换电路的负极输出端o2均连接参考地。

20、可以理解的是,本技术实施例的boost变换电路中第一开关管m1可视为功率开关管,第二开关管m2可视为同步整流开关管。

21、第二方面,本技术实施例提供了一种伪恒频控制装置,该伪恒频控制装置包括第一方面或第一方面任一种可能的实施方式所描述的伪恒频控制电路。

22、第三方面,本技术实施例提供了一种boost变换器,该boost变换器包括第一方面或第一方面任一种可能的实施方式所描述的伪恒频控制电路以及boost变换电路。

23、本技术第二和第三方面所提供的相关装置,其有益效果可以参考第一方面技术方案的有益效果,此处不再赘述。

- 还没有人留言评论。精彩留言会获得点赞!