一种氮化镓多功能充电器的制作方法

本发明涉及充电器领域,具体来说,涉及一种氮化镓多功能充电器。

背景技术:

1、氮化镓作为一种无机物,是氮和镓的化合物,是一种直接能隙的半导体,常用在超级快充充电器中。此化合物结构类似纤锌矿,硬度很高,用于充电器中,将大大缩短手机等电子设备的充电时间。

2、氮化镓半导体具有以下特点:氮化镓是一种直接能隙半导体;氮化镓具有较高的电子饱和漂移速度;氮化镓的带隙宽度相对较大。在超级快充充电器中,氮化镓通常用于功率转换器和充电控制电路中,以提供高效的电能转换和快速充电功能。这些特性使氮化镓成为先进电子器件的重要材料之一。

3、充电器作为一种电子消费产品,在我们日常生活中随处可见,它能满足智能手机等可充电装置的能量需求。随着各种智能日常用品的普及,充电器的应用越来越广泛,所以在未来市场上充电器的需求量将会持续增长。随着市场上多口快充功能需求的进一步扩大,常规多口快充空间较大,降低了便携性,已不能满足多功能快充的需求。

4、针对相关技术中的问题,目前尚未提出有效的解决方案。

技术实现思路

1、针对相关技术中的问题,本发明提出一种氮化镓多功能充电器,以克服现有相关技术所存在的上述技术问题。

2、为此,本发明采用的具体技术方案如下:

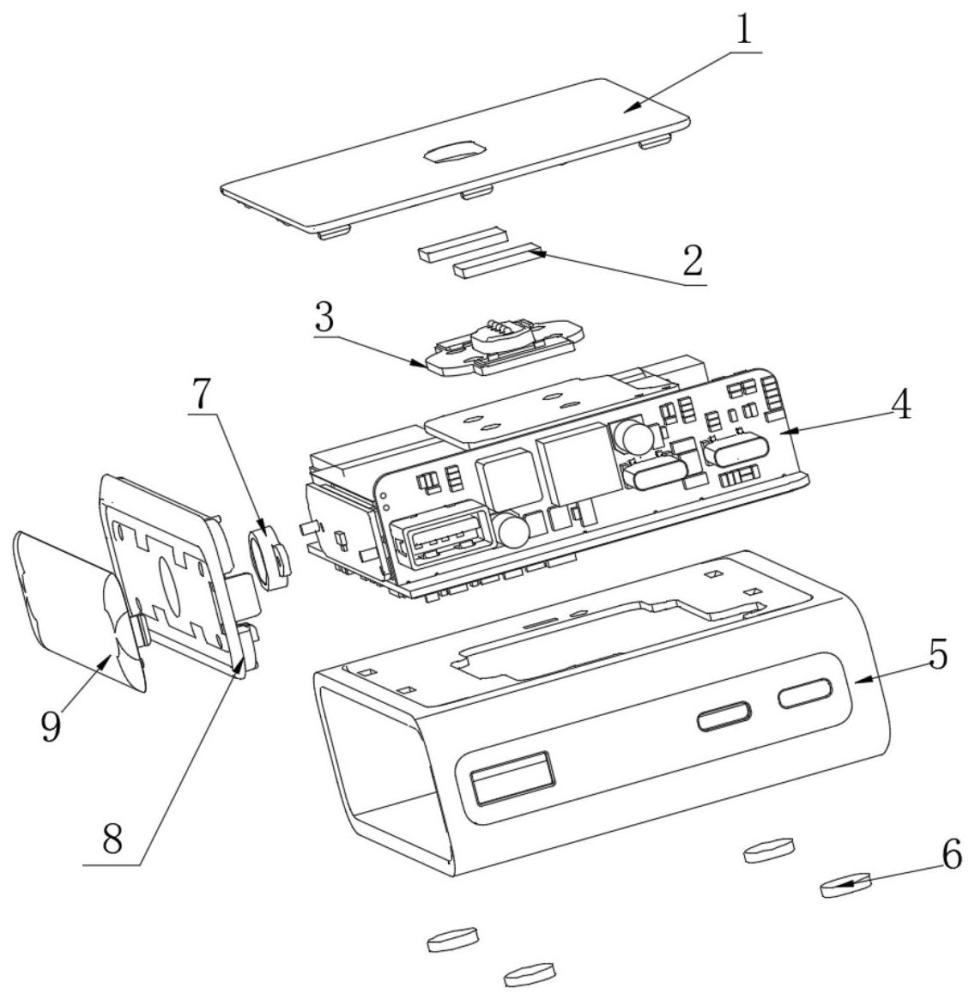

3、一种氮化镓多功能充电器,包括后壳,后壳的内部设置有pcba组件,pcba组件的顶端设置有弹簧针连接器,弹簧针连接器的两侧均设置有磁铁,弹簧针连接器的顶部且位于后壳的顶端设置有顶盖;后壳的一端设置有导光柱,导光柱的外侧且位于后壳的端部连接有前壳,前壳远离后壳的一端设置有装饰盖,后壳的底端设置有若干硅胶垫;氮化镓多功能充电器还包括ac输入模块,ac输入模块与输入整流滤波电路连接,输入整流滤波电路与pfc电路连接,pfc电路分别与变压器电路及pwm电路连接,变压器电路与输出同步整流电路连接,输出同步整流电路与输出滤波电路连接,输出滤波电路与协议ic控制电路连接,协议ic控制电路分别与第一type-c输出模块、第二type-c输出模块、usb-a输出模块及弹簧针输出模块连接。

4、进一步的,为了通过合理布局有效的利用内部空间,缩小产品体积,pcba组件包括设置在后壳内的主板,主板的顶端依次排列设置有pfc电感、变压器、卧式输入电解电容、ac座及输出固定电容;主板的一侧设置有dc板,dc板的顶部依次排列设置有usb-a、贴片电容、第一type-c及第二type-c;主板的一端设置有灯板,主板的顶部设置有弹簧针连接器板。

5、进一步的,ac输入模块包括连接器cn1及保险丝f1,ac输入模块的侧边还依次设置有变压器lx3、电阻r61、电阻r62、电容cx1、二极管d9及二极管d8;

6、其中,连接器cn1的第一端与保险丝f1的一端连接,保险丝f1的另一端与变压器lx3的第一端连接,连接器cn1的第二端与变压器lx3的第二端连接,变压器lx3的第三端依次与电阻r61的一端、电容cx1的一端、二极管d9的正极及输入整流滤波电路连接,变压器lx3的第四端依次与电阻r62的一端、电容cx1的另一端、二极管d8的正极及输入整流滤波电路连接,电阻r61的另一端与电阻r62的另一端连接,二极管d9的负极与二极管d8的负极连接。

7、进一步的,输入整流滤波电路包括变压器lx2及整流器bd1,输入整流滤波电路的侧边还依次设置有电容c42、电容c29、电容c27及变压器lx1;

8、其中,变压器lx2的第一端与二极管d9的正极连接,变压器lx2的第四端与二极管d8的正极连接,变压器lx2的第二端与整流器bd1的第三端连接,变压器lx2的第三端与整流器bd1的第二端连接,整流器bd1的第一端依次与电容c42的一端及变压器lx1的第一端连接,整流器bd1的第四端依次与电容c42的另一端、电容c29的一端及电容c27的一端连接并接地,电容c27的另一端依次与pfc电路、电容c29的另一端及变压器lx1的第二端连接。

9、进一步的,pfc电路包括电阻r24、电阻r19、电阻r23、电容c35、变压器l3、电感l4、二极管d3、二极管d1、二极管d4、电阻r32、电阻r36、电阻r33、电阻r35、电容c45、二极管d5、mos管q11、电阻r41、电阻r42、电阻r43、电阻r40、电容c49、电阻r38、电阻r47、电容c54、电阻r46、电阻r54、电容c63、电容c57、电容c58、芯片u5、电阻r52及电阻c59,pfc电路的侧边还依次设置有二极管d2、电容c30、电阻r20、电阻r28、电阻r34、电阻r37、电阻r44、电阻r51、电阻r49、电容c56、电容c41、电容c37及电容ec1;

10、其中,电阻r19的一端依次与电容c27的另一端、变压器l3的第一端及二极管d1的正极连接,电阻r19的另一端与电阻r24的一端连接,电阻r24的另一端依次与电容c35的一端、二极管d3的负极、电阻r38的一端及电容c54的一端连接,电容c35的另一端与电阻r23的一端连接,电阻r23的另一端与变压器l3的第四端连接,变压器l3的第二端与二极管d3的正极连接并接地,变压器l3的第三端与电感l4的一端连接,电感l4的另一端依次与mos管q11的漏极、二极管d2的正极及电容c30的一端连接,二极管d2的负极依次与电容c30的另一端、二极管d1的负极、电阻r20的一端、电容c41的一端、电容ec1的一端、电容c37的一端及变压器电路连接,电容ec1的另一端依次与变压器电路、电容c37的另一端及电容c41的另一端连接并接地,电阻r20的另一端与电阻r28的一端连接,电阻r28的另一端与电阻r34的一端连接,电阻r34的另一端与电阻r37的一端连接,电阻r37的另一端与电阻r44的一端连接,电阻r44的另一端依次与电阻r51的一端、电阻r49的一端及电容c56的一端连接,电阻r51的另一端依次与电阻r49的另一端及电容c56的另一端连接并接地;

11、mos管q11的栅极依次与二极管d5的负极、电阻r35的一端、电容c45的一端及电阻r33的一端连接,电阻r33的另一端依次与电容c45的另一端、电阻r36的一端及电阻r32的一端连接,电阻r32的另一端与二极管d4的正极连接,二极管d4的负极与电阻r36的另一端连接,电阻r35的另一端依次与二极管d5的正极、电阻r41的一端、mos管q11的源极、电阻r42的一端、电容c49的一端、电阻r40的一端及电阻r43的一端连接,电容c49的另一端与电阻r40的另一端连接,电阻r41的另一端依次与电阻r42的另一端及电阻r43的另一端连接;

12、电阻r38的另一端依次与电容c54的另一端及电阻r47的一端连接,电阻r47的另一端与电阻r46的一端连接,电阻r46的另一端依次与电容c58的一端及芯片u5的第三端连接,芯片u5的第一端依次与电容c57的一端及电阻r54的一端连接,电阻r54的另一端与电容c63的一端连接,电容c63的另一端依次与电容c57的另一端、芯片u5的第二端、电容c58的另一端及电容c59的一端连接并接地,电容c59的另一端与芯片u5的第五端连接,芯片u5的第六端与电阻r52连接。

13、进一步的,变压器电路包括电容ec2、功率表p1、电容c36、电阻r21、电阻r22、电容c32、电阻r30、电阻r29、二极管d6、电容c44、电感l5及变压器t1c,变压器电路的侧边还依次设置有mos管q12,电阻r53、电阻r45、二极管d7、电阻r50、电阻r59、电阻r55及电阻r56;

14、pwm电路包括芯片u6、电阻r63、电阻r65、电容c74、电容c76、电容c77、电阻r67、电阻r66、电容c75、光电晶体管u7b,二极管zd11及热敏电阻ntc1;

15、其中,电容ec2的一端与电容ec1的一端连接,电容ec2的另一端依次与电容ec1的另一端及功率表p1的一端连接,功率表p1的另一端与电容c36的一端连接,电容c36的另一端与电容ec1的一端连接,且电容c36的另一端依次与电阻r21的一端、电阻r22的一端、电容c32的一端及变压器t1c的第一端连接,电阻r21的另一端依次与电阻r22的另一端、电容c32的另一端、电阻r30的一端及电阻r29的一端连接,电阻r30的另一端依次与电阻r29的另一端、二极管d6的负极及电容c44的一端连接,二极管d6的正极依次与电容c44的另一端、电感l5的一端及mos管q12的漏极连接,电感l5的另一端与变压器t1c的第二端连接,变压器t1c的第七端与输出滤波电路连接,变压器t1c的第八端与输出同步整流电路连接;

16、mos管q12的栅极依次与电阻r53的一端、电阻r45的一端及电阻r50的一端连接,电阻r45的另一端与二极管d7的正极连接,二极管d7的负极与电阻r50的另一端连接,mos管q12的源极依次与电阻r53的另一端、电阻r67的一端、电阻r56的一端、电阻r59的一端及电阻r55的一端连接,电阻r56的另一端依次与电阻r59的另一端及电阻r55的另一端连接并接地;

17、电阻r67的另一端依次与电容c77的一端及芯片u6的第五端连接,芯片u6的第四端与电容c76的一端连接,电容c76的另一端依次与芯片u6的第六端、电容c74的一端、电容c77的另一端、电容c75的一端、光电晶体管u7b的第一端及二极管zd11的正极连接,电容c74的另一端与芯片u6的第八端连接,二极管zd11的负极依次与光电晶体管u7b的第二端及电阻r66的一端连接,电阻r66的另一端依次与芯片u6的第三端及电容c75的另一端连接,芯片u6的第一端与热敏电阻ntc1的一端连接,热敏电阻ntc1的另一端接地,芯片u6的第十端与电阻r65的一端连接,电阻r65的另一端与电阻r63的一端连接。

18、进一步的,输出同步整流电路包括电阻r25、电阻r31、电容c34、mos管q9及电阻r39;输出同步整流电路的侧边还依次设置有电阻r48、电阻r60、芯片u4、电容c62、电容c60及电容c61;

19、输出滤波电路包括电容c38、电容c39及电容c40;

20、其中,电阻r25的一端依次与电阻r31的一端、变压器t1c的第八端、mos管q9的漏极及电阻r48的一端连接,电阻r25的另一端依次与电阻r31的另一端及电容c34的一端连接,电容c34的另一端依次与mos管q9的源极、电容c38的一端、电容c39的一端及电容c40的一端连接,电容c40的另一端依次与电容c39的另一端、是电容c38的另一端及变压器t1c的第七端连接,mos管q9的栅极与电阻r39的一端连接,电阻r39的另一端接地;

21、电阻r48的另一端与芯片u4的第六端连接,芯片u4的第三端与电阻r60的一端连接,电阻r60的另一端接地,芯片u4的第一端与电容c61的一端连接,电容c61的另一端依次与电容c60的一端、电容c62的一端及芯片u4的第二端连接,电容c60的另一端依次与电容c62的另一端及芯片u4的第四端连接。

22、进一步的,协议ic控制电路包括芯片u1、芯片u3、电容c12、电容c11、电阻r7、电容c19、电容c20、电阻r8、电容c1、mos管q1、电阻r4、电阻r3、电容c3、电容c6、电容c10、电容c22、电容c23、电容c24、电容c21、电容c53、电容c52、电阻r57、电容c64、电容c65、电阻r58、电容c66、电容c67、电容c68、电容c69、电容c43、电容c51、电容c28、电阻r26、电阻r27、mos管q6及电容c25;

23、协议ic控制电路的侧边还依次设置有mos管q3、电阻r2、电容c4、电感l1、电容c9、电容c8、电容c7、电阻r1、电容c2、电容c5、mos管q2、电容c13、mos管q8、电阻r18、电容c31、电感l2、电容c50、电容c47、电容c46、电容c48、电阻r17、电容c26、电容c33、mos管q7、电容c55、电阻r64、电容c71、电容c72、mos管q13;

24、其中,芯片u1的第一端与电容c22的一端连接,电容c22的另一端依次与芯片u1的第二十九端、芯片u1的第二十六端、电容c20的一端、电容c19的一端、电阻r7的一端、电容c11的一端、电容c12的一端、电容c23的一端、电容c24的一端、电容c21的一端、芯片u1的第五端、电容c10的一端、电容c6的一端、mos管q3的第一端至第三端、电容c4的一端、电容c9的一端、电容c8的一端、电容c7的一端、电容c5的一端、电容c13的一端及第一type-c输出模块连接并接地,电容c23的另一端与芯片u1的第二端连接,电容c24的另一端与芯片u1的第三端连接,电容c21的另一端与芯片u1的第四端连接,电容c6的另一端与芯片u1的第十四端连接,电容c10的另一端与芯片u1的第十二端连接,电容c20的另一端与电阻r8的一端连接,电阻r8的另一端依次与芯片u1的第二十五端及电容c19的另一端连接,电阻r7的另一端与芯片u1的第二十四端连接,电容c12的另一端依次与电容c11的另一端、电容c1的一端、mos管q1的第五端至第八端及芯片u1的第十九端连接,mos管q1的第四端与电阻r4的一端连接,电阻r4的另一端与芯片u1的第十七端连接,芯片u1的第十六端与电阻r3的一端连接,电阻r3的另一端与mos管q3的第四端连接,mos管q1的第一端依次与mos管q1的第二端、mos管q1的第三端、芯片u1的第十八端、电容c3的一端、mos管q3的第五端至第八端、电阻r2的一端及电感l1的一端连接,电容c3的另一端与芯片u1的第十五端连接,电阻r2的另一端与电容c4的另一端连接,电感l1的另一端依次与电容c9的另一端、电容c8的另一端、电容c7的另一端、电容c1的另一端、电阻r1的一端、电容c2的一端、芯片u1的第六端、芯片u1的第八端及芯片u1的第九端连接,芯片u1的第七端依次与电容c2的另一端、电阻r1的另一端、mos管q2的第五端至第八端及电容c5的另一端连接,mos管q2的第一端依次与mos管q2的第二端、mos管q2的第三端、第一type-c输出模块、电容c13的另一端及芯片u1的第十端连接;

25、芯片u3的第一端与电容c66的一端连接,电容c66的另一端依次与芯片u3的第二十九端、芯片u3的第二十六端、电容c65的一端、电容c64的一端、电阻r57的一端、电容c52的一端、电容c53的一端、电容c67的一端、电容c68的一端、电容c69的一端、芯片u3的第五端、电容c51的一端、电容c43的一端、mos管q8的第一至第三端、电容c31的一端、电容c50的一端、电容c47的一端、电容c46的一端、电容c48的一端、电容c33的一端、电容c55的一端及第二type-c输出模块连接并接地,电容c67的另一端与芯片u3的第二端连接,电容c68的另一端与芯片u3的第三端连接,电容c69的另一端与芯片u3的第四端连接,电容c65的另一端与电阻r58的一端连接,电阻r58的另一端依次与芯片u3的第二十五端及电容c64的另一端连接,电阻r57的另一端与芯片u3的第二十四端连接,电容c53的另一端依次与电容c52的另一端、电容c25的一端、mos管q6的第五端至第八端及芯片u3的第十九端连接,mos管q6的第四端与电阻r27的一端连接,电阻r27的另一端与芯片u3的第十七端连接,芯片u3的第十六端与电阻r26的一端连接,电阻r26的另一端与芯片q8的第四端连接,mos管q6的第一端依次与mos管q6的第二端、mos管q6的第三端、芯片u3的第十八端、电容c28的一端、mos管q8的第五端至第八端、电阻r18的一端及电感l2的一端连接,电阻r18的另一端与电容c31的另一端连接,电容c28的另一端与芯片u3的第十五端连接,电感l2的另一端依次与电容c25的另一端、电容c50的另一端、电容c47的另一端、电容c46的另一端、电容c48的另一端、电阻r17的一端、电容c26的一端、芯片u3的第六端连接、电阻r64的一端及电容c71的一端连接,电阻r17的另一端依次与电容c26的另一端、芯片u3的第七端、mos管q7的第五端至第八端及电容c33的另一端连接,mos管q7的第一端依次与mos管q7的第二端、mos管q7的第三端、第二type-c输出模块、电容c55的另一端及芯片u3的第十端连接;

26、电阻r64的另一端依次与电容c71的另一端、mos管q13的第五端至第八端及电容c72的一端连接,电容c72的另一端与usb-a输出模块连接并接地,mos管q13的第一端依次与mos管q13的第二端、mos管q13的第三端及usb-a输出模块连接。

27、进一步的,第一type-c输出模块包括usb1、二极管zd1、二极管zd2、二极管zd3、二极管zd4及二极管zd5;

28、第二type-c输出模块包括usb2、二极管zd6、二极管zd7、二极管zd8、二极管zd9及二极管zd10;

29、usb-a输出模块包括usb3、电容c70及电容c73;

30、其中,usb1的a4端依次与mos管q2的第一端及二极管zd1的第二端连接,usb1的a5端与二极管zd2的第二端连接,usb1的b7端与二极管zd3的第二端连接,usb1的a6端与二极管zd4的第二端连接,usb1的b5端与二极管zd5的第二端连接,二极管zd1的第一端依次与二极管zd2的第一端、二极管zd3的第一端、二极管zd4的第一端、二极管zd5的第一端及电容c13的一端连接;

31、usb2的a4端依次与mos管q7的第一端及二极管zd6的第二端连接,usb2的a5端与二极管zd7的第二端连接,usb2的b7端与二极管zd8的第二端连接,usb2的a6端与二极管zd9的第二端连接,usb2的b5端与二极管zd10的第二端连接,二极管zd6的第一端依次与二极管zd7的第一端、二极管zd8的第一端、二极管zd9的第一端、二极管zd10的第一端及电容c55的一端连接;

32、usb3的第一端依次与电容c73的一端、电容c70的一端及mos管q13的第一端连接,电容c70的另一端依次与电容c72的另一端、电容c73的另一端及usb3的第四端至第六端连接。

33、进一步的,弹簧针输出模块包括连接器j1、电阻r9、电容c16、电容c17、电容c18、芯片u2、电阻r14、电阻r13、电容c15、电阻r5、mos管q4、电阻r6、电容c14、电阻r10、三极管q5、电阻r15、电阻r11、电阻r12及电阻r16;

34、其中,连接器j1的第一端与电阻r9的一端连接,电阻r9的另一端接地,连接器j1的第四端依次与电容c16的一端、电容c17的一端、电容c18的一端、电阻r14的一端、电阻r10的一端、三极管q5的第二端、电阻r15的一端及电阻r16的一端连接并接地,电阻r16的另一端依次与电阻r12的一端及电阻r11的一端连接,电阻r11的另一端依次与电容c14的一端、电阻r6的一端及mos管q4的源极连接,电容c14的另一端依次与电阻r6的另一端、mos管q4的栅极、电阻r10的另一端及三极管q5的第三端连接,三极管q5的第一端与电阻r15的另一端连接,mos管q4的漏极依次与电阻r5的一端、电容c15的一端及芯片u2的第四端连接,电阻r5的另一端依次与电容c15的另一端、芯片u2的第五端、电容c17的另一端、电容c16的另一端及连接器j1的第五端连接,芯片u2的第六端与电阻r13的一端连接,芯片u2的第三端与电容c18的另一端连接,芯片u2的第二端依次与芯片u2的第一端及电阻r14的另一端连接。

35、本发明的有益效果为:

36、(1)本发明提供的一种氮化镓多功能充电器采用层叠设计,能够节省充电器空间,内部结构紧凑,实现了多功能多口快充,大大提升了便捷性,便于携带,同时有效缩短了手机等电子设备的充电时间。

37、(2)本发明采用卧置电解电容,超薄变压器,超高集成芯片,极大的节省了空间;附带有1个usb-a口、2个type-c口和1个pogopin口,实现多口与多功能快充;采用inn650d260a氮化镓开关管,在同功率下次级氮化镓效率更高,体积更小。

- 还没有人留言评论。精彩留言会获得点赞!