用于输出驱动器的控制电路和包括控制电路的输出驱动器的制作方法

本公开一般涉及一种输出驱动器,特别是涉及一种用于如权利要求1的前序部分所述的具有转换速率控制电路的输出驱动器的控制电路。

背景技术:

1、输出驱动器是用于驱动输出焊盘的电路,预定负载连接到该输出焊盘以便从半导体装置输出数据。推挽(push-pull)型驱动器被认为是广泛使用的输出驱动器,并且通常与驱动器结合使用转换速率控制电路,用于控制驱动器的输出转换速率。

2、转换速率示出了输出信号的电压电平变化有多快。转换速率被定义为表示电压电平变化与单位时间之间的比率的斜率。

3、像集成电路间(i2c)、电磁干扰(emi)等应用受影响的电路需要慢转变输出信号以最小化emi,以满足上升/下降时间的标准要求。对于这样的应用,需要以受控的方式限制输出的上升时间和下降时间。

4、传统上已知的典型转换速率控制电路通过将明确定义的电流注入驱动器中来控制输出转换速率。该电流总是良好受控的电流,并且涉及大的导通时间。

5、us2010/176783a1公开了一种开关装置驱动电路,用于接收脉冲信号,并在对应于脉冲信号的预定时段内将驱动信号输出到开关装置的控制端子,该开关装置包括:功率转换电路,以及控制电路,用于将作为驱动信号提供到开关装置的控制端子的电压改变为不同于预定电压的电压,或将作为驱动信号流经开关装置的控制端子的电流改变为不同于预定电流的电流;以及控制电压检测电路,用于检测开关装置的控制端子的电压。

6、us10790818b1公开了一种栅极驱动器电路,包括第一电源轨,其提供第一固定电源电压;第二电源轨,其提供第二固定电源电压;晶体管,其包括具有栅极电压的栅极端子;以及栅极驱动器集成电路(ic),其被供应有第一固定电源电压和第二固定电源电压,栅极驱动器ic包括输出端子,该输出端子被配置为在输出端子处提供栅极驱动电压,以便在开关状态之间驱动晶体管。

7、us2006/119326a1公开了一种开关电压调节器,其包括开关晶体管和预驱动器电路,该开关晶体管被连接以响应于使晶体管循环导通和截止的控制信号而在电源电压和第一节点之间传导电流,该预驱动器电路提供控制信号。

8、对于在满足转换速率要求的同时需要小的等待时间的转换速率控制电路应用,期望的是可缩短导通时间。

9、考虑到上述情况,期望可以改善具有转换速率控制电路的输出驱动器的导通时间,而不影响转换速率。

技术实现思路

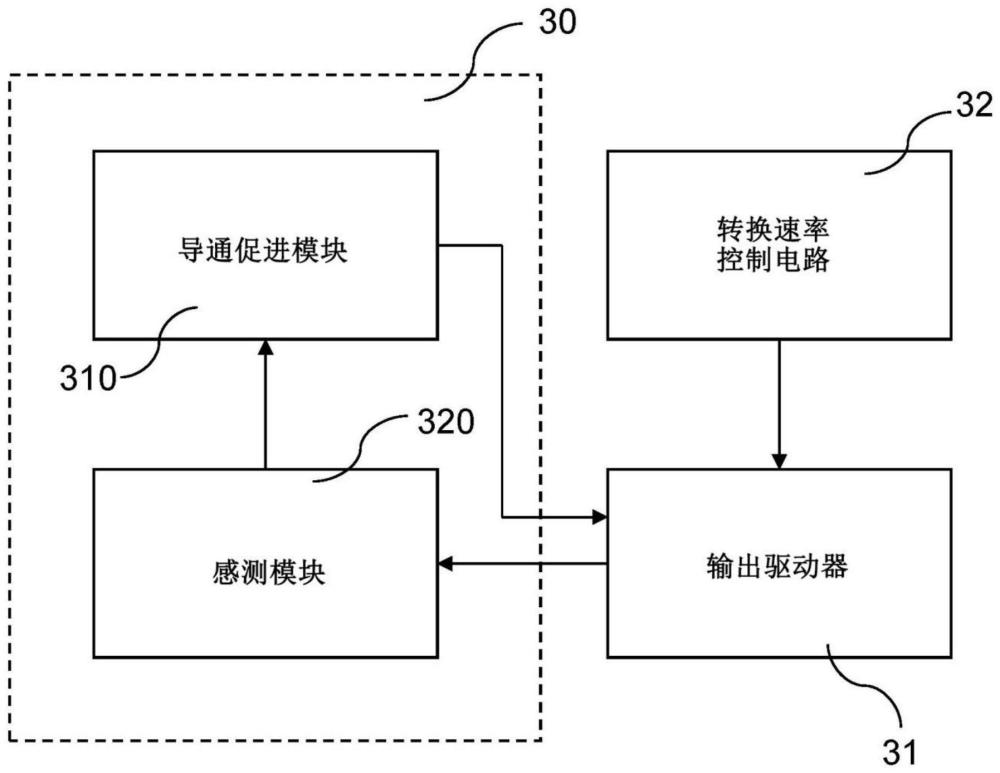

1、在本公开的第一方面中,提出了一种用于输出驱动器的控制电路,输出驱动器具有如权利要求1的特征部分中所限定的转换速率控制电路。控制电路包括:

2、导通促进模块,其具有控制输入,并且被配置为连接到输出驱动器,并且响应于控制输入处的控制电压向输出驱动器供应补充电压;

3、以及

4、感测模块,其被配置为连接到导通促进模块和输出驱动器,并且响应于由感测模块感测到的输出驱动器的输入电压而关断导通促进模块。

5、本公开基于这样的认识,通过经由导通促进模块向输出驱动器供应补充电压,可以减少或缩短输出驱动器的导通时间。除了由用于导通输出驱动器的转换速率控制电路注入的电流之外,还供应补充电压。

6、补充电压与由转换速率控制电路注入的电流相结合,确保了输出驱动器在短时间内导通。通过例如对用作输出驱动器的晶体管的栅极充电来导通输出驱动器所需的时间不依赖于在随后的转换速率时段期间使用的偏置电流。

7、导通促进模块仅在输出驱动器的导通时段期间操作。因此,感测模块被配置为通过感测输出驱动器的输入电压来关断导通促进模块。一旦输入电压达到阈值,则导通促进模块被关断,从而确保转换速率时段保持不受影响。

8、在本公开的示例中,导通促进模块包括导通路径,该导通路径被配置为连接到输出驱动器的输入端子并且响应于控制电压将电源电压连接到输出驱动器的输入端子。

9、这种导通路径被配置为向输出驱动器的输入端子供应补充电压。当控制电压被施加到导通促进模块的控制输入时,通过将包括输出驱动器的系统的电源电压连接到输出驱动器的输入端子来提供补充电压。

10、在本公开的示例中,导通路径包括串联的第一开关与第二开关,第一开关的使能端子耦接到控制电压,第二开关的使能端子耦接到电源电压与感测模块的输出端子,第二开关的输出端子被配置为连接到输出驱动器的输入端子。

11、这种导通路径连接到输出驱动器的输入端子。当控制电压施加在控制输入上时,它允许电源电压作为补充电压供应给输出驱动器的输入端子。此外,当输出驱动器的输入端子处的电压足够高时,在来自感测模块的输出下断开导通路径。

12、在本公开的示例中,第一开关包括第一pmos晶体管,第二开关包括第二pmos晶体管,第一pmos晶体管的源极耦接至电源电压,第一pmos晶体管的漏极耦接至第二pmos晶体管的源极,第二开关的漏极被配置为连接至输出驱动器的输入端子。

13、第一pmos晶体管和第二pmos晶体管串联连接。如上所述,第一pmos晶体管的使能端子(即栅极)耦接至控制电压。因此,在施加控制电压时,第一pmos晶体管被启用,从而也启用第二pmos晶体管。因此,电源电压经由输出端子或第二pmos晶体管的漏极被供应给输出驱动器的输入端子。

14、在本公开的示例中,第一pmos晶体管的栅极经由第一反相器耦接至控制电压,第二pmos晶体管的栅极经由串联连接的第二反相器和上拉电阻器耦接至电源电压。

15、这允许第一pmos晶体管以逻辑高电压被启用。在第一pmos晶体管导通的同时,第二pmos晶体管通过电源电压而被启用。

16、在本公开的示例中,感测模块包括第三开关,该第三开关被配置为使其输入端子连接到输出驱动器的输入端子,并且使其输出端子耦接到电源电压和第二开关的使能端子。

17、第三开关的输入端子被配置为感测输出驱动器的输入电压。因此,第三开关在输出驱动器的输入电压的控制下操作,从而通过关断导通路径的第二开关来关断导通促进模块的导通路径。

18、在本公开的示例中,第三开关包括第一nmos晶体管,第一nmos晶体管的源极经由第二nmos晶体管连接至控制电压。

19、在本公开的示例中,第二nmos晶体管的源极耦接到gnd,第二nmos晶体管的栅极耦接到控制电压。

20、这确保了当控制电压处于逻辑低电平时导通路径被禁用。

21、在本公开的示例中,第一nmos晶体管的输出端子耦接至第二反相器与上拉电阻之间的节点。

22、因此,确保了直到输出驱动器的输入电压达到启用第一nmos晶体管的阈值时,导通路径的第二pmos晶体管才受感测模块的影响。

23、在本公开的示例中,用于输出驱动器的控制电路还包括限流电阻器,限流电阻器具有可连接至输出驱动器的输入端子的第一端子以及耦接至导通促进模块与感测模块的第二端子。

24、限流电阻器被配置为防止输出驱动器的栅极电压中的任何尖峰,并且防止在禁用导通促进模块之前输出被快速放电。因此,输出驱动器的输出在整个转换时段内具有恒定转换速率。

25、在本公开的示例中,限流电阻器的第二端子耦接到第二pmos开关的漏极与第三开关的感测端子。

26、由此,限流电阻器连接在导通促进模块的输出以及感测模块的输入与输出驱动器的输入端子之间。

27、在本公开的示例中,限流电阻器具有在200欧姆到600欧姆的范围内的电阻。

28、在限定范围内的电阻可以有效地防止输出驱动器的栅极电压中的尖峰,并有助于稳定输出。

29、本公开的第二方面呈现一种输出驱动器,其包括转换速率控制电路和根据本公开的第一方面的用于转换速率控制电路的控制电路。

30、在本公开的示例中,输出驱动器包括开路漏极输出驱动器。

31、在本公开的另一示例中,输出驱动器包括推挽型驱动器。

32、如本公开的第一方面中所描述的控制电路可有利地用于开路漏极输出驱动器和推挽型驱动器两者中,从而允许两个驱动器具有低传播延迟以及良好受控的转换速率。

33、从下面参照附图的描述中,将最好地理解本公开的上述和其它特征和优点。在附图中,相同的附图标记表示相同的部件或执行相同或相当功能或操作的部件。

- 还没有人留言评论。精彩留言会获得点赞!