一种多相控制电路、芯片及多相并联电路的制作方法

本技术涉及开关电源,特别是涉及电源方向的一种多相控制电路、芯片及多相并联电路。

背景技术:

1、在开关电源技术中,为了满足大功率负载的电流需求通常使用多相控制器的两个或多个相位来满足高负载电流需求。现有技术中的多相控制器大多分为菊花链结构电路和锁相环结构电路。

2、其中,锁相环结构电路,其一般需要补偿网络,若不设置补偿网络在面向宽范围的频率调制时会出现稳定性问题,而若外置补偿电路则会消耗较多资源,增加了成本;且锁相环路需要建立时间,做不到快速响应。菊花链结构电路,由于其是使用数字状态机实现闭环链式控制,因此抗干扰性差,一旦数据链中某路因干扰发生故障,就会对后级相位造成不可恢复的影响。

3、因此,亟需一种稳定性好,响应速度快、抗干扰能力强的多相控制电路。

技术实现思路

1、为了解决现有技术存在的不足,本技术的目的在于提供一种多相控制电路,稳定性好,响应速度快、抗干扰能力强。

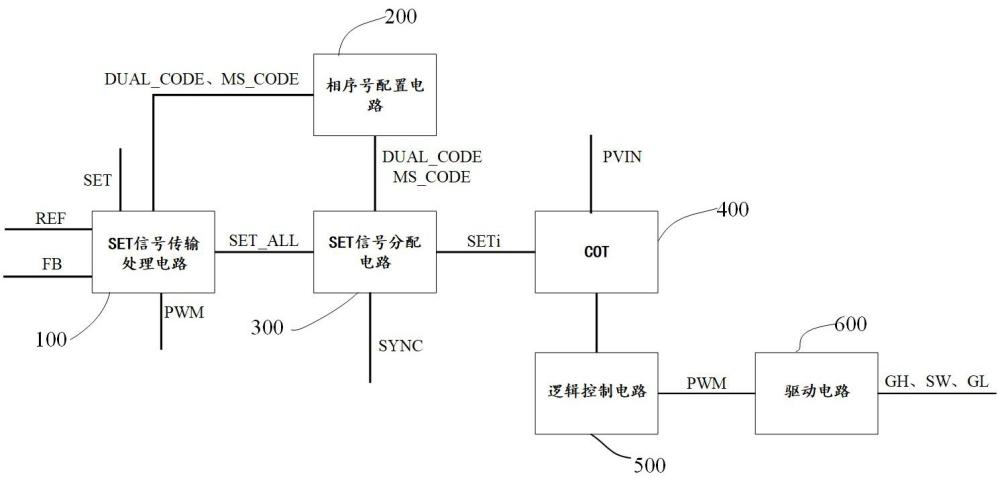

2、为实现上述目的,本技术提供一种多相控制电路,包括:

3、相序号配置电路,被配置为:根据相序电阻的阻值,生成相序号和工作模式信号;

4、控制信号传输处理电路,与所述相序号配置电路连接,被配置为:在所述相序号为主相序号时,生成多相控制信号;在所述相序号为从相序号时,接收多相控制信号;对所述多相控制信号进行边沿检测,生成总控制信号;

5、信号分配电路,与所述相序号配置电路和所述控制信号传输处理电路连接,被配置为:根据相序号和工作模式信号,从所述总控制信号中分配出对应相的相控制信号。

6、进一步地,所述控制信号传输处理电路,包括:

7、第一放大器,正向输入端接收参考电压信号,反向输入端接收反馈电压信号,输出端输出第一电压信号;

8、第一比较器,正向输入端接收斜坡电压信号和所述第一电压信号,反向输入端接收参考电压信号和反馈电压信号,输出第一控制信号;

9、脉宽检测与分割电路,与所述第一比较器的输出端连接,被配置为:检测所述第一控制信号的脉宽并分割至预定脉宽范围后作为控制脉冲信号输出;

10、脉宽延展电路,与所述脉宽检测与分割电路连接,被配置为:在所述相序号为主相序号且工作模式信号为多相工作模式时,将控制脉冲信号的脉宽延展为恒定值后作为多相控制信号输出;

11、边沿检测电路,与所述脉宽检测与分割电路和所述脉宽延展电路连接,被配置为:在工作模式信号为单相工作模式时,将控制脉冲信号作为总控制信号输出;在工作模式信号为多相工作模式时,将多相控制信号进行边沿检测与延时处理后作为总控制信号输出。

12、进一步地,所述脉宽检测与分割电路,包括:

13、脉宽检测电路,包括第一电阻,所述第一电阻的第一端被配置为接收第一控制信号,第二端被配置为输出端,所述第二端还通过第一电容cs1与公共地端连接。

14、进一步地,所述脉宽检测与分割电路,还包括:

15、脉冲分割电路,包括:

16、第一反相器,输入端与所述脉宽检测电路的输出端连接,输出端与第一或门的一个输入端连接;

17、第一或门,第一或门的另一个输入端与第三反相器的输出端连接,输出端与第一nmos管和第一pmos管的栅极均连接;

18、第二电阻,设置在所述第一nmos管的漏极和所述第一pmos管的漏极之间;

19、第二电容,设置在所述第一nmos管的源极和漏极之间;

20、第一缓冲器,输入端与所述第一nmos管的漏极连接,输出端与第二反相器的输入端和第一异或门的一个输入端连接;

21、第二反相器,输出端与所述第三反相器的输入端连接;

22、第三电容,设置在所述第三反相器的输出端与公共地端之间;

23、第一异或门,第一异或门的另一输入端被配置为接收第一控制信号,输出端与第一与门的一个输入端连接;

24、第一与门,第一与门的另一输入端被配置为接收第一控制信号,输出端被配置为输出控制脉冲信号;

25、供电端,与所述第一pmos管的漏极连接;

26、公共地端,与所述第一nmos管的源极连接。

27、进一步地,所述脉宽延展电路,包括:

28、d触发器,d端被配置为接收高电平,clk端被配置为接收控制脉冲信号,reset端和q端之间设置有100ns的延时电路;

29、第二与门,两输入端分别被配置为接收相序号和工作模式信号,输出端与第一与非门的一个输入端连接;

30、第一与非门,第一与门非的另一个输入端与所述d触发器的q端连接,输出端与第二缓冲器的输入端连接;

31、第四反相器,输入端与第二与门的输出端连接,输出端与第一或非门的一个输入端连接;

32、第一或非门,所述第一或非门的另一个输入端与所述d触发器的q端连接,输出端与所述第三缓冲器的输入端连接;

33、第二缓冲器,输出端与第二pmos管的栅极连接,所述第二pmos管的源极与供电端连接,第二pmos管的漏极被配置为输出多相控制信号;

34、第三缓冲器,输出端与第二nmos管的栅极连接,所述第二nmos管的源极与公共地端连接,第二nmos管的漏极与第二pmos管的漏极连接。

35、进一步地,所述边沿检测电路,包括:

36、第四缓冲器,输入端被配置为接收多相控制信号,输出端通过20ns的延时电路与第二异或门的一个输入端连接;

37、第二异或门,第二异或门的另一个输入端与第四缓冲器的输出端连接,输出端与第三与门的一个输入端连接;

38、第三与门,第三与门的另一个输入端与第四缓冲器的输出端连接,输出端与第二或门的一个输入端连接;

39、第五反相器,输入端被配置为接收工作模式信号,输出端与第四与门的一个输入端连接;

40、第四与门,第四与门的另一个输入端被配置为接收控制脉冲信号,输出端与第二或门的另一个输入端连接;

41、第二或门,输出端被配置为输出总控制信号。

42、进一步地,所述相序号配置电路包括:

43、第一电流源,正端与电源连接,负端经相序电阻接地;

44、第二电流源,正端与电源连接,负端经若干串联的基准电阻接地;

45、传输门阵列,被配置为:接收各所述基准电阻的电压信号,按照时钟选通输出;

46、第二比较器,正相输入端与所述传输门阵列的输出端连接,反相输入端与所述第一电流源的负端连接,输出端与所述编程逻辑处理单元连接;

47、编程逻辑处理单元,用于将所述第二比较器在不同时钟相位下输出的电平序列转化为相序号和工作模式信号。

48、进一步的,所述多相控制电路还包括:

49、cot单元,与所述信号分配电路连接,被配置为根据所述相控制信号确定pwm信号的开启时刻,根据输入电压、输出电压控制pwm信号的导通时间;

50、逻辑控制单元,与所述cot单元连接,用于生成pwm信号;

51、驱动单元,与所述逻辑控制单元连接,用于生成驱动信号。

52、为实现上述目的,本技术还提供一种多相并联控制芯片,包括,如上所述的一种多相控制电路。

53、为实现上述目的,本技术还提供一种多相并联电路,包括:

54、如上所述的多相并联控制芯片。

55、本技术的一种多相控制电路与现有技术相比,具有如下有益效果:

56、本技术的多相控制电路采用开环方式实现各相控制信号的分配,避免了稳定性问题,无需建立时间;

57、本技术的多相控制电路各相独立工作,多相控制信号set上的偶发干扰不影响多相之间的持续联动,可恢复;

58、本技术的多相控制电路无需额外的电路或者环路即可实现多相联动的动态快速响应;

59、本技术的多相控制电路通过设置脉宽延展和边沿检测电路,去除了不同相之间传输路径上的l/c寄生对窄脉宽的负面影响。

60、本技术的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本技术而了解。

- 还没有人留言评论。精彩留言会获得点赞!