一种高边开关电路的制作方法

本公开涉及开关电源,涉及但不限于一种高边开关电路。

背景技术:

1、金属氧化物半导体(metal oxide semiconductor,mos)高边开关因其低损耗、易驱动、可靠性高和接近理想的开关特性,目前被广泛应用于汽车、工业、移动设备等众多领域。

2、相关技术中,通常采用p型mos管(pmos管)作为高边开关,然而,pmos管作为高边开关具有两个缺点:一是pmos管的载流子迁移率较低,达到相同的导通电阻要求需要更多的面积;二是采用pmos管作为高边开关时的栅源电压受电源波动影响较大,使得高边开关导通电阻不稳定。

技术实现思路

1、有鉴于此,本公开实施例提供一种高边开关电路。

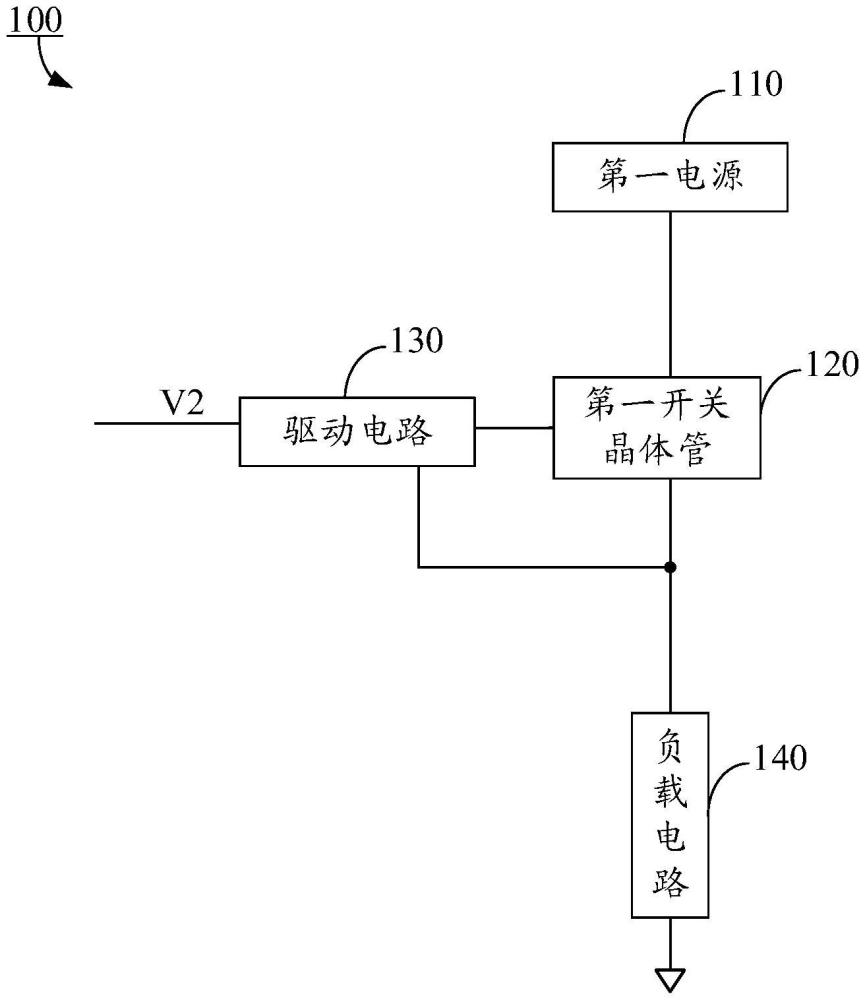

2、本公开实施例提供的一种高边开关电路,所述高边开关电路包括:第一电源、第一开关晶体管和驱动电路,所述第一开关晶体管的第一端与所述第一电源连接,所述第一开关晶体管的第二端与负载电路连接,所述第一开关晶体管的栅极端和第二端均与所述驱动电路连接;其中:

3、所述第一电源,用于向所述第一开关晶体管提供第一电压;

4、所述驱动电路,用于接收第二电压,并对所述第二电压进行抬升处理,得到偏置电压后,根据所述偏置电压控制是否导通所述第一开关晶体管;其中,所述抬升处理使得所述第一开关晶体管的栅极端的电压和所述第一开关晶体管的第二端的电压之差大于预设差值;在所述第一开关晶体管导通的情况下,所述第一开关晶体管将所述第一电压传输至所述负载电路。

5、在一些实施例中,所述高边开关电路还包括第二电源,所述驱动电路包括:第一电荷泵电路和第二电荷泵电路;所述第一电荷泵电路的第一端与所述第二电源耦接,所述第一电荷泵电路的第二端与所述第二电荷泵电路的第一端连接;所述第二电荷泵电路的第二端与所述第一开关晶体管的栅极端连接;其中:

6、所述第二电源,用于提供所述第二电压;

7、所述第一电荷泵电路,用于将所述第二电压进行抬升,得到预设电压,并将所述预设电压传输至所述第二电荷泵电路;

8、所述第二电荷泵电路,用于将所述预设电压进行抬升,得到所述偏置电压,并将所述偏置电压施加至所述第一开关晶体管的栅极端;其中,所述预设电压和所述预设差值的数值相等;在所述高边开关电路工作期间,所述第二电源和所述第一电荷泵电路始终保持开启状态。

9、在一些实施例中,所述第二电荷泵电路的第三端与所述第一开关晶体管的第二端连接;其中:

10、所述第二电荷泵电路,还用于接收所述第一开关晶体管的第二端电压,并根据所述第一开关晶体管的第二端的电压将所述预设电压进行抬升,得到所述偏置电压。

11、在一些实施例中,所述高边开关电路还包括第二开关晶体管和第三电源;所述第二开关晶体管的第一端与所述第三电源连接,所述第二开关晶体管的第二端与所述负载电路连接,所述第二开关晶体管的栅极端和所述第二开关晶体管的第二端与所述驱动电路连接;其中:

12、所述第三电源,用于向所述第二开关晶体管提供第三电压;

13、所述驱动电路,在对所述第二电压进行抬升处理,得到所述偏置电压后,根据所述偏置电压控制是否导通所述第二开关晶体管;其中,所述抬升处理还使得所述第二开关晶体管的栅极端的电压和所述第二开关晶体管的第二端的电压之差大于所述预设差值;在所述第二开关晶体管导通的情况下,所述第二开关晶体管将所述第三电压传输至所述负载电路。

14、在一些实施例中,所述第一开关晶体管和所述第二开关晶体管均为nmos管。

15、在一些实施例中,所述驱动电路还包括第三电荷泵电路;所述第三电荷泵电路的第一端与所述第一电荷泵电路的第二端连接,所述第三电荷泵电路的第二端与所述第二开关晶体管的栅极端连接,所述第三电荷泵电路的第三端与所述第二开关晶体管的第二端连接;其中:

16、所述第三电荷泵电路,用于将所述第二开关晶体管的第二端的电压抬升所述预设差值,得到所述偏置电压,并将所述偏置电压施加至所述第二开关晶体管的栅极端;所述第二电荷泵电路和/或所述第三电荷泵电路根据高边开关电路的工作状态进行开启或者关闭。

17、在一些实施例中,所述高边开关电路还包括逻辑控制电路;所述逻辑控制电路与所述第二电荷泵电路的控制端连接;其中:

18、所述逻辑控制电路,用于接收初始控制信号,对所述初始控制信号进行逻辑处理,在所述初始控制信号指示开启所述第一开关晶体管的情况下,生成处于使能状态的第一控制信号,并将所述第一控制信号传输至所述第二电荷泵电路;

19、其中,在所述第一控制信号处于使能状态的情况下,所述第二电荷泵电路开启,所述第一开关晶体管导通;在所述第一控制信号处于非使能状态的情况下,所述第二电荷泵电路关闭,所述第一开关晶体管断开。

20、在一些实施例中,所述逻辑控制电路还与所述第三电荷泵电路的控制端连接;其中:

21、所述逻辑控制电路,还用于在所述初始控制信号指示导通所述第一开关晶体管且关闭所述第二开关晶体管的情况下,生成处于使能状态的第一控制信号以及处于非使能状态的第二控制信号;或者,在所述初始控制信号指示关闭所述第一开关晶体管且导通所述第二开关晶体管的情况下,生成处于非使能状态的第一控制信号以及处于使能状态的所述第二控制信号;并将所述第一控制信号传输至所述第二电荷泵电路,以及将所述第二控制信号传输至所述第三电荷泵电路;

22、其中,在所述第二控制信号处于使能状态的情况下,所述第三电荷泵电路开启,所述第二开关晶体管导通;在所述第二控制信号处于非使能状态的情况下,所述第三电荷泵电路关闭,所述第二开关晶体管断开。

23、在一些实施例中,所述高边开关电路还包括:死区时间控制电路;所述死区时间控制电路的第一输出端与所述第二电荷泵电路的控制端连接,所述死区时间控制电路的第二输出端和所述第三电荷泵电路的控制端连接;其中:

24、所述死区时间控制电路用于对第一控制信号和/或所述第二控制信号进行延迟处理后,分别将延迟处理后的所述第一控制信号传输至所述第二电荷泵电路、将延迟处理后的所述第二控制信号传输至所述第三电荷泵电路,使得在所述第二电荷泵电路关闭后,所述第三电荷泵电路延迟开启,或者,在所述第三电荷泵电路关闭后,所述第二电荷泵电路延迟开启。

25、在一些实施例中,所述死区时间控制电路包括逻辑处理电路和延时处理电路;

26、所述逻辑处理电路,用于接收所述第一控制信号和所述第二控制信号,并根据所述第一控制信号和所述第二控制信号进行逻辑处理,生成第一中间控制信号和第二中间控制信号;其中,若所述第一控制信号和所述第二控制信号均为第一电平状态,则所述第一中间控制信号和所述第二中间控制信号均为第二电平状态;否则,所述第一中间控制信号的电平状态与所述第一控制信号相同、所述第二中间控制信号的电平状态与所述第二控制信号相同;

27、所述延时处理电路,用于接收所述第一中间控制信号和所述第二中间控制信号,并根据所述第一中间控制信号和所述第二中间控制信号,生成第一目标控制信号和第二目标控制信号;其中,在所述第一中间控制信号和所述第二中间控制信号中的一者由所述第二电平状态变为所述第一电平状态时,间隔所述预设时间后,所述第一目标控制信号和所述第二目标控制信号中的一者由所述第二电平状态变为所述第一电平状态;

28、其中,所述第一目标控制信号为延迟处理后的所述第一控制信号;所述第二目标控制信号为延迟处理后的所述第二控制信号。

29、在一些实施例中,所述逻辑处理电路包括第一与非门、第一与门和第二与门;

30、所述第一与非门的第一输入端和所述第一与门的第一输入端均用于接收所述第一控制信号,所述第一与非门的第二输入端和所述第二与门的第二输入端均用于接收所述第二控制信号,所述第一与非门的输出端与所述第一与门的第二输入端和所述第二与门的第一输入端连接;

31、所述第一与门的输出端用于输出所述第一中间控制信号;

32、所述第二与门的输出端用于输出所述第二中间控制信号。

33、在一些实施例中,所述延时处理电路包括第二与非门、第一延时单元、第一或非门、第三非门、第三与非门、第二延时单元、第二或非门、第四非门、第五非门和第六非门;

34、所述第二与非门的第一输入端用于接收所述第一中间控制信号;所述第二与非门的第二输入端与所述第四非门的输出端连接,用于接收第四中间控制信号;所述第二与非门的输出端与所述第一延时单元的输入端和所述第一或非门的第一输入端连接;所述第一延时单元的输出端和所述第一或非门的第二输入端连接;所述第一或非门的输出端和所述第三非门的输入端连接;所述第三非门的输出端用于输出第三中间控制信号;

35、所述第三与非门的第一输入端用于接收所述第二中间控制信号;所述第三与非门的第二输入端与所述第三非门的输出端连接,用于接收所述第三中间控制信号;所述第三与非门的输出端与所述第二延时单元的输入端和所述第二或非门的第一输入端连接;所述第二延时单元的输出端和所述第二或非门的第二输入端连接;所述第二或非门的输出端和所述第四非门的输入端连接;所述第四非门的输出端用于输出所述第四中间控制信号;

36、所述第五非门的输入端用于接收所述第三中间控制信号,所述第五非门的输出端用于输出所述第一目标控制信号;

37、所述第六非门的输入端用于接收所述第四中间控制信号,所述第六非门的输出端用于输出所述第二目标控制信号。

38、在一些实施例中,所述第一电源的工作模式包括et模式或者apt模式;所述第三电源的工作模式包括et模式或者apt模式;其中,所述第一电源和所述第三电源的工作模式不同。

39、本公开实施例提供的一种高边开关电路,包括:第一电源、第一开关晶体管和驱动电路,第一开关晶体管的第一端与第一电源连接,第一开关晶体管的第二端与负载电路连接,第一开关晶体管的栅极端和第二端均与驱动电路连接;其中:第一电源,用于向第一开关晶体管提供第一电压;驱动电路,用于接收第二电压,并对第二电压进行抬升处理,得到偏置电压后,根据偏置电压控制是否导通第一开关晶体管;其中,抬升处理使得第一开关晶体管的栅极端的电压和第一开关晶体管的第二端的电压之差大于预设差值;在第一开关晶体管导通的情况下,第一开关晶体管将第一电压传输至负载电路。这样,由于驱动电路对接收到的第二电压进行抬升处理,使得第一开关晶体管的栅极电压较高,从而可以使得第一开关晶体管采用体积较小,且开关电阻稳定的nmos管作为高边开关,进而不仅可以减少高边开关电路的面积,还可以使得开关电阻稳定。

- 还没有人留言评论。精彩留言会获得点赞!