一种锁相环控制电路及锁相控制方法与流程

1.本发明涉及集成电路设计领域,尤其涉及一种锁相环控制电路及锁相控制方法。

背景技术:

2.锁相环(phase-locked loop,pll)是一种反馈控制电路,它利用外部输入的参考信号控制环路内部振荡信号的频率和相位。在处理电子信号的过程中,因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常广泛应用于闭环跟踪电路。在时钟领域,时钟锁相环被广泛应用于时钟的生成。

3.时钟锁相环通常由以下几个部分组成:鉴相器(phase detector,pd)、低通滤波器(low-pass filter,lpf)、压控振荡器(voltage-controlled oscillator,vco)和环路分频器(loop dividers,lpdiv)。现有技术中,通常在pll的输出端级联一个后分频器pstdiv,可以使得时钟输出范围更为大,或者是大幅度减小压控振荡器vco的工作范围,从而降低设计难度,提高可靠性。虽然级联的后分频器本质上不属于pll,但是由于其对后级系统所接收到的时钟影响较大,作为源头通常可以把它视为时钟锁相环的一部分对待。

4.鉴相器pd,是一个完成相位比较的单元,其作用是比较输入信号fin和反馈信号fback之间的相位差,它的输出平均值,如电压正比于两个输入信号之相位差。低通滤波器lpf,是一个有源或无源低通滤波器,其作用是滤除鉴相器输出电压中的高频分量,其中包括混频及其他的高频噪声,起到平滑滤波的作用,最终输出控制信号vc,lpf通常由电阻、电容或电感等组成,有时也包含运算放大器。压控振荡器vco,是一个振荡频率受控制电压vc控制的振荡器,其振荡频率与控制电压之间成单调关系,vco根据控制信号vc输出对应的振荡频率fosc。

5.如图1所示,在图1示出的锁相环结构中,环路分频器lpdiv,它决定了输入和输出时钟的倍率,其倍率可以是整数也可以是小数,输入和输出时钟的关系可以用式1来表示,且对于普通的pll,输出频率fout就是振荡器频率fosc,其中,n(lpdiv)为lpdiv的分频系数:

6.fosc=n(lpdiv)

·

fin

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

式1

7.通常来说,pll时钟锁定后,由于反馈时钟与输入时钟的相位差稳定,因此能够输出稳定的时钟。当我们要改变pll的输出频率fout时,只需改变分频器对应的系数。

8.但是对于带有后分频器的pll,如图2所示,其后分频器(postscaler dividers,pstdiv将对fosc进行分频调整,分频调整系数可以是整数或小数,最终时钟输出fout可以由式2来表示,其中,n(lpdiv)为lpdiv的分频系数,n(pstdiv)为pstdiv的分频系数:

9.fout=[n(lpdiv)/n(pstdiv)]

·

fin

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

式2

[0010]

众所周知,描述二阶锁相环的方程是一个二阶非线性微分方程,二阶锁相环系统中压控振荡器vco可以看成是一个理想的积分器。所以从系统的角度来看,如果低通滤波器lpf是一阶的,则锁相环pll可以看成一个二阶系统。对一个二阶系统而言,存在固有频率ωn、阻尼系数ξ,如果突然改变系统内部的参数,系统都将根据其特性发生一次本征的阻尼振

荡。在同样的lpf条件下,vco灵敏度越高,ξ越小,锁定很快,但是阻尼振荡的幅度就愈大;ξ越大,阻尼振荡的幅度就愈小,大于1时就没有阻尼振荡,但是锁定时间变得很长。由于阻尼因子无法准确控制,而通常pll需要尽快锁定,因此输出存在一定幅度的阻尼振荡。

[0011]

当系统改变分频比后,pll需要重新锁定,锁定行为需要一定时间。锁定时间受环路带宽、锁定开始和结束的频率、阻尼因子等影响。如果选择一般pll,在锁定范围内的其二阶响应特性用阻尼因子表征。较快的锁定,阻尼因子小,出现较大的过冲;即使选取普通的阻尼因子0.45到0.7,也还是存在一定程度的过冲。

[0012]

如图3所示,在一个pll时钟系统变化特性中,其输入参考频率是12.5兆赫兹(mhz),分频器系数从31变为60时,输出频率应该从387.5mhz(12.5

×

31)变为750mhz(12.5

×

60)。图3中能明显看到二阶阻尼振荡特性,并且由于振荡出现的过冲,期间存在780mhz的输出频率,比750mhz的目标值要大。

[0013]

在片上系统soc(system on chip)中,为了低功耗,普遍采用动态自适应电压调整技术davs(dynamic adaptive voltage scaling)。在一定范围内,电压越高,中央处理器(central processing unit,cpu)能跑的最高频率越高,计算处理能力越高,功耗也更高。不同任务对cpu的计算能力的需求是不同的,一个简单的控制类任务仅需要很低的频率,而一个复杂的视频编解码算法却需要很高的频率,根据任务类别不断调整频率并且调低电压,能够大幅降低功耗。假如cpu工作电压在1伏(v)下,最高工作频率仅为770mhz,则pll的过冲频率780mh就会导致系统出错,为了不让系统崩溃,就要求调高电压。在留有安全裕度的情况下,要将电压调整到能让系统工作到更高频率的压值,例如1.05v,800mhz,但这样的处理方式会导致功耗的增加。

[0014]

若能够防止锁相环时钟过冲,则能避免上述系统出错的问题,或者减小功耗。理论上和实际中,常规的过冲不会非常大,例如10%-20%,因此若系统提供足够安全裕度,是不会带来太大问题的。

[0015]

但是,在不少实际设计中,在传统pll输出级联一个后分频器pstdiv可以让时钟范围更为广泛,或者是让压控振荡器vco的工作范围变小很多,这样可以降低设计难度,也可以提高可靠性。虽然后分频器本质上不属于pll,但是由于其影响较大,通常也将它作为锁相环的一部分来对待。但是后分频器有个非常明显的特征:由于它不在环路内,不具有二阶系统的环路带宽特性,相对输出fout是冲击式的瞬间响应,因此直接影响输出,在很多情况下将带来严重过冲问题。

[0016]

如图4所示,系统要求时钟从375mhz提高到387.5mhz,仅需提高12.5mhz,但却由于后分频器系数的变化引起了严重的过冲。切换前环路分频系数为60,后分频系数为2,因此,fosc振荡频率为750mhz,fout输出频率为375mhz。其中,切换是通过改变系数实现的,环路分频系数变为31,后分频系数变为1。

[0017]

从图4可以看到,系统经过长时间的巨大过冲后才稳定到387.5mhz。过冲的原因是fosc的频率只能通过环路来逐渐改变,环路滤波器有固定的带宽,vc控制的振荡器需要逐渐从750mhz变为387.5mhz,而后分频系数却能够瞬间从2变为1,这导致fout直接从当前的375mhz变为750mhz。若后级cpu无法运行在如此高频率,例如最多只能工作在500mhz频率,则将直接导致死机。假如cpu在1v下,最高工作频率仅为500mhz,那么pll切换输出导致的过冲频率750mh就必然使系统出错。为了不让系统崩溃,就要求大幅度调高电压。但是在很多

情况下,即使调高电压,cpu运行速度也无法一直提高,例如无法变快100%。在这种情况下,是无法通过大幅度提高功耗来避免问题的,必须通过增加额外硬件来解决,为了让系统不出错,就必须要防止过冲。

[0018]

现有技术中系统在要调高pll时钟频率之前,将cpu需要的时钟提前切换到一个固定的较低频率,例如另设一个32.768k或者12m的低频振荡器,然后让软件等待一个较为安全的规定时间,目的是让pll有足够的时间来稳定输出。系统等时钟稳定后,再将cpu需要的时钟切回pll已经达成的目标频率。

[0019]

这种防止锁相环时钟过冲的方式从时间方面考虑,pll频率切换所需要的时间不是一个恒定值,例如从50m到60m所需的时间与从50m到700m所需时间是完全不同。即使是同样的切换要求,如起始和终止频率一致,芯片在工作电源电压、环境温度和制造工艺存在偏差的情况下也是不同的,因此软件只能根据系统测试数据,假设一个足够安全的最长时间。从成本方面考虑,软件若要运行在另外一个安全时钟下,需要一个额外的硬件时钟资源。由于电压不一样安全时钟也不一样,在无法确定安全时钟最低值的情况下,就只能统一选取保守的较低时钟。

[0020]

综上所述,现有技术中为防止锁相环时钟异常所采取的方式,切换时间长,软件运行效能差。

技术实现要素:

[0021]

本发明实施例提供一种锁相环控制电路及锁相控制方法,用以防止锁相环模块输出的时钟异常,提高运行效能,节省功耗。

[0022]

第一方面,本发明实施例提供一种锁相环控制电路,包括:锁相环模块、切换模块和锁定检测模块,锁相环模块包括依次连接的鉴相器、低通滤波器、压控振荡器、以及环路分频器,压控振荡器包括第一振荡器和第二振荡器,环路分频器用于将压控振荡器中与低通滤波器连接的振荡器的输出信号反馈至鉴相器,其中,

[0023]

锁定检测模块,与切换模块、压控振荡器和环路分频器分别连接,用于检测压控振荡器的锁定状态,并根据锁定状态调节压控振荡器的状态,以及根据锁定状态向切换模块发送选择信号,其中,锁定状态包括第一振荡器的锁定状态和第二振荡器的锁定状态;

[0024]

切换模块,与压控振荡器连接,用于根据锁定检测模块输出的选择信号,在第一振荡器的输出信号和第二振荡器的输出信号中选择信号输出。

[0025]

本发明实施例提供的锁相环控制电路,包括:锁相环模块、切换模块和锁定检测模块,锁相环模块包括依次连接的鉴相器、低通滤波器、压控振荡器、以及环路分频器,其中,压控振荡器中设置有第一振荡器和第二振荡器压控振荡器,锁定检测模块用于检测压控振荡器的锁定状态,并根据锁定状态调节压控振荡器的状态,以及根据锁定状态向切换模块发送选择信号,锁定状态包括第一振荡器的锁定状态和第二振荡器的锁定状态,切换模块用于根据锁定检测模块输出的选择信号,在第一振荡器的输出信号和第二振荡器的输出信号中选择信号输出。相比于现有技术,由于切换模块的切换时间点就是锁相环模块的锁定时间点,因此,每次切换时间都是自适应的、且最短的时间,系统无需冗余的长时间统一等待;并且在切换期间,还能向系统提供原来相同频率的安全时钟,发挥cpu处理能力,从而防止锁相环模块输出的时钟异常,提高运行效能,节省功耗。

[0026]

在一种可能的实施方式中,锁定检测模块根据锁定状态调节压控振荡器的状态,具体用于:

[0027]

在检测到压控振荡器的锁定状态变化为失锁时,控制断开目标振荡器与低通滤波器的连接,连接非目标振荡器与低通滤波器,并控制目标振荡器保持当前振荡频率,目标振荡器为压控振荡器的锁定状态为锁定时处于工作状态的振荡器,非目标振荡器为压控振荡器中除目标振荡器之外的另一振荡器。

[0028]

本发明实施例提供的锁相环控制电路,在调节锁相环模块的输出信号时,控制断开目标振荡器与低通滤波器的连接,连接非目标振荡器与低通滤波器,即将目标振荡器从锁相环模块中脱离,将非目标振荡器接入锁相环模块,锁定检测模块还用于控制目标振荡器输出的时钟维持在原来的稳定频率,使锁定期间的阻尼振荡时钟不输出,当内部阻尼振荡时钟稳定后再切换为新的时钟,防止了锁相环模块输出的时钟异常,例如过冲。

[0029]

在一种可能的实施方式中,锁定检测模块根据锁定状态向切换模块发送选择信号,具体用于:

[0030]

检测环路分频器反馈的输出信号的频率与鉴相器的输入信号的频率是否达到锁定特征条件,根据检测结果向切换模块发送选择信号。

[0031]

在一种可能的实施方式中,锁定检测模块具体用于:

[0032]

在根据检测结果确定鉴相器的输入信号与环路分频器反馈的输出信号未达到锁定特征条件时,向切换模块发送用于指示选择目标振荡器的输出信号作为输出的选择信号;以及

[0033]

在根据检测结果确定鉴相器的输入信号与环路分频器反馈的输出信号达到锁定特征条件时,向切换模块发送用于指示选择非目标振荡器的输出信号作为输出的选择信号。

[0034]

在一种可能的实施方式中,锁定检测模块检测压控振荡器的锁定状态,具体用于:

[0035]

若检测到环路分频器反馈的输出信号的相位与鉴相器的输入信号的相位之差大于预设阈值,则确定检测到压控振荡器的锁定状态变化为失锁;以及

[0036]

若检测到环路分频器反馈的输出信号的相位与鉴相器的输入信号的相位之差小于或等于预设阈值,则确定检测到压控振荡器的锁定状态变化为锁定。

[0037]

在一种可能的实施方式中,锁相环控制电路还包括:

[0038]

锁相环模块还包括:与压控振荡器相连接的后分频器,后分频器包括第一分频器和第二分频器,第一分频器与第一振荡器连接,第二分频器与第二振荡器连接;

[0039]

电路还包括:控制检测模块,分别与锁定检测模块、锁相环模块连接,用于接收锁相环模块中的分频器的控制信号,并在控制信号发生变化时,向锁定检测模块发送失锁检测信号;

[0040]

切换模块,与后分频器连接,具体用于:根据锁定检测模块输出的选择信号,在第一振荡器的输出信号和第二振荡器的输出信号中选择输出信号。

[0041]

本发明实施例提供的锁相环控制电路,锁相环模块还可以包括后分频器,当锁相环控制电路中包含后分频器时,电路还包括控制检测模块。当改变后分频器的系数时,控制检测模块检测到变化,瞬间复位锁定检测模块,从而立刻启动安全输出控制机制,以避免由于后分频器分频系数变化引起的意外过冲。

[0042]

在一种可能的实施方式中,控制检测模块包括依次连接的第一延时单元、同或门运算器,其中,

[0043]

第一延时单元,用于根据控制信号的变化调节延时单元大小生成延时信号,并将延时信号输入同或门运算器;

[0044]

同或门运算器,根据延时信号生成失锁检测信号并传输至锁定检测模块。

[0045]

在一种可能的实施方式中,锁定检测模块包括:

[0046]

第二延时单元,用于对鉴相器的输入信号进行延时,并将延时后的鉴相器的输入信号发送至第一触发器;

[0047]

第三延时单元,用于对环路分频器反馈的输出信号进行延时,并将延时后的环路分频器反馈的输出信号发送至第二触发器;

[0048]

第一触发器,用于比较环路分频器反馈的输出信号和延时后的鉴相器的输入信号,并根据比较结果生成第一比较信号;

[0049]

第二触发器,用于比较鉴相器的输入信号和延时后的环路分频器反馈的输出信号,并根据比较结果生成第二比较信号;

[0050]

与运算器,用于对第一比较信号和第二比较信号进行逻辑与运算,生成选择信号。

[0051]

第二方面,本发明实施例提供一种电子设备,包括本发明实施例第一方面提供的锁相环控制电路。

[0052]

第三方面,本发明实施例提供一种锁相控制方法,应用于本发明实施例第一方面提供的锁相环控制电路,包括:

[0053]

检测锁相环控制电路中压控振荡器的锁定状态,并根据锁定状态调节压控振荡器中的状态,其中,锁定状态包括第一振荡器的锁定状态和第二振荡器锁定状态;

[0054]

根据锁定状态生成选择信号,选择信号用于在第一振荡器的输出信号和第二振荡器的输出信号中选择信号输出。

[0055]

在一种可能的实施方式中,根据锁定状态调节压控振荡器中的状态,包括:

[0056]

在检测到压控振荡器的锁定状态变化为失锁时,断开目标振荡器与低通滤波器的连接,连接非目标振荡器与低通滤波器,并控制目标振荡器保持当前振荡频率,目标振荡器为压控振荡器的锁定状态为锁定时处于工作状态的振荡器,非目标振荡器为压控振荡器中除目标振荡器之外的另一振荡器。

[0057]

在一种可能的实施方式中,根据锁定状态生成选择信号,包括:

[0058]

检测环路分频器反馈的输出信号的频率与鉴相器的输入信号的频率是否达到锁定特征条件,根据检测结果生成选择信号。

[0059]

在一种可能的实施方式中,根据检测结果生成选择信号,包括:

[0060]

在根据检测结果确定环路分频器反馈的输出信号的频率与鉴相器的输入信号的频率未达到锁定特征条件时,生成用于指示选择目标振荡器的输出信号作为输出的选择信号;以及

[0061]

在根据检测结果确定环路分频器反馈的输出信号的频率与鉴相器的输入信号的频率达到锁定特征条件时,生成用于指示选择非目标振荡器的输出信号作为输出的选择信号。

[0062]

第四方面,本发明实施例提供一种锁相控制装置,应用于本发明实施例第一方面

提供的锁相环控制电路,包括:

[0063]

检测模块,检测锁相环控制电路中压控振荡器的锁定状态,并根据锁定状态调节压控振荡器中的状态,其中,锁定状态包括第一振荡器的锁定状态和第二振荡器锁定状态;

[0064]

选择模块,用于根据锁定状态生成选择信号,选择信号用于在第一振荡器的输出信号和第二振荡器的输出信号中选择信号输出。

[0065]

在一种可能的实施方式中,检测模块具体用于:

[0066]

在检测到压控振荡器的锁定状态变化为失锁时,断开目标振荡器与低通滤波器的连接,连接非目标振荡器与低通滤波器,并控制目标振荡器保持当前振荡频率,目标振荡器为压控振荡器的锁定状态为锁定时处于工作状态的振荡器,非目标振荡器为压控振荡器中除目标振荡器之外的另一振荡器。

[0067]

在一种可能的实施方式中,选择模块具体用于:

[0068]

检测环路分频器反馈的输出信号的频率与鉴相器的输入信号的频率是否达到锁定特征条件,根据检测结果生成选择信号。

[0069]

在一种可能的实施方式中,选择模块具体用于:

[0070]

在根据检测模块的检测结果确定输入鉴相器的输入信号与环路分频器反馈的输出信号未达到锁定特征条件时,生成用于指示选择目标振荡器的输出信号作为输出的选择信号;以及

[0071]

在根据检测模块的检测结果确定检测鉴相器的输入信号与环路分频器反馈的输出信号达到锁定特征条件时,生成用于指示选择非目标振荡器的输出信号作为输出的选择信号。

附图说明

[0072]

通过参考附图阅读下文的详细描述,本发明示例性实施方式的上述以及其他目的、特征和优点将变得易于理解。在附图中,以示例性而非限制性的方式示出了本发明的若干实施方式,其中:

[0073]

图1为现有技术中一种锁相环的电路原理图;

[0074]

图2为现有技术中另一锁相环的电路原理图;

[0075]

图3为现有技术中一种锁相环时钟系统变化特性的示意图;

[0076]

图4为现有技术中另一锁相环时钟系统变化特性的示意图;

[0077]

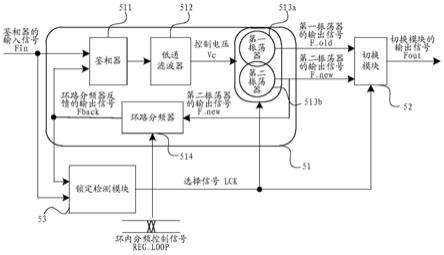

图5为本发明实施例提供的一种锁相环控制电路原理图;

[0078]

图6为本发明实施例提供的一种锁相环控制电路的时钟变化特性示意图;

[0079]

图7为本发明实施例提供的锁定检测模块的结构示意图;

[0080]

图8为本发明实施例提供的另一锁相环控制电路原理图;

[0081]

图9为本发明实施例提供的另一锁相环控制电路的时钟变化特性示意图;

[0082]

图10为本发明实施例提供的控制检测模块的结构示意图;

[0083]

图11为本发明实施例提供的切换模块的结构示意图;

[0084]

图12为本发明实施例提供的一种锁相环控制方法的示意流程图;

[0085]

图13为本发明实施例提供的一种锁相环控制装置的结构示意图。

具体实施方式

[0086]

以下结合附图对本发明的实施例进行说明,应当理解,此处所描述的实施例仅用于说明和解释本发明,并不用于限定本发明。

[0087]

鉴于现有技术中防止锁相环时钟异常所采取的方式,切换时间长,软件运行效能差,本发明实施例提供一种锁相环控制电路及其锁相控制方案,用以防止锁相环模块输出的时钟异常,提高运行效能,节省功耗。

[0088]

下面结合附图对本发明实施例提供的电路进行详细说明。

[0089]

如图5所示,本发明实施例提供一种锁相环控制电路,包括:

[0090]

锁相环模块51、切换模块52和锁定检测模块53,锁相环模块包括依次连接的鉴相器511、低通滤波器512、压控振荡器513、以及环路分频器514,压控振荡器513包括第一振荡器513a和第二振荡器513b,环路分频器514用于将压控振荡器513中与低通滤波器512连接的振荡器的输出信号反馈至鉴相器511。

[0091]

锁定检测模块53,与切换模块52、压控振荡器513和环路分频器514分别连接,用于检测压控振荡器513的锁定状态,并根据锁定状态调节压控振荡器513的状态,以及根据锁定状态向切换模块52发送选择信号,其中,锁定状态包括第一振荡器513a的锁定状态和第二振荡器513b的锁定状态。

[0092]

切换模块52,与压控振荡器513连接,用于根据锁定检测模块53输出的选择信号,在第一振荡器513a的输出信号和第二振荡器513b的输出信号中选择信号输出。

[0093]

其中,锁定检测模块53具体用于,在检测到压控振荡器513的锁定状态变化为失锁时,控制断开目标振荡器与低通滤波器512的连接,连接非目标振荡器与低通滤波器512,并控制目标振荡器保持当前振荡频率,目标振荡器为压控振荡器的锁定状态为锁定时处于工作状态的振荡器,非目标振荡器为压控振荡器中除目标振荡器之外的另一振荡器。

[0094]

具体实施时,锁定检测模块在调节锁相环模块的输出信号时,控制断开目标振荡器与低通滤波器的连接,连接非目标振荡器与低通滤波器,即将目标振荡器从锁相环模块中脱离,将非目标振荡器接入锁相环模块,锁定检测模块还用于控制目标振荡器输出的时钟维持在原来的稳定频率,使锁定期间的阻尼振荡时钟不输出,当内部阻尼振荡时钟稳定后再切换为新的时钟,防止了锁相环模块输出的时钟异常,例如过冲。

[0095]

具体实施时,锁定检测模块53根据锁定状态向切换模块52发送选择信号,具体用于:

[0096]

检测环路分频器514反馈的输出信号的频率与鉴相器511的输入信号的频率是否达到锁定特征条件,根据检测结果向切换模块52发送选择信号。

[0097]

具体实施时,锁定检测模块53具体用于:

[0098]

在根据检测结果确定鉴相器511的输入信号与环路分频器514反馈的输出信号未达到锁定特征条件时,向切换模块52发送用于指示选择目标振荡器的输出信号作为输出的选择信号;以及

[0099]

在根据检测结果确定鉴相器511的输入信号与环路分频器514反馈的输出信号达到锁定特征条件时,向切换模块52发送用于指示选择非目标振荡器的输出信号作为输出的选择信号。

[0100]

具体实施时,锁定检测模块53检测压控振荡器513的锁定状态,具体用于:若检测

到环路分频器514反馈的输出信号的相位与鉴相器511的输入信号的相位之差大于预设阈值,则确定检测到压控振荡器513的锁定状态变化为失锁;以及若检测到环路分频器514反馈的输出信号的相位与鉴相器511的输入信号的相位之差小于或等于预设阈值,则确定检测到压控振荡器513的锁定状态变化为锁定,其中,预设阈值可以根据实际经验设定,本发明实施例对此不做限定,例如,预设阈值为5度。

[0101]

如图6所示,为本发明实施例提供的锁相环控制电路的仿真结果,可以看到锁定期间是完全没有过冲的。150微秒(μs)时刻系统发出调整时钟的指令后,锁相环模块的输出信号的频率依然维持在原来大约387.5mhz附近,此时第一振荡器从锁相环模块中脱离,变成开环振荡,但由于第一振荡器的输入控制端口变成高阻状态,因此输出时钟由于寄生效应产生一点点偏差;168μs时刻锁相环模块已经重新锁定,切换模块的输出信号立刻切换为750mhz的精准目标值,即第二振荡器的锁定值。但实际上锁相环模块中的第二振荡器时钟表现特性依然和原来一样,依然存在780mhz的时钟过冲,只不过没有被切换模块输出而已。

[0102]

如图7所示,锁定检测模块包括:

[0103]

第二延时单元71,用于对鉴相器的输入信号进行延时,并将延时后的鉴相器的输入信号发送至第一触发器;

[0104]

第三延时单元72,用于对环路分频器反馈的输出信号进行延时,并将延时后的环路分频器反馈的输出信号发送至第二触发器;

[0105]

第一触发器73,用于比较环路分频器反馈的输出信号和延时后的鉴相器的输入信号,并根据比较结果生成第一比较信号;

[0106]

第二触发器74,用于比较鉴相器的输入信号和延时后的环路分频器反馈的输出信号,并根据比较结果生成第二比较信号;

[0107]

与运算器75,用于对第一比较信号和第二比较信号进行逻辑与运算,生成选择信号。

[0108]

具体实施时,锁定检测模块可以采用图7中交叉延时锁存的结构来实现。假设锁相环模块在锁定期间鉴相器的输入信号fin和环路分频器反馈的输出信号fback的上升沿是对齐的,即相位差恒定,延迟任何一方的上升沿都能抓取到另一方的高电平,两个触发器的输出始终都是1。当环路分频器改变时,其输出信号fback就会发生变化,新的上升沿会与鉴相器的输入信号fin相差一个或n个振荡周期。当pll要调高输出频率时,要增大环路分频器的分频系数。例如从n变为n+k,则环路分频器反馈的输出信号fback将比鉴相器的输入信号fin延迟k个周期。

[0109]

具体实施时,若检测到环路分频器反馈的输出信号的相位与鉴相器的输入信号的相位之差大于预设阈值,则确定检测到压控振荡器的锁定状态变化为失锁,例如,使鉴相器的输入信号fin和环路分频器反馈的输出信号fback的上升沿相差在一个振荡周期内,第一触发器的输出将输出0,发出选择信号lck。第二振荡器的输出信号在锁相环模块的作用下逐渐加快直到发生过冲,这时候环路分频器反馈的输出信号fback边沿将会领先鉴相器的输入信号fin的边沿,第二触发器又将输出0。若检测到环路分频器反馈的输出信号的相位与鉴相器的输入信号的相位之差小于或等于预设阈值,则确定检测到压控振荡器的锁定状态变化为锁定,即当鉴相器的输入信号fin和环路分频器反馈的输出信号fback的边沿重新对齐到一定范围内时,锁定检测模块输出的选择信号变回1。

[0110]

如图8所示,本发明实施例提供另一锁相环控制电路,包括:

[0111]

锁相环模块81、切换模块82、锁定检测模块83和控制检测模块84,锁相环模块包括依次连接的鉴相器811、低通滤波器812、压控振荡器813、环路分频器814以及与压控振荡器相连接的后分频器815。其中,压控振荡器813包括第一振荡器813a和第二振荡器813b,环路分频器814用于将压控振荡器813中与低通滤波器812连接的振荡器的输出信号反馈至鉴相器811;后分频器815包括第一分频器815a和第二分频器815b,第一分频器815a与第一振荡器813a连接,第二分频器815b与第二振荡器813b连接。

[0112]

锁定检测模块83,与切换模块82、压控振荡器813和环路分频器814分别连接,用于检测压控振荡器813的锁定状态,并根据锁定状态调节压控振荡器813的状态,以及根据锁定状态向切换模块82发送选择信号,其中,锁定状态包括第一振荡器813a的锁定状态和第二振荡器813b的锁定状态。

[0113]

控制检测模块84,分别与锁定检测模块83、锁相环模块81连接,用于接收锁相环模块81中的分频器的控制信号,并在控制信号发生变化时,向锁定检测模块83发送失锁检测信号。

[0114]

需要说明的是,控制检测模块接收的控制信号,可以包括控制环路分频器的环内分频控制信号和控制后分频器的环外分频控制信号,也可以只包括控制后分频器的环外分频控制信号。

[0115]

切换模块82,与后分频器815连接,具体用于根据锁定检测模块83输出的选择信号,在第一振荡器的输出信号和第二振荡器的输出信号中选择输出信号。

[0116]

如图9所示,为本发明实施例提供的另一锁相环控制电路的仿真结果,可以看到锁定期间也是完全没有过冲的。129.4μs时刻系统发出调整时钟的指令后,环路分频系数从60变为31,后分频系数从2变为1,锁相环模块的输出信号的频率依然维持在原来大约387mhz附近,此时第一振荡器从锁相环模块中脱离,变成开环振荡,但由于第一振荡器的输入控制端口变成高阻状态,因此输出时钟由于寄生效应产生一点点偏差;144μs时刻锁相环模块已经重新锁定,切换模块的输出信号立刻切换为387.5mhz的精准目标值,即第二振荡器的锁定值。但实际上锁相环模块中的第二振荡器时钟表现特性依然和原来一样,依然存在750mhz的时钟过冲,只不过没有被切换模块输出而已。

[0117]

含有后分频器的锁相环模块需要调高时钟时,除了单独增大环路分频系数的方式外,还存在其它的系数调整方式,当环路分频系数变小时,后分频器系数也变小。例如要将时钟从375mhz调高12.5mhz时,其环路分频系数是变小的,即从60变为31,其后分频系数也变小,即从2变为1。系数调整后,第一次分频结果导致环路分频器反馈的输出信号fback将比鉴相器的输入信号fin提前29个周期。只要将图7中第三延时单元的延时周期设计在合理范围,第二触发器输出将输出0,发出选择信号lck。第二分频器的输出信号在锁相环模块的作用下逐渐降低。直到鉴相器的输入信号fin和环路分频器反馈的输出信号fback的边沿重新对齐到一定范围内时,锁定检测模块输出的选择信号变回1。

[0118]

如图10所示,控制检测模块包括:

[0119]

第一延时单元101,用于根据控制信号的变化调节延时单元大小生成延时信号,并将延时信号输入同或门运算器;

[0120]

同或门运算器102,根据延时信号生成失锁检测信号并传输至锁定检测模块。

[0121]

具体实施时,控制检测模块接收的控制信号,可以包括控制环路分频器的环内分频控制信号和控制后分频器的环外分频控制信号,也可以只包括控制后分频器的环外分频控制信号。因为控制环路分频器的环内分频控制信号即使不进入控制检测模块,通过影响环路分频器反馈的输出信号fback的边沿也可以被锁定检测模块探测到。但若控制后分频器的环外分频控制信号有变化,则需要立刻发出失锁检测信号给锁定检测模块,通过锁定检测模块输出的选择信号lck启动切换模块和压控振荡器及其后分频器的在线选择方式。控制检测模块发出的失锁检测信号可以为单个脉冲信号,也可以是更为复杂的多个时序控制信号,图10为第一延时单元、同或/异或非逻辑实现的电路,当环内分频控制信号和/或环外分频控制信号发生变化时,就会产生一个时间宽度为延时单元大小的负脉冲。

[0122]

具体实施时,切换模块可以采用比较简单方式,例如多路选择器,但是可能在切换过程中出现误差;也可以采用如图11所示的互交叉反馈双锁存输出结构,相对多路选择器更为安全。互交叉反馈双锁存输出结构可以对两个异步时钟进行安全切换,不会有意外窄脉冲。当然,也可以用其他类似的完成类似功能,本发明对此不做限定。

[0123]

本发明实施例还提供一种电子设备,包括本发明实施例提供的锁相环控制电路。

[0124]

基于上述相同的发明构思,本发明实施例还提供一种锁相控制方法,应用于本发明实施例提供的锁相环控制电路,如图12所示,其可以包括以下步骤:

[0125]

步骤121,检测锁相环控制电路中压控振荡器的锁定状态,并根据锁定状态调节压控振荡器中的状态,其中,锁定状态包括第一振荡器的锁定状态和第二振荡器锁定状态。

[0126]

步骤122,根据锁定状态生成选择信号,选择信号用于在第一振荡器的输出信号和第二振荡器的输出信号中选择信号输出。

[0127]

在一种可能的实施方式中,根据锁定状态调节压控振荡器中的状态,包括:

[0128]

在检测到压控振荡器的锁定状态变化为失锁时,断开目标振荡器与低通滤波器的连接,连接非目标振荡器与低通滤波器,并控制目标振荡器保持当前振荡频率,目标振荡器为压控振荡器的锁定状态为锁定时处于工作状态的振荡器,非目标振荡器为压控振荡器中除目标振荡器之外的另一振荡器。

[0129]

在一种可能的实施方式中,根据锁定状态生成选择信号,包括:

[0130]

检测环路分频器反馈的输出信号的频率与鉴相器的输入信号的频率是否达到锁定特征条件,根据检测结果生成选择信号。

[0131]

在一种可能的实施方式中,根据检测结果生成选择信号,包括:

[0132]

在根据检测结果确定环路分频器反馈的输出信号的频率与鉴相器的输入信号的频率未达到锁定特征条件时,生成用于指示选择目标振荡器的输出信号作为输出的选择信号;以及

[0133]

在根据检测结果确定环路分频器反馈的输出信号的频率与鉴相器的输入信号的频率达到锁定特征条件时,生成用于指示选择非目标振荡器的输出信号作为输出的选择信号。

[0134]

基于上述相同的发明构思,本发明实施例还提供一种锁相控制装置。

[0135]

如图13所示,本发明实施例还提供一种锁相控制装置,应用于本发明实施例提供的锁相环控制电路,包括:

[0136]

检测模块131,检测锁相环控制电路中压控振荡器的锁定状态,并根据锁定状态调

节压控振荡器中的状态,其中,锁定状态包括第一振荡器的锁定状态和第二振荡器锁定状态;

[0137]

选择模块132,用于根据锁定状态生成选择信号,选择信号用于在第一振荡器的输出信号和第二振荡器的输出信号中选择信号输出。

[0138]

在一种可能的实施方式中,检测模块131具体用于:

[0139]

在检测到压控振荡器的锁定状态变化为失锁时,断开目标振荡器与低通滤波器的连接,连接非目标振荡器与低通滤波器,并控制目标振荡器保持当前振荡频率,目标振荡器为压控振荡器的锁定状态为锁定时处于工作状态的振荡器,非目标振荡器为压控振荡器中除目标振荡器之外的另一振荡器。

[0140]

在一种可能的实施方式中,选择模块132具体用于:

[0141]

检测环路分频器反馈的输出信号的频率与鉴相器的输入信号的频率是否达到锁定特征条件,根据检测结果生成选择信号。

[0142]

在一种可能的实施方式中,选择模块132具体用于:

[0143]

在根据检测模块131的检测结果确定输入鉴相器的输入信号与环路分频器反馈的输出信号未达到锁定特征条件时,生成用于指示选择目标振荡器的输出信号作为输出的选择信号;以及

[0144]

在根据检测模块132的检测结果确定检测鉴相器的输入信号与环路分频器反馈的输出信号达到锁定特征条件时,生成用于指示选择目标振荡器的输出信号作为输出的选择信号。

[0145]

本领域技术人员在考虑说明书及实践这里公开的发明后,将容易想到本公开的其它实施方案。本公开旨在涵盖本公开的任何变型、用途或者适应性变化,这些变型、用途或者适应性变化遵循本公开的一般性原理并包括本公开未公开的本技术领域中的公知常识或惯用技术手段。说明书和实施例仅被视为示例性的,本公开的真正范围和精神由下面的权利要求指出。

[0146]

应当理解的是,本公开并不局限于上面已经描述并在附图中示出的精确结构,并且可以在不脱离其范围进行各种修改和改变。本公开的范围仅由所附的权利要求来限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1