可变增益放大器及其方法与流程

1.本公开的实施例主要是有关于增加在低电压操作的可变增益放大器的增益范围的可变增益放大器技术。

背景技术:

2.可变增益放大器可将欲接收或传送的射频信号放大或缩小至所需要功率水平,以传给后级电路做信号处理。可变增益放大器的使用范围很广,例如遥控玩具、消费性移动通信电子装置、基站、军事应用、太空应用等。

3.在现今的电子装置中,为了省电和延长电池的使用时间,都会使用较低的电源供应电压。然而,随着供应电压变小,可变增益放大器的可变增益范围也会跟着变小,因而限制了可变增益放大器的作用。因此,在不提高电源供应电压的条件控制下,如何使得可变增益放大器在低电压操作时,也能维持足够的可变增益范围,将是值得思考的课题。

技术实现要素:

4.有鉴于上述背景技术的问题,本公开的实施例提供了一种可变增益放大器和增加可变增益范围的方法。

5.根据本公开的一实施例提供了一种可变增益放大器。上述可变增益放大器包括至少一放大器电路、至少一电流汲取电路,以及至少一基底偏压电路。每一上述电流汲取电路分别耦接每一上述放大器电路。每一上述基底偏压电路分别耦接每一上述电流汲取电路,以提供一正偏压给每一上述电流汲取电路。

6.根据本公开的一实施例提供了一种增加可变增益范围的方法。上述增加可变增益范围的方法的步骤包括,配置至少一基底偏压电路在上述可变增益放大器中,其中每一上述基底偏压电路会分别耦接至上述可变增益放大器的每一电流汲取电路;以及从每一基底偏压电路提供一正偏压给其对应的电流汲取电路。

7.关于本公开其他附加的特征与特点,本领域的技术人员,在不脱离本公开的精神和范围内,当可根据本案实施方法中所公开的可变增益放大器及其方法,做些许的改动与润饰而得到。

附图说明

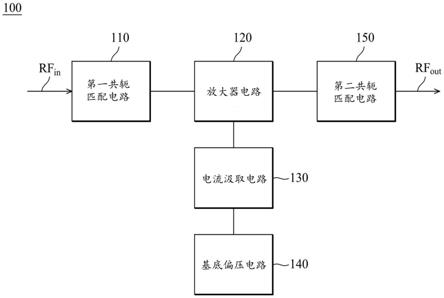

8.图1是显示根据本公开的一实施例所述的一可变增益放大器100的方块图。

9.图2a是显示根据本公开的一实施例所述的一可变增益放大器200的电路图。

10.图2b是显示根据本公开的另一实施例所述的一可变增益放大器200的电路图。

11.图3是根据本公开的一实施例所述的增加可变增益范围的方法的流程图300。

具体实施方式

12.本章节所叙述的是实施本公开的较佳方式,目的在于说明本公开的精神而非用以

限定本公开的保护范围,本公开的保护范围当视后附的权利要求书所界定者为准。

13.图1是显示根据本公开的一实施例所述的一可变增益放大器100的方块图。如图1所示,可变增益放大器100可包含一第一共轭匹配电路110、一放大器电路120、一电流汲取(current steering)电路130、一基底偏压电路140,以及一第二共轭匹配电路150。注意的是,在图1中所示的方块图,仅是为了方便说明本公开的实施例,但本公开并不以图1为限。可变增益放大器100中也可包含其他共轭匹配电路、放大器电路、电流汲取电路、基底偏压电路。

14.在本公开的实施例中,第一共轭匹配电路110耦接至放大器电路120。第一共轭匹配电路110可用以接收射频输入信号rf

in

,并对射频输入信号rf

in

进行共轭匹配。射频输入信号rf

in

进行共轭匹配后,第一共轭匹配电路110可将已进行共轭匹配的射频输入信号rf

in

传送给放大器电路120。

15.在本公开的实施例中,放大器电路120可用以放大已进行共轭匹配的射频输入信号rf

in

。此外,在本公开的实施例中,放大器电路120可以是一级联式(cascode)放大器电路,例如:图2a-2b的第一放大器电路220和第二放大器电路260。

16.在本公开的实施例中,电流汲取电路130耦接至放大器电路120。电流汲取电路130可用以控制放大器电路120所产生的增益。以下将会以图2a-2b来做说明。根据本发明一实施例,电流汲取电路130可以是一数字电路,以下将会以图2a来说明。根据本发明另一实施例,电流汲取电路130可以是一模拟电路,以下将会以图2b来说明。

17.在本公开的实施例中,基底偏压电路140耦接至电流汲取电路130。基底偏压电路140可提供一正偏压给电流汲取电路130,以增加电流汲取电路130的控制电压范围或增加电流汲取电路130的汲取电流。以下将会以图2a-2b来做说明。

18.在本公开的实施例中,第二共轭匹配电路150耦接至放大器电路120。第二共轭匹配电路150可用以对放大器电路120的输出信号进行共轭匹配,以输出射频输出信号rf

out

。在本公开另一些实施例中,第二共轭匹配电路150也会耦接下一级的放大器电路,并将进行共轭匹配后的放大器电路120的输出信号,输出给下一级的放大器电路。以下将会以图2a-2b来做说明。

19.图2a是显示根据本公开的一实施例所述的一可变增益放大器200的电路图。在此实施例中,如图2a所示,可变增益放大器200可包括一第一共轭匹配电路210(可对应第一共轭匹配电路110)、一第一放大器电路220(可对应放大器电路120)、一第一电流汲取电路230(可对应电流汲取电路130)、一第一基底偏压电路240(可对应基底偏压电路140)、一第二共轭匹配电路250(可对应第二共轭匹配电路150)、一第二放大器电路260、一第二电流汲取电路270、一第二基底偏压电路280以及一第三共轭匹配电路290。在此实施例中,电流汲取电路230和电流汲取电路270是以数字电路的方式来实现。此外,特别说明地是,图2a中显示了包含两级放大器电路的可变增益放大器的架构,但本公开不以此为限。图2a的实施例也可应用在包含一级放大器或更多级放大器的可变增益放大器的架构中。举例来说,若可变增益放大器200仅包含一级放大器,可变增益放大器200就仅会包括一第一共轭匹配电路210(可对应第一共轭匹配电路110)、第一放大器电路220(可对应放大器电路120)、第一电流汲取电路230(可对应电流汲取电路130)、第一基底偏压电路240(可对应基底偏压电路140)和第二共轭匹配电路250(可对应第二共轭匹配电路150)。

20.如图2a所示,第一共轭匹配电路210可包括传输线tl1~tl3、电容c1和c2以及电阻r1。传输线tl1的一端会接收射频输入信号rf

in

,另一端则会耦接至电容c1。传输线tl2的一端会耦接至电容c1和传输线tl3,另一端则会耦接至电阻r1和电容c2。传输线tl3的一端会耦接至电容c1和传输线tl2,另一端则会耦接至第一放大器电路220。电阻r1的一端会耦接至传输线tl2和电容c2,另一端则会耦接至电压源v

g

1。

21.如图2a所示,第一放大器电路220可包括第一晶体管m1、第二晶体管m2、电阻r2以及电容c3。第一晶体管m1的栅极会耦接至第一共轭匹配电路210的传输线tl3,以接收经过第一共轭匹配电路210共轭匹配处理后的射频输入信号rf

in

。第一晶体管m1的源极会耦接至一接地。第一晶体管m1的漏极会耦接至第二晶体管m2的源极。第二晶体管m2的栅极会耦接至电阻r2和电容c3,并从电阻r2接收电压源v

g

2。第二晶体管m2的源极会耦接至第一晶体管m1的漏极以及第一电流汲取电路230。第二晶体管m2的漏极会耦接至第二共轭匹配电路250。电容c3的一端会耦接至地,另一端则会耦接至第二晶体管m2的栅极与电阻r2。电容c3可当成稳压电容,以稳压第二晶体管m2的栅极电压。电阻r2的一端会耦接至电压源v

g

2,另一端则会耦接至第二晶体管m2的栅极与电容c3。电阻r2可当成保护装置,以避免太大电流损坏第二晶体管m2。

22.如图2a所示,第一电流汲取电路230可包括晶体管m31、m32、m33和m34,以及电容c4。晶体管m31、m32、m33和m34是三重井(triple-well)晶体管,且以并联方式连接。晶体管m31、m32、m33和m34的栅极分别会接收数字控制信号v

c

31、v

c

32、v

c

33和v

c

34。在数字控制信号v

c

31、v

c

32、v

c

33和v

c

34的控制下,晶体管m31、m32、m33和m34可从第二晶体管m2汲取电流,以控制第一放大器电路220的增益。晶体管m31、m32、m33和m34的源极会耦接至第一晶体管m1的漏极和第二晶体管m2的源极。晶体管m31、m32、m33和m34的漏极会耦接至电容c4和电压源v

dd

。晶体管m31、m32、m33和m34的基板本体端会接收第一基底偏压电路240所提供的一正偏压v

bs

。电容c4的一端耦接至地,另一端则耦接至晶体管m31、m32、m33和m34的漏极和电压源v

dd

。在本发明的实施中,每一基底偏压电路(例如:第一基底偏压电路240和第二基底偏压电路280)会分别耦接至每一电流汲取电路(例如:第一电流汲取电路230和第二电流汲取电路270)的三重井晶体管的一基板本体端。

23.以下将更进一步说明第一电流汲取电路230的操作。在此实施例中,数字控制信号v

c

31、v

c

32、v

c

33和v

c

34(可为0或1)可用以控制晶体管m31、m32、m33和m34是导通或是关闭。当通过数字控制信号v

c

31、v

c

32、v

c

33和v

c

34(可为0或1)控制晶体管m31、m32、m33和m34的一个或多个导通时,流经第二晶体管m2的电流会被抽到晶体管m31、m32、m33和m34,因而造成第二晶体管m2电流下降。当第二晶体管m2电流下降时,第二晶体管m2的转导值(gm2)将会降低。因此,在此实施例中,可透过数字控制信号v

c

31、v

c

32、v

c

33和v

c

34来调整流经第二晶体管m2的电流,进而达成控制第一放大器电路220的整体增益的目的。举例来说,若晶体管m31、m32、m33和m34中被导通者越多,第二晶体管m2的电流将会被抽取更多,因而使得第一放大器电路220的整体增益下降更多,反的亦然。

24.如图2a所示,第一基底偏压电路240可包括多个导线。多个导线会耦接至晶体管m31、m32、m33和m34的基板本体端,以从多个导线提供正偏压v

bs

至晶体管m31、m32、m33和m34的基板本体端。由于晶体管m31、m32、m33和m34是三重井(triple-well)晶体管,其基板本体端可以额外拉线出来接收电压(即第一基底偏压电路240提供的正偏压v

bs

)。此外,再参照以

下方程式可得知当v

bs

不为0且为正值时,临界电压v

th

的值会变小。因此,在此实施例中,当晶体管m31、m32、m33和m34的基板本体端接收到正偏压v

bs

后,晶体管m31、m32、m33和m34的临界电压v

th

会下降。当晶体管m31、m32、m33和m34的临界电压v

th

下降,晶体管m31、m32、m33和m34可从第二晶体管m2抽取更多的电流,因而使得可调整的可变增益范围将会增加。

25.如图2a所示,第二共轭匹配电路250可包括传输线tl4~tl10、电容c5~c8以及电阻r3。传输线tl4的一端会耦接至电压源v

dd

和电容c5,另一端则耦接至传输线tl5和电容c6。传输线tl5的一端会耦接至传输线tl4和电容c6,另一端则耦接至第二晶体管m2的漏极。传输线tl6的一端会耦接至电容c6,另一端则耦接至传输线tl7和传输线tl8。传输线tl7的一端会耦接至传输线tl6和地,另一端则耦接至传输线tl8。传输线tl8的一端会耦接至传输线tl6和传输线tl7,另一端则耦接至电容c7。传输线tl9的一端会耦接至电容c7和传输线tl10,另一端则耦接至电容c8和电阻r3。传输线tl10的一端会耦接至传输线tl9和电容c7和,另一端则耦接至第二放大器电路260。电阻r3的一端会耦接至电压源v

g

1,另一端则耦接至传输线tl9的和电容c8。电容c8一端耦接至电阻r3和传输线tl9,另一端则耦接至地。

26.如图2a所示,第二放大器电路260可包括第四晶体管m4、第五晶体管m5、电阻r4以及电容c9。第四晶体管m4的栅极会耦接至第二共轭匹配电路250的传输线tl10,以接收经过第二共轭匹配电路250的输入信号。第四晶体管m4的源极会耦接至一接地。第四晶体管m4的漏极会耦接至第五晶体管m5的源极。第五晶体管m5的栅极会耦接至电阻r4和电容c9,并从电阻r4接收电压源v

g

2。第五晶体管m5的源极会耦接至第四晶体管m4的漏极以及第二电流汲取电路270。第五晶体管m5的漏极会耦接至第三共轭匹配电路290。电容c9的一端会耦接至地,另一端则会耦接至第五晶体管m5的栅极与电阻r4。电容c9可当成稳压电容,以稳压第五晶体管m5的栅极电压。电阻r4的一端会耦接至电压源v

g

2,另一端则会耦接至第五晶体管m5的栅极与电容c9。电阻r4可当成保护装置,以避免太大电流损坏第五晶体管m5。

27.如图2a所示,第二电流汲取电路270可包括晶体管m71、m72、m73和m74,以及电容c10。晶体管m71、m72、m73和m74是三重井(triple-well)晶体管,且以并联方式连接。晶体管m71、m72、m73和m74的栅极分别会接收数字控制信号v

c

71、v

c

72、v

c

73和v

c

74。在数字控制信号v

c

71、v

c

72、v

c

73和v

c

74的控制下,晶体管m71、m72、m73和m74可从第五晶体管m5汲取电流,以控制第二放大器电路260的增益。晶体管m71、m72、m73和m74的源极会耦接至第四晶体管m4的漏极和第五晶体管m5的源极。晶体管m71、m72、m73和m74的漏极会耦接至电容c10和电压源v

dd

。晶体管m71、m72、m73和m74的基板本体端会接收第二基底偏压电路280提供的一正偏压v

bs

。电容c10的一端耦接至地,另一端耦接至晶体管m71、m72、m73和m74的漏极和电压源v

dd

。第二电流汲取电路270的操作类似第一电流汲取电路230。因此,在此就不再赘述。

28.如图2a所示,第二基底偏压电路280可包括多个导线。多个导线会耦接至晶体管m71、m72、m73和m74的基板本体端,以从多个导线提供正偏压v

bs

至晶体管m71、m72、m73和m74的基板本体端。由于晶体管m71、m72、m73和m74是三重井(triple-well)晶体管,其基板本体端可以额外拉线出来接收电压(即第二基底偏压电路280提供的正偏压v

bs

)。此外,再参照以下方程式可得知当v

bs

不为0且为正值时,临界电压v

th

的值会变小。因此,在此实施例中,当晶体管m71、m72、m73和m74的基板本体端接收到正

偏压v

bs

后,晶体管m71、m72、m73和m74的临界电压v

th

会下降。当晶体管m71、m72、m73和m74的临界电压v

th

下降,晶体管m71、m72、m73和m74可从五晶体管m5抽取更多的电流,因而使得可调整的可变增益范围将会增加。

29.如图2a所示,第三共轭匹配电路290可包括传输线tl11~tl14,以及电容c11和电容c12。传输线tl11的一端耦接至第五晶体管m5的漏极,另一端则会耦接至传输线tl12和电容c12。传输线tl12的一端耦接至传输线tl11和电容c12,另一端则会耦接至电容c11和电压源v

dd

。传输线tl13的一端耦接至电容c12,另一端则会耦接至传输线tl14以及输出射频输出信号rf

out

。传输线tl14的一端耦接至传输线tl13,另一端则会耦接至地。

30.当提供给可变增益放大器200的电压源v

dd

变低时,可变增益放大器200的可变增益范围将会变小。具体来说,当提供给可变增益放大器200的电压源v

dd

变低时,第一电流汲取电路230从第二晶体管m2抽取电流的能力以及第二电流汲取电路270从第五晶体管m5抽取电流的能力会变弱,因此,通过数字控制信号v

c

31、v

c

32、v

c

33和v

c

34和数字控制信号v

c

71、v

c

72、v

c

73和v

c

74可调整的增益范围将会减少(即可变增益放大器200的可变增益范围将会变小)。因此,在此实施例中,通过配置第一基底偏压电路240和第二基底偏压电路280在可变增益放大器200中,将可避免可变增益放大器200操作在低电压(即电压源v

dd

变低)时,可变增益范围会因而变小的问题。

31.特别说明地是,图2a中所示的第一共轭匹配电路210、第二共轭匹配电路250和第三共轭匹配电路290的电路架构,仅是用以说明本公开的实施例,但本公开不以此为限。在本公开的其他实施例中,也可依实际需求,采用和配置其他架构的共轭匹配电路。此外,在本公开的其他实施例中,在可变增益放大器200中所采用的共轭匹配电路的数量,也可依实际需求来做调整以及变更。

32.图2b是显示根据本公开的另一实施例所述的一可变增益放大器200的电路图。和图2a相比,图2b不同的地方在于,在此实施例中,电流汲取电路230和电流汲取电路270是以模拟电路的方式来实现。此外,在此实施例中,第一基底偏压电路240和第二基底偏压电路280的电路架构,也根据电流汲取电路230和电流汲取电路270的电路架构的不同而有所调整。以下将会针对图2b的电流汲取电路230、第一基底偏压电路240、电流汲取电路270和第二基底偏压电路280来做说明。关于图2b和图2a相同的部分,在以下就不再赘述。此外,特别说明地是,图2b中显示了包含两级放大器电路的可变增益放大器的架构,但本公开不以此为限。图2b的实施例也可应用在包含一级放大器或更多及放大器的可变增益放大器的架构中。举例来说,若可变增益放大器200仅包含一级放大器,可变增益放大器200就仅会包括一第一共轭匹配电路210(可对应第一共轭匹配电路110)、第一放大器电路220(可对应放大器电路120)、第一电流汲取电路230(可对应电流汲取电路130)、第一基底偏压电路240(可对应基底偏压电路140)和第二共轭匹配电路250(可对应第二共轭匹配电路150)。

33.如图2b所示,第一电流汲取电路230可包括第三晶体管m3,电阻r5,以及电容c13~c14。第三晶体管m3是一三重井(triple-well)晶体管。第三晶体管m3的栅极会耦接至电阻r5和电容c14,且会从电阻r5接收模拟控制信号v

c

1。在模拟控制信号v

c

1的控制下,第三晶体管m3可从第二晶体管m2汲取电流,以控制第一放大器电路220的增益。第三晶体管m3的源极会耦接至第一晶体管m1的漏极和第二晶体管m2的源极。第三晶体管m3的漏极会耦接至电容c13和电压源v

dd

。第三晶体管m3的基板本体端会接收第一基底偏压电路240提供的一正偏压

v

bs

。电容c13的一端耦接至地,另一端则耦接至第三晶体管m3的漏极和电压源v

dd

。电容c13可用以稳定第三晶体管m3的漏极电压。电容c14的一端耦接至第三晶体管m3的栅极以及电阻r5,另一端则耦接至地。电容c14可用以稳定第三晶体管m3的栅极电压。电阻r5的一端耦接至第三晶体管m3的栅极以及电容c14,另一端则耦接至模拟控制信号v

c

1。电阻r5可当成保护装置,以避免太大电流损坏第三晶体管m3。

34.以下将更进一步说明图2b的第一电流汲取电路230的操作。当第三晶体管m3根据模拟控制信号v

c

1导通时,流经第二晶体管m2的电流会被抽到第三晶体管m3,因而造成第二晶体管m2电流下降,因此,第二晶体管m2的转导值(gm2)会降低,进而使得第一放大器电路220的整体增益下降。因此,在此实施例中,可通过模拟控制信号v

c

1来调整流经第二晶体管m2的电流,进而达成控制第一放大器电路220的整体增益的目的。举例来说,若模拟控制信号v

c

1的电位越高,将使得第三晶体管m3会从第二晶体管m2抽取更多电流。当第二晶体管m2电流下降,将会使得第一放大器电路220的整体增益下降,反的亦然。

35.如图2b所示,第一基底偏压电路240可包括电阻r6。电阻r6会耦接至第三晶体管m3的基板本体端,以从电阻r6提供正偏压v

bs

至第三晶体管m3的基板本体端。由于第三晶体管m3是三重井(triple-well)晶体管,其基板本体端可以额外拉线出来接收电压(即第一基底偏压电路240提供的正偏压v

bs

)。此外,再参照以下方程式可得知当v

bs

不为0且为正值时,临界电压v

th

的值会变小。因此,在此实施例中,当第三晶体管m3的基板本体端接收到正偏压v

bs

后,第三晶体管m3的临界电压v

th

会下降。当第三晶体管m3的临界电压v

th

下降,模拟控制信号v

c

1可调整的电压范围将会变大,因而使得可调整的可变增益范围将会增加。

36.如图2b所示,第二电流汲取电路270可包括第七晶体管m7,电阻r7,以及电容c15~c16。第七晶体管m7是一三重井(triple-well)晶体管。第七晶体管m7的栅极会耦接至电阻r7和电容c16,且会从电阻r7接收模拟控制信号v

c

2。在模拟控制信号v

c

2的控制下,第七晶体管m7可从第五晶体管m5汲取电流,以控制第二放大器电路260的增益。第七晶体管m7的源极会耦接至第四晶体管m4的漏极和第五晶体管m5的源极。第七晶体管m7的漏极会耦接至电容c15和电压源v

dd

。第七晶体管m7的基板本体端会接收第一基底偏压电路280提供的一正偏压v

bs

。电容c15的一端耦接至地,另一端则耦接至第七晶体管m7的漏极和电压源v

dd

。电容c15可用以稳定第七晶体管m7的漏极电压。电容c16的一端耦接至第七晶体管m7的栅极以及电阻r7,另一端则耦接至地。电容c16可用以稳定第七晶体管m7的栅极电压。电阻r7的一端耦接至第七晶体管m7的栅极以及电容c16,另一端则耦接至模拟控制信号v

c

1。电阻r7可当成保护装置,以避免太大电流损坏第七晶体管m7。图2b的第二电流汲取电路270的操作类似图2b的第一电流汲取电路230。因此,在此就不再赘述。

37.如图2b所示,第二基底偏压电路280可包括电阻r8。电阻r8会耦接至第七晶体管m7的基板本体端,以从电阻r8提供正偏压v

bs

至第七晶体管m7的基板本体端。由于第七晶体管m7是三重井(triple-well)晶体管,其基板本体端可以额外拉线出来接收电压(即第二基底偏压电路280提供的正偏压v

bs

)。此外,再参照以下方程式可得知当v

bs

不为0且为正值时,临界电压v

th

的值会变小。因此,在此实施例中,当第七晶体管m7的基板本体端接收到正偏压v

bs

后,第七晶

体管m7的临界电压v

th

会下降。当第七晶体管m7的临界电压v

th

下降,模拟控制信号v

c

2可调整的电压范围将会变大,因而使得可调整的可变增益范围将会增加。

38.当提供给可变增益放大器200的电压源v

dd

变低时,可变增益放大器200的可变增益范围将会变小。具体来说,当提供给可变增益放大器200的电压源v

dd

变低时,模拟控制信号v

c

1和v

c

2可调整的电压范围将会变小,因而使得可变增益放大器200的可变增益范围将会变小。因此,在此实施例中,通过配置第一基底偏压电路240和第二基底偏压电路280在可变增益放大器200中,将可避免可变增益放大器200操作在低电压(即电压源v

dd

变低)时,可变增益范围会因而变小的问题。

39.图3是根据本公开的一实施例所述的增加可变增益范围的方法的流程图300。可变增益范围的方法适用可变增益放大器100和200。如图3所示,在步骤s310,配置至少一基底偏压电路在一可变增益放大器中,其中每一基底偏压电路会分别耦接至可变增益放大器的每一电流汲取电路。在步骤s320,从每一基底偏压电路提供一正偏压给其对应的电流汲取电路。

40.在本公开的增加可变增益范围的方法中,电流汲取电路可以是数字电路或是模拟电路。

41.在本公开的增加可变增益范围的方法中,每一电流汲取电路可包括一三重井(triple-well)晶体管,且每一基底偏压电路分别耦接至每一电流汲取电路的三重井晶体管的一基板本体端。当三重井晶体管的一基板本体端接收上述正偏压后,三重井晶体管的一临界电压会下降。

42.在一些实施例中,若电流汲取电路是数字电路,当电流汲取电路的三重井晶体管的临界电压会下降,电流汲取电路的三重井晶体管可从可变增益放大器的放大器电路抽取更多电流,因而使得可变增益放大器的可调整的可变增益范围将会增加。

43.在一些实施例中,若电流汲取电路是模拟电路,当电流汲取电路的三重井晶体管的临界电压会下降,模拟控制信号可调整的电压范围将会变大,因而使得可变增益放大器的可调整的可变增益范围将会增加。

44.在本公开的增加可变增益范围的方法中,通过配置基底偏压电路在可变增益放大器中,将可避免当可变增益放大器操作在低电压(即电压源v

dd

变低)时,可变增益范围会因而变小的问题。

45.在本说明书中以及权利要求书中的序号,例如“第一”、“第二”等等,仅是为了方便说明,彼此之间并没有顺序上的先后关系。

46.以上段落使用多种层面描述。显然的,本文的教示可以多种方式实现,而在范例中公开的任何特定架构或功能仅为一代表性的状况。根据本文的教导,任何本领域的技术人员应理解在本文公开的各层面可独立实现或两种以上的层面可以合并实现。

47.虽然本公开已以实施例公开如上,然其并非用以限定本公开,任何本领域的技术人员,在不脱离本公开的精神和范围内,当可作些许的更动与润饰,因此发明的保护范围当视后附的权利要求书所界定者为准。

48.【符号说明】

49.100、200 可变增益放大器

50.110、210 第一共轭匹配电路

51.120 放大器电路

52.130 电流汲取电路

53.140 基底偏压电路

54.150、250 第二共轭匹配电路

55.220 第一放大器电路

56.230 第一电流汲取电路

57.240 第一基底偏压电路

58.260 第二放大器电路

59.270 第二电流汲取电路

60.280 第二基底偏压电路

61.290 第三共轭匹配电路

62.300 流程图

63.c1~c16 电容

64.m1 第一晶体管

65.m2 第二晶体管

66.m3电三晶体管

67.m4 第四晶体管

68.m5 第五晶体管

69.m6 第六晶体管

70.m31~m34、m71~m74 晶体管

71.r1~r6 电阻

72.rf

in 射频输入信号

73.rf

out 射频输出信号

74.tl1~tl14 传输线

75.v

g

1、v

g

2、v

dd 电压源

76.v

bs 正偏压

77.v

th 临界电压

78.v

c

31~v

c

34、v

c

71~v

c

74 数字控制信号

79.v

c

1、v

c

2 模拟控制信号

80.s310~s320 步骤

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1