一种脉冲发生器和时钟倍频器

1.本技术涉及脉冲发生器技术领域,尤其涉及一种脉冲发生器和时钟倍频器。

背景技术:

2.时钟倍频器在现代有线通信系统中继续发挥着重要作用。随着每路数据速率的快速增长和大容量接口集成,对时钟倍增器提出了更高的要求,包括高运行速度、低抖动、小面积占用和低功耗。得益于注入锁定技术的发展,基于环形振荡器的脉冲注入锁定时钟倍频器(ring-oscillator pulse injection-locked clock multiplier,rpilcm)已成为产生低抖动时钟的最有希望的解决方案之一,同时它在面积占用和功耗方面有更大优势。它的高功率效率、紧凑的电路实现和高鲁棒性进一步使它在时钟倍频器、时钟恢复电路和频率同步器的设计中具有特殊的优势。

3.rpilcm的主要挑战是如何使振荡器的自由运行频率在工艺、电压和温度(processvoltagetemperature,pvt)变化范围内非常接近目标频率,从而保持锁定状态,并获得优异的杂散和相位噪声性能。当倍增因数随着一个注入周期内相关的累积相移随倍增因数线性增加而增加时,这种频率偏差尤其重要。

4.与rpilcm相关的另一个问题是如何选择脉冲宽度及其在不同pvt角的变化效果。频率跟踪问题吸引了大量的研究兴趣,虽然它们或多或少都有一些缺点,但许多技术已经发展起来。与频率跟踪问题不同的是,脉冲宽度调整是一个研究不充分的问题,过去没有引起足够的研究兴趣。然而,脉冲宽度的值及其变化会显著影响脉冲注入锁定振荡器(pules injection-locked oscillator,pilo)的跟踪带宽。

5.综上所述,需要提供一种能够调节脉冲宽度,使脉宽和注入周期形成固定比例,从而改善脉冲注入锁定振荡器的跟踪带宽的性能的脉冲发生器和时钟倍频器。

技术实现要素:

6.为解决以上问题,本技术提出了一种脉冲发生器和时钟倍频器。

7.一方面,本技术提出一种脉冲发生器,包括:第一与门、可调延迟单元组和第二与门;

8.第一与门的输出端与可调延迟单元组的输入端连接,可调延迟单元组的输出端与第二与门的输入端连接;

9.第一与门、可调延迟单元组和第二与门还连接电源电压;

10.可调延迟单元组的输入端还与滤波器的输出端连接。

11.优选地,所述可调延迟单元组,包括:一个非门、一个传输门、三个可调延迟单元和三个晶体管;

12.三个所述可调延迟单元包括第一可调延迟单元、第二可调延迟单元和第三可调延迟单元,其中,第一可调延迟单元的正输入端和非门的输出端连接,第一可调延迟单元的反向输入端与传输门的输出端连接,第一可调延迟单元和第二可调延迟单元以及第三可调延

迟单元依次串联,每个可调延迟单元的正输入端连接一个对应的所述晶体管的栅极,其反向输出端连接同一个晶体管的源极。

13.第二方面,本技术提出一种时钟倍频器,包括:互相连接的脉冲注入锁定振荡模块和追踪模块;

14.所述脉冲注入锁定振荡模块包括:顺次连接的如上所述的脉冲发生器和环形压控振荡器;

15.所述追踪模块包括:环路选择状态机、相位测量单元、鉴频鉴相单元、多路选择器和滤波器;所述多路选择器的输入端分别与环路选择状态机、相位测量单元、鉴频鉴相单元的输出端连接,所述多路选择器的输出端与所述滤波器的输入端连接;所述滤波器的输出端与所述脉冲发生器和环形压控振荡器的输入端连接;所述环路选择状态机、相位测量单元、和鉴频鉴相单元的输入端均连接所述环形压控振荡器的输出端;所述环路选择状态机和鉴频鉴相单元的输入端还连接参考输入信号,所述相位检测单元的输入端还连接所述脉冲发生器的输出端。

16.优选地,所述相位测量单元,包括:顺次连接的相位测量器和第一电荷泵;

17.所述相位测量器,包括多个第一晶体管,用于比较参考输入信号和脉冲注入锁定振荡模块生成的脉冲的相位,生成相位输出信号,发送至第一电荷泵;

18.所述第一电荷泵,包括多个第二晶体管和一个比较器,用于将所述相位输出信号转换为电流。

19.优选地,所述相位测量单元还包括极性探测器,所述极性探测器与第一电荷泵连接。

20.优选地,所述鉴频鉴相单元,包括:顺次连接的分频器、鉴频鉴相器和第二电荷泵;

21.分频器,用于对脉冲注入锁定振荡模块输出的时钟倍频信号进行分频,获得分频后的时钟倍频信号,发送至鉴频鉴相器;

22.鉴频鉴相器,用于比较分频后的时钟倍频信号和参考输入信号的频率和相位,确定误差信号,发送至第二电荷泵;

23.第二电荷泵,用于将误差信号转换为电流,并发送至所述多路选择器。

24.优选地,所述环路选择状态机,包括:频率锁定检测器和环路选择器;

25.所述频率锁定检测器包括:两个d触发器和一个第一异或门;其中,两个d触发器的输出端分别与第一异或门的两个输入端连接;

26.所述环路选择器包括:一个第二异或门,一个边缘计数器和一个定时器;其中,第二异或门的输出端与边缘计数器的输入端连接,定时器的输出端与边缘计数器的输入端连接。

27.优选地,所述脉冲发生器,根据参考输入信号、电源电压和所述追踪模块生成的控制电压,生成脉冲;

28.所述环形压控振荡器,根据电源电压生成时钟倍频信号;或根据电源电压和控制电压,生成时钟倍频信号;或根据电源电压、所述脉冲和控制电压,生成时钟倍频信号。

29.优选地,所述追踪模块包括两条环路,其中一条环路为锁相环路,另一条环路为定时调整环路;

30.所述环路选择状态机根据参考输入信号的频率、环形压控振荡器生成的时钟倍频

信号的频率以及当前运行的环路,选择所述两条环路中的一条环路,生成环路控制信号,发送至多路选择器;

31.所述相位测量单元根据脉冲和时钟倍频信号确定第一电流,发送至多路选择器;

32.所述鉴频鉴相单元根据所述参考输入信号和时钟倍频信号确定第二电流,发送至多路选择器;

33.所述多路选择器根据所述环路控制信号,开启所述定时调整环路,输出所述第一电流或开启所述锁相环路,输出所述第二电流;

34.所述滤波器对第一电流或第二电流进行滤波,得到控制电压,发送至所述脉冲注入锁定振荡模块。

35.本技术的优点在于:脉冲发生器产生的脉冲可以在不同的pvt拐角处自适应地调整脉冲宽度,一直保持一个固定的比例,从而改善环形压控振荡器生成的时钟倍频信号。

附图说明

36.通过阅读下文优选实施方式的详细描述,各种其他的优点和益处对于本领域普通技术人员将变得清楚明了。附图仅用于示出优选事实方案的目的,而并不认为是对本技术的限制。而且在整个附图中,用同样的参考符号表示相同的部件。在附图中:

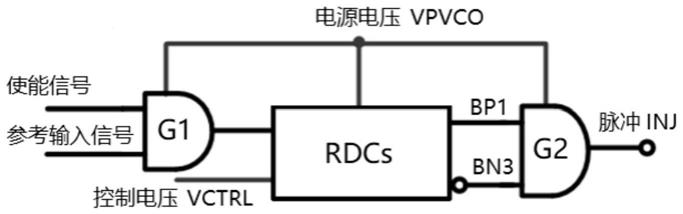

37.图1是本技术提供的一种脉冲发生器的电路示意图;

38.图2是本技术提供的一种脉冲发生器中的可调延迟单元组的电路示意图;

39.图3是本技术提供的一种时钟倍频器的示意图;

40.图4是本技术提供的一种时钟倍频器的详细示意图;

41.图5是本技术提供的一种时钟倍频器的环形压控振荡器的电路示意图;

42.图6是传统的脉冲发生器的电路示意图;

43.图7是本技术提供的一种时钟倍频器的环形压控振荡器中的延迟单元的电路示意图;

44.图8是本技术提供的一种时钟倍频器的相位测量单元的电路示意图;

45.图9是本技术提供的一种时钟倍频器的相位测量器的等效逻辑示意图;

46.图10是本技术提供的一种时钟倍频器的相位测量器的等效逻辑和极性选择示意图;

47.图11是本技术提供的一种时钟倍频器的极性探测器的示意图;

48.图12(a)是本技术提供的一种时钟倍频器的一种锁定条件的示意图;

49.图12(b)是本技术提供的一种时钟倍频器的另一种锁定条件的示意图;

50.图13是本技术提供的一种时钟倍频器的环路选择状态机的电路示意图;

51.图14(a)是本技术提供的一种时钟倍频器的频率追踪的目标谐波锁定的信号电平示意图;

52.图14(b)是本技术提供的一种时钟倍频器的频率追踪的谐波失锁的信号电平示意图;

53.图14(c)常规频率偏差的信号电平示意图;

54.图15是本技术提供的一种时钟倍频器的滤波器的电路示意图。

具体实施方式

55.下面将参照附图更详细地描述本公开的示例性实施方式。虽然附图中显示了本公开的示例性实施方式,然而应当理解,可以以各种形式实现本公开而不应被这里阐述的实施方式所限制。相反,提供这些实施方式是为了能够更透彻地理解本公开,并且能够将本公开的范围完整的传达给本领域的技术人员。

56.根据本技术的实施方式,提出一种脉冲发生器,如图1所示,包括:第一与门g1、可调延迟单元组rdcs和第二与门g2。第一与门的输出端与可调延迟单元组的输入端连接,可调延迟单元组的输出端与第二与门的输入端连接,第一与门、可调延迟单元组和第二与门还连接电源电压,可调延迟单元组的输入端还与滤波器的输出端连接。

57.如图2所示,可调延迟单元组,包括:一个非门、一个传输门、三个可调延迟单元和三个晶体管。三个可调延迟单元包括第一可调延迟单元rdc1、第二可调延迟单元rdc2和第三可调延迟单元rdc3,其中,第一可调延迟单元的正输入端和非门的输出端连接,第一可调延迟单元的反向输入端与传输门的输出端连接,第一可调延迟单元和第二可调延迟单元以及第三可调延迟单元依次串联,每个可调延迟单元的正输入端连接一个对应的晶体管的栅极,其反向输出端连接同一个晶体管的源极。

58.根据本技术的实施方式,还提出一种时钟倍频器,如图3所示,包括:互相连接的脉冲注入锁定振荡模块101和追踪模块102。

59.如图4所示,脉冲注入锁定振荡模块包括:顺次连接的本技术实施方式中提出的脉冲发生器(pulse generator)和环形压控振荡器(ringvoltage controlled oscillator,rvco);

60.追踪模块包括:环路选择状态机、相位测量单元、鉴频鉴相单元、多路选择器和滤波器;多路选择器的输入端分别与环路选择状态机、相位测量单元、鉴频鉴相单元的输出端连接,多路选择器的输出端与滤波器的输入端连接;滤波器的输出端与脉冲发生器和环形压控振荡器的输入端连接;环路选择状态机、相位测量单元、和鉴频鉴相单元的输入端均连接环形压控振荡器的输出端;环路选择状态机和鉴频鉴相单元的输入端还连接参考输入信号,相位检测单元的输入端还连接脉冲发生器的输出端。

61.相位测量单元,包括:顺次连接的相位测量器和第一电荷泵。

62.相位测量器,包括多个第一晶体管,用于比较参考输入信号和脉冲注入锁定振荡模块生成的脉冲的相位,生成相位输出信号,发送至第一电荷泵。

63.第一电荷泵,包括多个第二晶体管和一个比较器,用于将相位输出信号转换为电流。

64.相位测量单元还包括极性探测器(polarity detector),极性探测器与第一电荷泵连接。

65.鉴频鉴相单元,包括:顺次连接的分频器、鉴频鉴相器和第二电荷泵。

66.分频器,用于对脉冲注入锁定振荡模块输出的时钟倍频信号进行分频,获得分频后的时钟倍频信号,发送至鉴频鉴相器。

67.鉴频鉴相器,用于比较分频后的时钟倍频信号和参考输入信号的频率和相位,确定误差信号,发送至第二电荷泵。

68.第二电荷泵,用于将误差信号转换为电流,并发送至多路选择器。

69.环路选择状态机,包括:频率锁定检测器和环路选择器。

70.频率锁定检测器包括:两个d触发器和一个第一异或门;其中,两个d触发器的输出端分别与第一异或门的两个输入端连接。

71.环路选择器包括:一个第二异或门,一个边缘计数器和一个定时器;其中,第二异或门的输出端与边缘计数器的输入端连接,定时器的输出端与边缘计数器的输入端连接。

72.脉冲发生器,根据参考输入信号、电源电压和追踪模块生成的控制电压,生成脉冲(pulse)。

73.环形压控振荡器,根据电源电压生成时钟倍频信号;或根据电源电压和控制电压,生成时钟倍频信号;或根据电源电压、脉冲和控制电压,生成时钟倍频信号。

74.环形压控振荡器能够根据电源电压直接生成时钟倍频信号。其根据电源电压和控制电压,生成时钟倍频信号;或根据电源电压、所述脉冲和控制电压,生成时钟倍频信号,均为根据电源电压和控制电压,或者根据电源电压、控制电压和脉冲,对生成的时钟倍频信号进行调整并输出。

75.追踪模块包括两条环路,其中一条环路为锁相环路,另一条环路为定时调整环路。

76.环路选择状态机根据参考输入信号的频率、环形压控振荡器生成的时钟倍频信号的频率以及当前运行的环路,选择两条环路中的一条环路,生成环路控制信号,发送至多路选择器。

77.相位测量单元根据脉冲和时钟倍频信号确定第一电流,发送至多路选择器。

78.鉴频鉴相单元根据参考输入信号和时钟倍频信号确定第二电流,发送至多路选择器。

79.多路选择器根据环路控制信号,开启定时调整环路,输出第一电流或开启锁相环路,输出第二电流。

80.滤波器对第一电流或第二电流进行滤波,得到控制电压,发送至脉冲注入锁定振荡模块。

81.脉冲发生器,随定时调整环路的开启而开启,随锁相环路的开启而关闭。

82.频率锁定检测器,用于比较参考输入信号的频率和时钟倍频信号的频率,确定频率偏差次数是否超过阈值,若超过,则发送第一控制信号至环路选择器。

83.环路选择器,用于根据第一控制信号确定环路控制信号,发送至多路选择器,启动定时器,若定时器运行到达时间阈值,则生成第二控制信号,作为环路控制信号,发送至多路选择器。

84.相位输出信号为比较参考输入信号和脉冲的相位得到的误差信号。

85.第一控制信号用于开启锁相环路,第二控制信号用于开启定时调整环路。

86.下面,对本技术实施例进行进一步说明,如图4所示。

87.脉冲注入锁定振荡模块包括:环形压控振荡器和脉冲发生器。追踪模块为混合频率追踪环路,包括两条环路,一条环路为通过相位测量单元、多路选择器和滤波器的定时调整环路,一条环路为通过鉴频鉴相单元、多路选择器和滤波器的锁相环路。其中,鉴频鉴相单元为间歇性工作,脉冲发生器随相位测量单元工作而工作。

88.控制电压用于控制环形压控振荡器和脉冲发生器进行脉冲的宽度调整和频率调整,使脉冲的宽度和震荡周期保持一个合适的比例。环形压控振荡器和脉冲发生器的控制

电压均由追踪模块自适应调整,从而使环形压控振荡器的自由运行频率跟踪目标输出频率,并且注入信号(注入的脉冲)的脉冲宽度接近振荡周期的特定比例。

89.装置上电时,脉冲发生器与相位测量单元不工作,环形压控振荡器直接根据电源电压生成时钟倍频信号。由于参考输入信号(fref)的频率和时钟倍频信号(fout)的频率的差别过大,环路选择状态机根据参考输入信号的频率和时钟倍频信号的频率差别,控制多路选择器打开锁相环路,此时鉴频鉴相单元工作,同时定时器开始计时。鉴频鉴相单元根据参考输入信号和时钟倍频信号确定第二电流,发送至多路选择器。第二电流通过多路选择器,经过滤波器滤波,得到控制电压,输入至环形压控振荡器。环形压控振荡器根据控制电压和电源电压生成时钟倍频信号。当时鉴频鉴相单元的工作时间达到时间阈值时,环路选择状态机控制多路选择器打开定时调整环路。脉冲发生器根据参考输入信号、电源电压和控制电压生成脉冲,发送至相位测量器和环形压控振荡器。环形压控振荡器根据脉冲、控制电压和电源电压生成时钟倍频信号。相位测量器根据脉冲和时钟倍频信号,确定第一电流,通过多路选择器输入至滤波器。滤波器对第一电流进行滤波,得到控制电压,输入至脉冲发生器和环形压控振荡器,环形压控振荡器根据脉冲、电源电压和控制电压生成时钟倍频信号。环路选择状态机根据参考输入信号和时钟倍频信号的频率,时钟倍频信号的频率以及当前运行的已运行环路,确定待运行环路,生成环路控制信号,发送至多路选择器。若参考输入信号和时钟倍频信号的频率偏差次数未超过阈值,则继续控制多路选择器,使定时调整环路导通;若参考输入信号和时钟倍频信号的频率偏差次数超过阈值,则控制多路选择器,使锁相环路导通,同时鉴频鉴相单元运行,定时器开始定时。

90.如图1所示,脉冲发生器的第一与门g1的两个输入端分别输入参考输入信号和使能信号,同时,还接入电源电压。第一与门g1的输出端连接可调延迟单元组rdcs,可调延迟单元组rdcs还输入控制电压和电源电压。可调延迟单元组rdcs的两个输出信号分别和第二与门g2的输入端以及反向输入端连接,输出脉冲inj。

91.如图2所示,为本技术实施方式的脉冲发生器中的可调延迟单元组的电路示意图。其中,可调延迟单元组包括:一个非门、一个传输门、三个可调延迟单元和三个晶体管。信号分成两路,分别经过非门和传输门后,输入至第一可调延迟单元rdc1的输入端,其中非门的输出端与第一可调延迟单元rdc1的正输入端连接,传输门的输出端与可调延迟单元rdc1的反向输入端连接。每个可调延迟单元的输入端均连接一个晶体管,具体地,第一可调延迟单元rdc1的正输入端连接晶体管t31的栅极,第一可调延迟单元rdc1的反向输入端连接晶体管t31的源极,晶体管t31、t32和t33的门级均接地。第一可调延迟单元rdc1的反向输出端与第二可调延迟单元rdc2的正输入端以及晶体管t32的栅极连接,第一可调延迟单元rdc1的正输出端与第二可调延迟单元rdc2的反向输入端以及晶体管t32的源极极连接。第二可调延迟单元rdc2的反向输出端与第三可调延迟单元rdc3的正输入端以及晶体管t33的栅极连接,第二可调延迟单元rdc2的正输出端与第三可调延迟单元rdc3的反向输入端以及晶体管t33的源极极连接。每可调个延迟单元还输入电源电压。第一可调延迟单元rdc1的一路正输出bp1和第三可调延迟单元rdc3的一路反向输出bpn3作为可调延迟单元组的两个输出,分别输入至第二与门的两个输入端。

92.如图1所示,到达后一个与门的两个信号之间的延迟由可调延迟单元组产生。如图2所示,参考输入信号首先被转换成差分信号,到达第一可调延迟单元rdc1,然后被馈送到

后两个级联的可调延迟单元。第一可调延迟单元rdc1的正输出端和第三可调延迟单元rdc3的反向输出端分别生成两个信号bp1和bn3并进行与运算。相应地,注入至环形压控振荡器的脉冲(注入脉冲)的脉冲宽度应等于可调延迟单元组延迟时间的两倍。脉冲发生器通过与环形压控振荡器共享相同的电源电压vpvco和控制电压vctrl,可以在不同的pvt拐角处自适应地调整脉冲宽度。在本技术的实施方式中,可以通过手动改变低压差调节器的配置来适应角点变化,并通过及时调整的控制电压自动跟踪温度变化。

93.如图5所示,为环形压控振荡器,用于脉冲锁定。其中,环形压控振荡器包括四个延迟单元和四个晶体管。

94.如图6所示,为传统的脉冲发生器,包括两个与门和一个延迟单元组du。其中第三与门g3的输出端分别连接延迟单元组du和第四与门g4的一个输入端,延迟单元组du的反向输出端连接第四与门g4的另一个输入端。

95.环形压控振荡器中的延迟单元和传统的脉冲发生器中的延迟单元组的用途相同,具体的内部结构可以相同,也可以不同。

96.如图5所示,注入至环形压控振荡器的脉冲inj被施加到四个延迟单元中的一个(如图所示为dc3),而其他与延迟单元连接的注入晶体管(t41、t42和t44)被连接到地面以避免中断注入。环形压控振荡器的自由运行频率由电源电压vpvco和控制电压vctrl共同调节,电源电压调节以覆盖不同的工艺角,控制电压对环形压控振荡器进行自适应调节以跟踪温度变化。

97.如图7所示,为环形压控振荡器中的延迟单元的电路示意图。包括四个非门(g5、g6、g7和g8)、两个传输门和两个压控电容(c1和c2)。

98.如图8所示,为相位测量单元的电路示意图,包括第一电荷泵和相位测量器。其中第一电荷泵还包括开关电路。如图8所示,相位测量单元包括26个晶体管和一个比较器,相位测量器中的晶体管为第一晶体管,第一电荷泵中的晶体管为第二晶体管。其中,晶体管t1、t2、t3、t4、t5、t6、t7、t8、t9和t10为p沟道晶体管,晶体管t11、t12、t13、t14、t15、t16、t17、t18、t19、t20、t21、t22、t23、t24、t25和t26为n沟道晶体管。第一电荷泵采用在2.5v功率域中工作的大尺寸厚氧化物晶体管来实现高匹配精度,相位测量器利用1.2v晶体管来支持高工作速度。

99.其中,第一电荷泵中的开关电路包括晶体管t9、t10、t15、t16和比较器。比较器的正输入端与晶体管t10的漏极以及晶体管t16的漏极连接接于c点,c点的电流为icp。比较器的输出端与晶体管t19的漏极以及晶体管t15的漏极连接接于d点,比较器的负输入端还与比较器的输出端连接。晶体管t9和t10的源极连接接于e点,晶体管t15和t16的源极连接接于f点。t9的栅极和t16的栅极连接与en_p,t10的栅极和t15的栅极连接与en_n。

100.第一电荷泵中的晶体管t1的源极、t3的源极、t5的源极以及t7的源极均连接电源。t1的栅级与t7的栅极连接,且电流放大β倍,t17的栅级与t18的栅极连接,且电流放大β倍。t3的栅级与t5的栅极连接于p点,t13的漏极、t14的漏极以及t4的漏极也连接于p点。t4的栅级与t6的栅极连接于vbp,t12的栅级与t13的栅极连接于po_n。t2的栅极、t4的栅极、t6的栅极和t8的栅极连接于vbp,t11的栅极和t14的栅极连接于po_p。t1的漏极与t2的源极连接,t2的漏极与t1的栅极、t11的漏极以及t12的漏极连接于n点。t3的漏极与t4的源极连接,t5的漏极与t6的源极连接,t6的漏极于t17的漏极以及t17的栅极连接,t17的源极接地。t7的

漏极与t8的源极连接,t8的源极与e点连接,t18的漏极与f点连接,t18的源极接地。t11的源极和t13的源极相接于a点,t12的源极和t14的源极相接于b点。

101.如图9所示为相位测量器的等效逻辑示意图,其中,a点与开关s1的一端连接,s1的另一端分别与ps_p端以及接地连接。b点与开关s2的一端连接,s1的另一端分别与ps_n端以及接地连接。

102.如图10所示为相位测量器的等效逻辑和极性选择示意图,其中,n点与开关s3的一端连接,s3的另一端分别与psp_p端以及接地连接。p点与开关s4的一端连接,s4的另一端分别与psp_n端以及接地连接。n和p与开关s3以及s4连接的部分的输入电流为icp,电流icp与电流icp相等。

103.相位测量器中的晶体管t19的漏极和t20的漏极相接于a点,t23的漏极和t24的漏极相接于b点。t19的源极和t21的漏极连接,t21的源极接地。t20的源极和t22的漏极连接,t22的源极接地。t23的源极和t25的漏极连接,t25的源极接地。t24的源极和t26的漏极连接,t26的源极接地。

104.相位测量单元还包括极性探测器,通过引入极性探测器来保持边缘无关的输出。如图11所示,极性探测器包括两个d触发器,d1和d2。时钟倍频信号被分为clk_p和clk_n,其中,clk_p和脉冲输入至d1中,输出po_p信号,clk_n和脉冲输入至d2中,输出po_n信号。脉冲pulse(即脉冲inj)均输入至d触发器的时钟输入端。

105.如图12(a)所示,为一种锁定条件的示意图。如图12(b)所示,为另一种锁定条件的示意图。相位测量单元首先通过互补时钟的交叉点将注入的脉冲划分为两个部分:和然后,该宽度差被随后的第一电荷泵转换为电流,其中瞬时电流由极性选择晶体管的阈值电压和相位检测晶体管的等效导通电阻确定。如图12(a)和12(b)所示的两种锁定条件所示,环形压控振荡器的上升沿和下降沿(clk_p的升沿和下降沿,以及clk_n的升沿和下降沿)都可以锁定到注入脉冲。这使得检测到的相位差(即两个脉冲在ps_p和ps_n中的宽度差)呈现出边缘化的迹象。为了解决这一问题,引入了极性探测器来区分注入瞬间的边缘类型。特别地,当注入位置在两个锁定条件之间交换时,检测到的ps_p和ps_n的脉冲的连接将被po_p和po_n的极性选择信号交换。因此,对于图12(a)和12(b)示的两个条件,可以获得相同的psp_p和psp_n的等效脉冲,因此边缘相关输出和正反馈都可以避免。

106.如图13所示,为环路选择状态机的示意图,包括:频率锁定检测器(frequency lock detector,fld)和环路选择器(loop selector,ls)。频率锁定检测器用于输入被4分频之后的时钟倍频信号(div4_90)和参考输入信号(ref_clk),输出第一控制信号(fre_lock)至环路选择器。环路选择器根据第一控制信号和inj_lock信号,确定环路控制信号。环路控制信号包括控制定时调整环路开启的tpd_en信号和控制锁相环路的开启的pfd_en信号。inj_lock信号是由对极性探测器生成的po_p信号的进行延迟后得到的。

107.如图13所示,频率锁定检测器包括两个d触发器,d3和d4,以及一个异或门xor1。其中,被4分频之后的时钟倍频信号输入d3的d输入端,输入d4的时钟输入端,参考输入信号输入至d3的时钟输入端,输入至d4的d输入端。d3的输出信号fd1和d4的输出信号fd2均输入至异或门xor1中,异或门xor1的输出信号为第一控制信号,输入至环路选择器中。

108.环路选择器包括一个异或门xor2、饱和边缘计数器(saturation edge counter,sec)和定时器。其中,异或门xor2的两个输入端分别输入inj_lock信号和第一控制信号,输

出端连接饱和边缘计数器,将输出信号ind_lock信号输入至饱和边缘计数器中。饱和边缘计数器根据ind_lock信号和重置信号rst,确定环路控制信号。其中,第二环路控制信号为当定时器运行到达时间阈值时生成的用于控制多路选择器开启定时调整环路的控制信号。饱和边缘计数器还与定时器连接,定时器包括三个反相器(g21、g22和g23)、两个晶体管(t51和t52)、一个电容c11和一个电阻r11,用于根据pfd_en信号开始计时。以60ns为例,当计时器到达时间阈值60ns,则产生重置信号rst发送至饱和边缘计数器。

109.如图14(a)所示,可以看出,当ref_clk的时钟上升沿和div4_90的时钟低电平以及fd1信号,还有ref_clk的时钟高电平与fd2之间的距离与始终保持固定比例时,实现环形压控振荡器的注入锁定。如图14(b)所示,当比例无法保持固定时,锁定丢失。频率锁定检测器可以通过产生边缘跳变来快速地指示假谐波锁定或较大的频率偏差,但随着频率差变小,如图14(c)所示,常规频率偏差产生周期滑移需要更多的时间。为了加快锁丢失检测,inj_lock(即由极性探测器生成的po_p的延迟版本)也应用于环路选择器。inj_lock和fre_lock信号的总边缘跳变由环路选择器中的饱和计数器记录。在环路选择器中,inj_lock信号和fre_lock信号上的边缘跃迁首先计算异或,然后由饱和计数器记录。一旦数字达到特定值,环路选择器控制多路选择器把环路从定时调整环路切换到锁相环路,以启动锁获取过程。同时,启动时间常数约为60ns的定时器给图13中的节点a充电。当电压上升到逆变器的阈值时,环路选择器将重置,将锁相环路切换回定时调整环路,以启用注入锁定。如果环形压控振荡器成功锁定到目标频率的注入信号,则inj_lock和fre_lock都将保持静止,环路选择器也将保持静止,此为锁定丢失检测和锁定恢复过程。否则,将重复锁定丢失检测和锁定恢复过程,直到实现注入锁定。在初始启动期间,可以通过重复锁定丢失检测和锁定恢复过程来获得注入锁定。在正常运行期间,可以及时检测到锁丢失以激活锁定丢失检测和锁定恢复进程。由于在注入锁定模式期间,环路选择状态机中没有信号跳变,因此这种锁定丢失检测和锁定恢复内的功率成本可以忽略不计。

110.如图15所示,为滤波器的电路示意图。滤波器包括一个开关s1,三个电容(c21、c22和c23)和两个电阻(r21和r22),当定时调整环路开启时,开关s1闭合。

111.本技术的脉冲发生器可以自动跟踪pvt的变化,并保持脉冲宽度在延迟单元的两倍左右。通过定时调整环路输出的控制电压控制脉冲发生器和环形压控振荡器,可以实现自适应脉冲宽度调节,能够优化从9.32ps到1.47ps的脉冲变化,可以使跟踪带宽表现出良好的稳定性。相位测量单元中的电路采用的紧凑和简洁的信号连接使其能够以低功耗支持高运行速度;该电路提高了各电流镜的匹配精度和工作余量,从而优化了电流匹配精度;在该设计中消除了传统设计中的注入锁定和频率追踪环路锁定之间的竞争条件。环路选择状态机的锁定丢失检测和锁定恢复进程提高了锁定获取能力,如启动失败和可能的注入锁丢失都得到了完全解决。

112.本技术的实施方式中,脉冲发生器产生的脉冲可以在不同的pvt拐角处自适应地调整脉冲宽度,一直保持一个固定的比例,从而保证时钟倍频器一直处于性能最佳状态;通过环路选择状态机根据参考输入信号、时钟倍频信号,确定环路,通过相位测量单元输出控制电压,能够控制脉冲注入锁定振荡模块中的脉冲生成器根据电源电压和控制电压调整脉冲的宽度,改善脉冲注入锁定振荡器的跟踪带宽,从而改善环形压控振荡器生成的时钟倍频信号。本技术的实施方式还能够有效防止传统的注入锁定和锁相环路中的互拉问题,同

时保持了其良好的带内噪声抑制性能和较高的工作鲁棒性,使其成为实际应用中的一种有竞争力的选择。通过与匹配良好的第一电荷泵紧密结合的相位测量器来检测频偏生成控制电压;通过定时调整环路输出的控制电压控制脉冲发生器和环形压控振荡器,可以实现自适应脉冲宽度调节,保持pvt角的特定脉冲宽度;通过环路选择状态机实时进行锁定丢失检测和锁定恢复进程,能够快速进行锁丢失检测以及快速启动锁定恢复进程,提高锁捕获能力。

113.以上所述,仅为本技术较佳的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1