锁相环电路的制作方法

[0001]

本公开涉及锁相环电路。

背景技术:

[0002]

如hbm(高带宽存储器)等存储器装置有时包含pll(锁相环)电路,以生成与有待外部供应的参考时钟信号同步的内部时钟信号。pll电路有时包含相位频率检测器,以检测参考时钟信号与反馈时钟信号之间的相位差和频率差。如果供应给相位频率检测器的参考时钟信号的转换速率与反馈时钟信号的转换速率基本不同,则在由相位频率检测器执行的检测操作中会出现错误,这会产生内部时钟信号的相位偏差并且导致错误的操作。

技术实现要素:

[0003]

一方面,本公开涉及一种设备,所述设备包括:相位频率检测器,所述相位频率检测器被配置成比较第一时钟信号与第二时钟信号之间的相位差以生成相位检测信号;以及转换速率控制器,所述转换速率控制器被配置成当选择信号处于第一状态时降低所述第一时钟信号的转换速率。

[0004]

另一方面,本公开涉及一种设备,所述设备包括:相位频率检测器,所述相位频率检测器被配置成比较第一时钟信号与第二时钟信号之间的相位差以生成相位检测信号;时钟生成电路,所述时钟生成电路被配置成基于所述相位检测信号生成所述第二时钟信号,所述第二时钟信号的频率被控制成等于所述第一时钟信号的频率;以及转换速率控制器,所述转换速率控制器被配置成基于所述第一时钟信号的所述频率控制所述第一时钟信号的转换速率。

[0005]

另外一方面,本公开涉及一种设备,所述设备包括:相位频率检测器,所述相位频率检测器被配置成比较第一时钟信号与第二时钟信号之间的相位差;以及电流控制电路,所述电流控制电路被配置成基于所述第一时钟信号和所述第二时钟信号的转换速率控制所述相位频率检测器的操作电流。

附图说明

[0006]

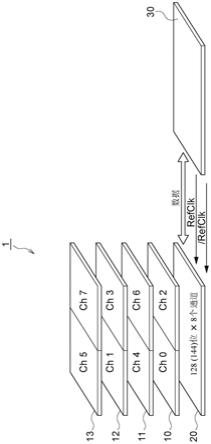

图1是展示了根据本公开的半导体装置的实例的示意性分解透视图。

[0007]

图2是展示了根据本公开的pll电路的配置的框图。

[0008]

图3是展示了根据本公开的分频器电路的配置的框图。

[0009]

图4是根据本公开的第一实例的相位频率检测器的电路图。

[0010]

图5a是当反馈时钟信号绕过分频器电路时的时钟信号的波形图。

[0011]

图5b是当反馈时钟信号穿过分频器电路时的时钟信号的波形图。

[0012]

图6是根据参考实例的时钟信号的波形图。

[0013]

图7是根据本公开的第二实例的相位频率检测器的电路图。

具体实施方式

[0014]

下文将参考附图详细地解释本发明的各个实施例。以下详细描述参考了附图,所述附图通过说明的方式示出了可以实践本发明的具体方面和实施例。足够详细地对这些实施例进行描述以使本领域技术人员能够实践本发明。可以利用其它实施例,并且在不脱离本发明的范围的情况下,可以进行结构、逻辑和电气改变。本文公开的各个实施例不一定是相互排斥的,因为一些公开的实施例可以与一或多个其它公开的实施例组合形成新的实施例。

[0015]

图1中所示出的半导体装置1包含控制芯片20和堆叠在控制芯片20上的四个存储器芯片10到13。存储器芯片10到13是例如dram(动态随机存取存储器)。存储器芯片10到13中的每一个存储器芯片被划分成两个通道,并且所述通道可以彼此独立地操作。因此,如数据输入/输出端子、地址端子、命令端子和时钟端子等端子被分配给通道中的每一个通道。存储器芯片10被划分成通道ch0和ch2、存储器芯片11被划分成通道ch4和ch6、存储器芯片12被划分成通道ch1和ch3并且存储器芯片13被划分成通道ch5和ch7。因此,半导体装置1具有包含总共八个通道的配置。分配给通道ch0到ch7的如数据输入端子、地址端子、命令端子和时钟端子等端子通过设置成穿透存储器芯片10到13的通孔导体连接到控制芯片20。例如,每个通道的i/o位数是144位,其中128位是实际数据,并且16位是ecc(错误校正码)数据。

[0016]

控制芯片20连接到存储器控制器30。存储器控制器30将彼此互补的参考时钟信号refclk和/refclk供应给控制芯片20。在接收到参考时钟信号refclk和/refclk时,控制芯片20生成图2中所示出的四相内部时钟信号ph0、ph90、ph180和ph270。与内部时钟信号ph0、ph90、ph180和ph270同步地执行控制芯片20与存储器控制器30之间的数据传输。

[0017]

四相内部时钟信号ph0、p90、ph180和ph270由图2中所示出的pll电路40生成。pll电路40包含相位频率检测器41,所述相位频率检测器检测参考时钟信号refclk和/refclk与反馈时钟信号fbclk和/fbclk之间的相位差和频率差,并且基于相位差和频率差生成检测信号up和dn。检测信号up和dn被供应给环路滤波器/电荷泵电路42。环路滤波器/电荷泵电路42对检测信号up和dn进行平均,以基于经平均的检测信号up执行充电,并且基于经平均的检测信号dn执行放电,从而改变偏置电位vcobias的电平。偏置电位vcobias被供应给vco(压控振荡器)电路43。vco电路43是根据偏置电位vcobias来改变彼此互补的输出时钟信号vcoclk和/vcoclk的频率以及四相内部时钟信号ph0、ph90、ph180和ph270的频率的振荡器电路。当参考时钟信号refclk和/refclk以及反馈时钟信号fbclk和/fbclk的频率相同并且具有预定相位差时,输出时钟信号vcoclk和/vcoclk以及内部时钟信号ph0、ph90、ph180和ph270的频率被设计成预定频率,例如,800mhz。输出时钟信号vcoclk和/vcoclk被供应给分频器电路44。当选择信号div有效时,分频器电路44对输出时钟信号vcoclk和/vcoclk进行分频以生成反馈时钟信号fbclk和/fbclk。当选择信号div被去激活时,分频器电路44可以停止分频操作。

[0018]

pll电路40进一步包含开关电路45。vco电路43、分频器电路44和开关电路45构成生成反馈时钟信号fbclk和/fbclk的时钟生成电路。当选择信号div有效时,开关电路45将从分频器电路44输出的反馈时钟信号fbclk和/fbclk供应给相位频率检测器41,并且当选择信号div无效时,将从vco电路43输出的输出时钟信号vcoclk和/vcoclk和反馈时钟信号

fbclk和/fbclk一样供应给相位频率检测器41。因此,当选择信号div被激活时,反馈时钟信号fbclk和/fbclk的频率降低。例如,在由vco电路43生成的输出时钟信号vcoclk和/vcoclk的频率是800mhz并且分频器电路44的分频比是8的情况下,当选择信号div处于无效状态时,反馈时钟信号fbclk和/fbclk的频率为800mhz,而当选择信号div处于有效状态时,反馈时钟信号fbclk和/fbclk的频率降低到100mhz。因为有时以比实际使用中更低的速度使用参考时钟信号refclk和/refclk来执行操作测试,所以需要反馈时钟信号fbclk和/fbclk的频率的此种切换。

[0019]

将可以输出具有小振幅和高转换速率的信号的电流模式逻辑(cml)用作生成参考时钟信号refclk和/refclk、输出时钟信号vcoclk和/vcoclk以及反馈时钟信号fbclk和/fbclk的电路。然而,输出时钟信号vcoclk和/vcoclk在分频器电路44中被临时转换成cmos(互补金属氧化物半导体)电平以降低电流消耗。例如,在图3中所示出的分频器电路44中,作为cml电平的输出时钟信号vcoclk和/vcoclk通过电平移位器46转换成cmos电平,通过计数器电路47进行分频,并且然后通过电平移位器48恢复成cml电平。因此,从分频器电路44输出的反馈时钟信号fbclk和/fbclk的转换速率低于输出时钟信号vcoclk和/vcoclk的转换速率。

[0020]

如图4中所示出的,相位频率检测器41包含检测单元a和转换速率控制单元b。检测单元a包含包括n沟道mos晶体管51和52的差分电路以及包括n沟道mos晶体管53和54的差分电路。参考时钟信号refclk输入到晶体管51和54的栅电极,并且参考时钟信号/refclk输入到晶体管52和53的栅电极。晶体管51和53的漏极共同连接到p沟道mos晶体管61。晶体管51和53的连接点的电位被检索为检测信号up。晶体管52和54的漏极共同连接到p沟道mos晶体管62。晶体管52和54的连接点的电位被检索为检测信号dn。偏置电位pbias被供应给晶体管61和62的栅电极。

[0021]

晶体管51和52的源极共同连接并且通过n沟道mos晶体管71、72和73接地。晶体管53和54的源极共同连接并且通过n沟道mos晶体管74、75和76接地。反馈时钟信号fbclk输入到晶体管71的栅电极,并且反馈时钟信号/fbclk输入到晶体管74的栅电极。检测单元a进一步包含串联连接并且通过操作电流i_pd的n沟道mos晶体管77和78。晶体管77、72和75构成电流镜电路。因此,与流过晶体管77的操作电流i_pd相同的电流或与所述操作电流成比例的电流流过晶体管72和75。使能信号en输入到晶体管78、73和76的栅电极。在未使用相位频率检测器41的时间段期间,使能信号en被去激活为低电平。

[0022]

利用以上所描述的配置,当参考时钟信号refclk和/refclk与反馈时钟信号fbclk和/fbclk具有相同频率并且其间的相位差为90

°

时,检测信号up的电平和检测信号dn的电平相匹配。另一方面,当参考时钟信号refclk和/refclk与反馈时钟信号fbclk和/fbclk之间的相位差偏离90

°

时,检测信号up的电平和检测信号dn的电平之间出现差异,并且电平差随着相位偏差增大而增加。如以上所描述的,检测信号up和dn被供应给环路滤波器/电荷泵电路42以调整偏置电位vcobias的电平。vco电路43根据偏置电位vcobias的电平来改变输出时钟信号vcoclk和/vcoclk的频率以使反馈时钟信号fbclk和/fbclk的频率与参考时钟信号refclk和/refclk的频率相匹配并且将其间的相位差设置成90

°

。

[0023]

转换速率控制单元b包含p沟道mos晶体管81和82以及电容器83和84。晶体管81和电容器83串联连接在供应有参考时钟信号refclk的线l1与供电线g之间。晶体管82和电容

器84串联连接在供应有参考时钟信号/refclk的线l2与供电线g之间。反相选择信号/div共同输入到晶体管81和82的栅电极。因此,在选择信号/div处于低电平的第一状态下,线l1连接到电容器83,并且线l2连接到电容器84,使得线l1和l2的电容增加,并且因此参考时钟信号refclk和/refclk的转换速率降低。因此,在这种情况下,转换速率降低的参考时钟信号refclk和/refclk输入到包含在检测单元a中的晶体管51到54。与此相反,在选择信号/div处于高电平的第二状态下,线l1从电容器83断开,并且线l2从电容器84断开,使得参考时钟信号refclk和/refclk的转换速率基本上没有降低。因此,在这种情况下,将转换速率基本上没有降低的参考时钟信号refclk和/refclk输入到包含在检测单元a中的晶体管51到54。

[0024]

如图5a中所示出的,在选择信号/div处于高电平的第二状态下,当参考时钟信号refclk和/refclk、输出时钟信号vcoclk和/vcoclk以及反馈时钟信号fbclk和/fbclk的频率彼此匹配并且参考时钟信号refclk和/refclk与反馈时钟信号fbclk和/fbclk之间的相位差为90

°

时,pll电路40被锁定。换言之,从参考时钟信号refclk和/refclk的交叉点到反馈时钟信号fbclk和/fbclk的交叉点的时间段t1与从反馈时钟信号fbclk和/fbclk的交叉点到参考时钟信号refclk和/refclk的交叉点的时间段t2相同。交叉点的电平为vc。图5a和5b中所示出的定时p1和p2指示当检测信号up和dn的改变开始时的定时以及当参考时钟信号refclk和/refclk之间的电位差已经增加了晶体管的阈值电压时的定时。定时p3指示当包含在相位频率检测器41中的晶体管71导通时的定时以及反馈时钟信号fbclk和/fbclk的相位差已经增加了晶体管的阈值电压时的定时。定时p4指示当反馈时钟信号fbclk和/fbclk彼此交叉的定时。定时p3恰好是定时p1与定时p2之间的中间定时。

[0025]

另一方面,如图5b中所示出的,在选择信号/div处于低电平的第一状态下,选择穿过分频器电路44的路径,并且因此参考时钟信号refclk和/refclk以及反馈时钟信号fbclk和/fbclk的频率变得低于输出时钟信号vcoclk和/vcoclk的频率。同样在这种情况下,当参考时钟信号refclk和/refclk与反馈时钟信号fbclk和/fbclk之间的相位差为90

°

时,pll电路40被锁定。换言之,从参考时钟信号refclk和/refclk的交叉点到反馈时钟信号fbclk和/fbclk的交叉点的时间段t3与从反馈时钟信号fbclk和/fbclk的交叉点到参考时钟信号refclk和/refclk的交叉点的时间段t4相同。原因如下。尽管反馈时钟信号fbclk和/fbclk的转换速率在第一状态下低于输出时钟信号vcoclk和/vcoclk的转换速率(因为反馈时钟信号fbclk和/fbclk是由分频器电路44生成的),但是转换速率控制单元b也降低了参考时钟信号refclk和/refclk的转换速率,并且因此两个转换速率理想地是相同的。

[0026]

当选择穿过分频器电路44的路径时,如图6中所示出的,如果未提供转换速率控制单元b,则反馈时钟信号fbclk和/fbclk的转换速率变得低于参考时钟信号refclk和/refclk的转换速率。在这种情况下,在从参考时钟信号refclk和/refclk的交叉点到反馈时钟信号fbclk和/fbclk的交叉点的时间段t3与从反馈时钟信号fbclk和/fbclk的交叉点到参考时钟信号refclk和/refclk的交叉点的时间段t4之间出现差异。结果,锁定pll电路40的条件改变,并且相对于参考时钟信号refclk和/refclk,内部时钟信号ph0、ph90、ph180和ph270的相位偏离设置值。与此相反,在本实施例中,当外部供应的参考时钟信号refclk和/refclk的频率低时,输入到检测单元a的参考时钟信号refclk和/refclk的转换速率通过转换速率控制单元b降低并且被理想地设置成与反馈时钟信号fbclk和/fbclk的转换速率相同。因此,即使改变了参考时钟信号refclk和/refclk的频率,相对于参考时钟信号refclk

和/refclk,内部时钟信号ph0、ph90、ph120和ph270的相位也总是符合设定值。

[0027]

根据图7中所示出的修改,可以将n沟道mos晶体管91和92添加到如在相位频率检测器41中的电流镜电路的输入侧。接收使能信号en和选择信号div的与门电路90的输出信号被供应给晶体管92的栅电极。因此,在选择信号div处于高电平的第一状态下,操作电流i_pd分支到晶体管77和91,并且因此在晶体管72和75中流动的操作电流减小。例如,当晶体管77和91具有同一栅极宽度时,与选择信号div处于低电平的第二状态相比,在选择信号div处于高电平的第一状态下,在晶体管72和75中流动的操作电流减半。因此,在反馈时钟信号fbclk和/fbclk中出现的波形失真变得更小。

[0028]

虽然已经在某些优选实施例和实例的上下文中公开了本发明,但是本领域技术人员将理解,本发明超出具体公开的实施例延伸到本发明的其它替代性实施例和/或用途及其显而易见的修改和等同物。另外,基于本公开,在本发明的范围内的其它修改对本领域技术人员而言将当是显而易见的。还设想了,可以对实施例的具体特征和方面进行各种组合或子组合并且所述组合或子组合仍然落入本发明的范围内。应理解,所公开的实施例的各个特征和方面可以彼此组合或取代以形成所公开的发明的不同模式。因此,其旨在使本文所公开的本发明中的至少一些的范围不应受到以上所描述的特定公开实施例的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1