功率晶体并联均流电路布局方法及其均流电路与流程

1.本发明关于一种功率晶体并联均流电路布局方法及其均流电路,特别是关于一种于电动车直流电转交流电的电力转换,使用功率晶体的开关电路,特别是关于一种大电流的功率脉波宽度调变(pwm)的单相或三相电力转换功率晶体均流电路及其布局方法。

背景技术:

2.在电动车的马达电力控制器应用中,都需要使用功率晶体作为直流电转交流电的电力转换,但现有技术的功率晶体电路板的电路布局,其大电流流动的铜箔形状为矩形,表示并联功率晶体每段的铜箔电阻皆为相同,根据欧姆定律位于并联两端的功率晶体电流会大于位于中间的功率晶体,若以稳态的电流分布来看,每颗功率晶体的电流差异不大于5%,若以瞬时电流分布来看,功率晶体的电流分布受到铜箔电感与电阻的影响,每颗功率晶体电流分布差异会增大。

3.现有的铜箔布线方式无论铜柱及铜箔位置及形状如何改变,均没有一个科学方法使得并联的功率晶体每颗分布电流相等。每位电路板绘图工程师均凭感觉及经验来绘制功率晶体电路板,虽然有电路板绘制规范之类的文件,但对于电流平均分布这方面没有一个明确的依据,这样使得绘制出的功率晶体电路板效果好坏相当程度变成一个试误(try&error)的过程。

4.如此一来会造成,当功率晶体开关导通时,因为分布电感的影响,使得并联功率晶体其中一颗超过其它并联的功率晶体,如图1所示三颗功率晶体并联的电流分布示意图,假设铜箔形成的阻抗为0.3mω,功率晶体的阻抗为6mω,电流300a经三组功率晶体并联分流后,因铜箔阻抗相同,流经两端功率晶体的电流(i1、i3)为101.613a与流经中间功率晶体的电流(i2)为96.77a,会有不小的差异,如此将会造成两端功率晶体寿命比预期设计来得短,一旦功率晶体寿命提前结束,其它并联的功率晶体会因而承担大于设计时的导通电流导致整体功率晶体组提前毁损。

5.更有甚者,当功率晶体的电路板铜箔布局不当,造成电流分布不均情况恶化,即使设计时有考虑电流宽裕度的情况下,在功率晶体导通或关闭的瞬间,相互并联的其中某颗功率晶体,其上的瞬间电流大于该功率晶体所能承受的最大电流值时,将使得因为铜箔布局不当造成必须多并联一颗甚至数颗功率晶体来保证电路工作正常,如此直接造成产品成本的增加,产品竞争力下降。

技术实现要素:

6.因此为解决上述现有技术存在的问题,需要针对功率晶体的并联均流进行电路的布局设计。本发明的目的即在于提供一种功率晶体并联均流电路布局方法及其均流电路,能够使并联的每颗功率晶体的电流能够在受到铜箔电阻及铜箔电感的影响下依然相等。如此可提升电路板铜箔的利用率,当铜箔利用率提升将意谓成本降低,减少整体电力控制器的体积,提升电力控制器的效率及寿命,降低电力控制器输出电源总谐波失真,从而降低总

谐波失真意谓可以连带提升输出马达的效率。

7.为达成上述目的,本发明主要技术特征在于提供一种功率晶体并联均流电路布局方法,首先备置一电路基板,其上形成多个铜箔线路分别电性连接多颗功率晶体的一第一端及一第二端;接着排列该多颗功率晶体呈偶数排,每一排皆有多颗功率晶体电性并联,且每两排功率晶体之间的间距呈一侧间隔近向另一侧逐渐间隔远的方式并排;最后布局第一端连接的铜箔线路的宽度与第二端连接的铜箔线路的宽度,呈相互交错对应的由宽渐窄及由窄渐宽的电路布局。

8.为达成上述目的,本发明次要技术特征在于提供一种功率晶体并联均流电路,包括:一电路基板及多颗功率晶体,电路基板上布设有多个铜箔线路;功率晶体呈偶数组排列于电路基板上,具有一第一端及一第二端,每一排皆由多颗功率晶体以铜箔线路分别电性连接第一端及第二端成并联状,且每两排功率晶体之间的间距呈一侧间隔近向另一侧逐渐间隔远的方式并排;其中第一端所连接的铜箔线路的宽度与第二端连接的铜箔线路的宽度,呈相互交错对应的由宽渐窄及由窄渐宽的电路布局。

9.为达成上述目的,本发明次要技术特征在于提供上述功率晶体并联均流电路布局方法及其均流电路,其中第一端连接的铜箔线路的阻抗值与第二端连接的铜箔线路的阻抗值呈相反趋势。

10.为达成上述目的,本发明次要技术特征在于提供上述功率晶体并联均流电路布局方法及其均流电路,其中第一端连接的铜箔线路,靠近电流流入方向的铜箔线路阻抗值为靠近电流流出方向的铜箔线路阻抗值的二分之一。

11.为达成上述目的,本发明次要技术特征在于提供上述功率晶体并联均流电路布局方法及其均流电路,其中第二端连接的铜箔线路,靠近电流流入方向的铜箔线路阻抗值为靠近电流流出方向的铜箔线路阻抗值的二倍。

附图说明

12.图1为现有的三颗功率晶体并联的电流分布示意图。

13.图2为本发明六组功率晶体实施例的排列位置示意图。

14.图3为本发明电路基板的铜箔布局示意图。

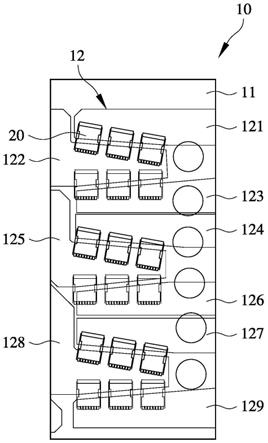

15.图4为本发明实施例电流流向示意图。

16.图5为本发明实施例的电流分流示意图。

17.图6为本发明实施例的电压高低趋势图。

18.图7为本发明实施例的铜箔阻抗分布示意图。

19.附图标记说明:10-电路基板;11-绝缘层;12-铜箔层;121-第一铜箔线路;122-第二铜箔线路;123-第三铜箔线路;124-第四铜箔线路;125-第五铜箔线路;126-第六铜箔线路;127-第七铜箔线路;128-第八铜箔线路;129-第九铜箔线路;20-功率晶体。

具体实施方式

20.本发明功率晶体并联均流电路主要设计一款能将电流平均分流给所有并联的功率晶体的均流布局电路,本发明的功率晶体可排列成二排组成单相半桥架构的脉波宽度调变功率电路,亦可排列成四排组成二相全桥架构的脉波宽度调变功率电路,还可排成六排

组成三相架构的脉波宽度调变功率电路。本发明六组三相的功率晶体说明如后。

21.请一并参阅图2及图3所示,图2为本发明以六组功率晶体实施例的排列位置示意图,图3为本发明电路基板的铜箔布局示意图。本发明包括一电路基板10及多颗功率晶体20,较佳地电路基板10可为一铝基板、铜基板或fr4耐燃材料等级的电路基板。电路基板10上布设有一功率晶体均流电路,由一绝缘层11及一铜箔层12形成有多个铜箔线路电性并联该多颗功率晶体20。然而有些fr4素材的电路基板不必然会有该绝缘层,因为在某些架构下电路基板需要与功率晶体某接脚端导通,故无绝缘层设计。如图3所示,该多个铜箔线路包括一第一铜箔线路121、一第二铜箔线路122、一第三铜箔线路123、一第四铜箔线路124、一第五铜箔线路125、一第六铜箔线路126、一第七铜箔线路127、一第八铜箔线路128及一第九铜箔线路129等九条。

22.该多颗功率晶体20可分成偶数组排列在电路基板10上,如图2为六组的功率晶体,该多颗功率晶体20可以为金属氧化物半导体场效晶体管(mosfet)、双载子接面晶体管(bjt)、绝缘闸极双极性晶体管(igbt)或功率碳化硅(sic)等可控固态开关功率元件,以mosfet为例其接脚具有一汲极端、一源极端及一闸极端,若以bjt为例则其接脚具有一集极端、一射极端及一基极端,若以igbt为例其接脚具有一集极端、一射极端及一闸极端,由于闸极端或基极端仅为控制信号的小电流不需分流故本发明不讨论,本发明将汲极端或集极端称为第一端,而源极端或射极端称为第二端。

23.每一排的功率晶体皆由多颗功率晶体20平行并排组成,如图2所示,有六排功率晶体20,每一排由三颗功率晶体20并联组成,而每两排的功率晶体20之间的间距呈现一侧间隔近,向另一侧逐渐间隔远的方式并排,如图2中由上往下数第一排与第二排的功率晶体20之间的间距是由右侧间隔近,中间的间隔较右侧远,左侧的间隔又较中间的远,而第三排与第四排之间,以及第五排与第六排之间的排列方式亦同第一排与第二排。

24.又如图3所示,该多颗功率晶体20以该多个铜箔线路分别电性连接第一端及第二端成功率晶体并联状。如第一铜箔线路121电性连接第一排功率晶体20的第一端,第二铜箔线路122电性连接第一排功率晶体20的第二端及第二排功率晶体20的第一端,第三铜箔线路123电性连接第二排功率晶体20的第二端,第四铜箔线路124电性连接第三排功率晶体20的第一端,第五铜箔线路125电性连接第三排功率晶体20的第二端及第四排功率晶体20的第一端,第六铜箔线路126电性连接第四排功率晶体20的第二端,第七铜箔线路127电性连接第五排功率晶体20的第一端,第八铜箔线路128电性连接第五排功率晶体20的第二端及第六排功率晶体20的第一端,第九铜箔线路129电性连接第六排功率晶体20的第二端。

25.该第一至第九铜箔线路121~129的宽度皆呈相互交错对应的由宽渐窄及由窄渐宽的电路布局。如图3所示,第一、第三、第四、第六、第七、第九铜箔线路121、123、124、126、127、129为由右至左由宽变窄布局,而第二、第五、第八铜箔线路122、125、128则由右至左由窄变宽布局。

26.再一并参阅图3及图4所示,图4为本发明实施例电流流向示意图,其中第一排与第二排的功率晶体20上流过的电流,由右向左流动,如图4的箭头方向,亦即由功率晶体20间隔近流向间隔远的方向,而第三与第四排的功率晶体20及第五排与第六排的功率晶体20上的电流则是由左向右流动,亦即由功率晶体20间隔远流向间隔近的方向。

27.再由电流方向观之,其中第一、第三、第四、第六、第七、第九铜箔线路121、123、

124、126、127、129的宽度是依电流方向呈由宽逐渐变窄的电路布局,而第二、第五、第八铜箔线路122、125、128的宽度是依电流方向呈由窄逐渐变宽的电路布局。

28.请一并参阅图5、图6及图7所示,图5为本发明实施例的电流分流示意图,图6为本发明实施例的电压高低趋势图,而图7为本发明实施例的铜箔阻抗分布示意图。由于本发明的铜箔线路布局法则,是依功率晶体20位置及电流流向进行宽窄变化的布局,使得电流在同一片铜箔上因宽度面积由宽变窄的趋势与铜箔阻抗趋势相同,使得在铜箔每一小段的电压差都相同。

29.如功率晶体20第一端连接的铜箔线路的阻抗值与第二端连接的铜箔线路的阻抗值呈相反趋势。较佳地,第一端连接的铜箔线路,靠近该电流流入方向的铜箔线路阻抗值为靠近电流流出方向的铜箔线路阻抗值的二分之一。较佳地,第二端连接的铜箔线路,靠近电流流入方向的铜箔线路阻抗值为靠近电流流出方向的铜箔线路阻抗值的二倍。

30.当并联功率晶体20距离最远的两颗功率晶体20的第一端及第二端铜箔阻抗相等,同时电阻趋势相反时,并联功率晶体20当中位于两端的功率晶体20的分配电流逐渐缩小,位于中间的功率晶体的分配电流逐渐增加,当铜箔阻抗由大变小的变化率到达某一适当的点时,流过每一颗并联的功率晶体20其各自的电流将达到相同。

31.如图5所示,本发明因铜箔线路阻抗的变化使得当电流300a流入二组并联的功率晶体20时,每颗功率晶体20都能均分100a的电流。又如图6所示,二组并联的功率晶体20,依电流流向使靠近电流流入端的第一端及第二端电压值较高,而靠近电流流出端的第一端及第二端电压值较低。再如图7所示,第一排功率晶体20的第一端靠近电流流入端的电阻较低,而靠近电流流出端的电阻较高,第二端则相反,靠近电流入端的电阻较高,而靠近电流流出端的电阻较低。

32.从以上分析可知,本发明利用功率晶体的排列间距变化以及第一端及第二端连接铜箔线路的宽度变化,使得功率晶体相对位置的铜箔阻抗变化率,流过每一颗功率晶体的电流达到相同,以提升功率晶体的使用效率及寿命,进而提升电力控制器的输出效能及降低产品的成本。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1