一种基于自动电流档位选择的超宽锁频范围频率锁定环形振荡器的制作方法

[0001]

本发明涉及频率锁定环型振荡器。特别涉及一种基于自动电流档位选择的超宽锁频范围频率锁定环型振荡器。

背景技术:

[0002]

频率锁定环形振荡器具有频率稳定性好、易于全集成、相位噪声相对较小的优点,被广泛用做片内信号源。

[0003]

频率锁定环形振荡器作为一种频率锁定系统,锁频范围是重要的技术指标。目前的宽频率锁定范围频率锁定系统,通常需要片外电路进行选通开关、配置寄存器等协同操作。它们存在着自动化程度不够、集成度不够等缺点。

[0004]

同时,目前的频率锁定系统,频率锁定上下限较少能达到数百倍。不能满足某些超宽带应用需求。

技术实现要素:

[0005]

本发明提出了一种基于自动电流档位选择的超宽锁频范围频率锁定环型振荡器。它可以全自动实现数百倍的锁频范围。

[0006]

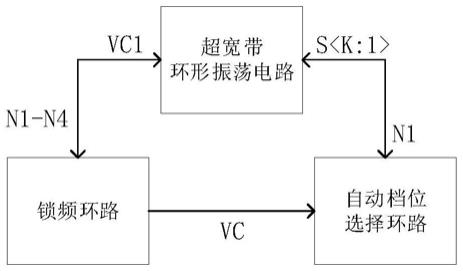

本发明的目的是通过以下技术方案来实现的:一种基于自动电流档位选择的超宽锁频范围频率锁定环型振荡器,所述超宽锁频范围频率锁定环形振荡器包括:一个超宽带环形振荡电路、一个锁频环路和一个自动档位选择环路;

[0007]

所述超宽带环形振荡电路,有两路输入,一路是锁频环路输出的控制电压vc1,另一路是自动档位选择环路输出的k位开关选通信号s<k:1>,输出是四个相位依次相差90

°

的方波信号n1、n2、n3、n4;

[0008]

所述锁频环路,输入是超宽带环形振荡电路输出的四个方波信号n1、n2、n3、n4,输出是自动档位选择环路的控制电压vc和超宽带环形振荡电路的控制电压vc1,所述vc1接入超宽带环形振荡电路,所述vc接入自动档位选择环路;

[0009]

所述自动档位选择环路,输入是锁频环路输出的控制电压vc和超宽带环形振荡电路输出的方波信号n1,输出是k位开关选通信号s<k:1>,接到超宽带环形振荡电路中。

[0010]

所述自动档位选择环路的控制电压vc具有高阈值和低阈值两个阈值,并且具有2

k-1个电流档位,高阈值和低阈值的设定要满足自动档位选择环路的第i个电流档位g

i

之后的任意相邻档位覆盖的频率范围没有间隔,记每个档位内最高频率与最低频率的比值为m,i满足:

[0011][0012]

所述自动档位选择环路根据控制电压vc与高阈值和低阈值之间的大小关系以及超宽带环形振荡电路控制电压vc1调谐增益的正负性,自动选择电流档位;具体如下:

[0013]

若vc1调谐增益为正,vc大于高阈值时电流档位自增,vc小于低阈值时电流档位自减,vc介于高低阈值之间时,电流档位不变;

[0014]

若vc1调谐增益为负,vc大于高阈值时电流档位自减,vc小于低阈值时电流档位自增,vc介于高低阈值之间时,电流档位不变。

[0015]

进一步地,所述超宽带环形振荡电路包括:

[0016]

两个全差分环振单元u1、u2,它们的电流端口isn、isp分别对应连接到一起,u1的反相输出端连在u2的同相输入端,连接节点记为na,u1的反相输入端连在u2的反相输出端,连接节点记为nb,u1的同相输出端连在u2的反相输入端,连接节点记为nc,u1的同相输入端连在u2的同相输出端,连接节点记为nd;

[0017]

四个完全相同的压控电容c1、c2、c3、c4,它们均有一端同时连在控制电压vc1上,c1另一端连在节点na上,c2另一端连在节点nb上,c3另一端连在节点nc上,c4另一端连在节点nd上;

[0018]

一个偏置电路,由nmos电流源mn0a、mn0b和pmos电流源mp0以及参考电流源组成,mn0a的栅极漏极相连后接到参考电流源,产生偏置电压vrn,mn0a和mn0b的源极都接在参考地,mn0b的栅极接在偏置电压vrn、漏极接在mp0的漏极,mp0栅极漏极相连产生偏置电压vrp、源极接到电源;

[0019]

k个nmos电流源mn1、mn2、

……

mnk,k大于或等于8,它们的源极均接地,漏极均接在u1和u2的电流端口isn上,栅极分别接在对应的开关sn1、sn2、

……

snk的输出端;所述开关sn1、sn2、

……

snk均为2输入1输出开关,输入1均接地,输入2均接在偏置电压vrn上;

[0020]

k个pmos电流源mp1、mp2、

……

mpk,k大于或等于8,它们的源极均接在电源,漏极均接在u1和u2的电流端口isp上,栅极分别接在对应的开关sp1、sp2、

……

spk的输出端;所述开关sp1、sp2、

……

spk均为2输入1输出开关,输入1均接在电源,输入2均接在偏置电压vrp上;

[0021]

开关选通信号s1、

……

sk分别控制对应的开关sn1和sp1、

……

snk和spk的导通方式,第j个开关选通信号sj为低时,第j个nmos电流源的开关snj和第j个pmos电流源的开关spj的输出与各自的输入1相连,否则输出与输入2相连,其中j=1,2,

……

k;

[0022]

若干个反相器,它们分为四组,每组内的反相器串联在一起,且每组反相器个数相同,每组输入分别接在节点na、nb、nc、nd上,输出是相位依次相差90

°

的方波信号n1、n2、n3、n4。

[0023]

进一步地,所述锁频环路包括:

[0024]

一个状态信号产生电路,它的输入是超宽带环形振荡电路输出的方波信号n1、n2、n3、n4,输出是状态信号rst、ch、sh、sl;

[0025]

八个开关s1a、s1b、s2a、s2b、s3a、s3b、s4a和s4b,所述s1a、s2a和s3a的一端连接在一起,记为节点vp0,所述s1b、s2b和s3b的一端连接在一起,记为节点vn0,所述s3a的另一端和s4a的一端连接在一起记为节点vp1,所述s3b的另一端和s4b的一端连接在一起记为节点vn1;所述s4a的另一端与一个运算放大器opa1的同相输入端连接在一起,节点记为vp,所述s4b的另一端与运算放大器opa1的反相输入端连接在一起,节点记为vn;开关s1a另一端接地,开关s1b另一端接电源,开关s2a另一端接在一个电阻rref1上,开关s2b另一端接在一个电阻rref2上;rref1另一端接在电源上,rref2另一端接地;状态信号rst控制开关s1a和

s1b,状态信号ch控制开关s2a和s2b,状态信号sh控制开关s3a和s3b,状态信号sl控制开关s4a和s4b;

[0026]

五个电容cref、cs、cp、cn、cl,电容cref两端分别接在节点vp0和vn0,电容cs两端分别接在节点vp1和vn1,电容cp两端分别接在节点vp和参考地,电容cn两端分别接在节点vn和opa1的输出端上,电容cl一端接在opa1的输出端上,另一端接在参考地;opa1的输出即为自动档位选择环路的控制电压vc;电容cref和电阻rref1、rref2一起设定锁定频率,所述两个电阻rref1、rref2阻值相等。

[0027]

一个电平移位电路,输入为opa1的输出,输出为超宽带环形振荡电路的控制电压vc1。

[0028]

进一步地,所述自动档位选择环路包括:

[0029]

三个电阻r1、r2、r3,r1一端接到电源,另一端与电阻r2的一端相连,节点记为rh,r2的另一端r3一端相连,节点记为rl,r3的另一端接地;

[0030]

两个迟滞比较器comp1、comp2,comp1的同相输入端和comp2的反相输入端分别接在节点rh、rl上,comp1的反相输入端和comp2的同相输入端相连接在输入的控制电压vc上;comp1、comp2分别输出判决信号nh、nl;

[0031]

一个计数方向产生电路,输入为判决信号nh和nl,输出方向信号up;

[0032]

一个计数时钟产生电路,输入是超宽带环形振荡电路输出的方波信号n1、判决信号nh和nl、方向信号up和k位开关选通信号s<k:1>,输出档位选择时钟信号clk;

[0033]

一个k位可逆计数器,输入是方向信号up和档位选择时钟信号clk,输出k位开关选通信号s<k:1>接入超宽带环形振荡电路中。

[0034]

进一步地,所述k个nmos电流源,导通电流以mn1为基准按照二进制规律变化,mn2的导通电流是mn1导通电流的2倍,mnk的导通电流是mn1导通电流的2

k-1

倍。所述k个pmos电流源,导通电流以mp1为基准按照二进制规律变化,mp2的导通电流是mp1导通电流的2倍,mpk的导通电流是mp1导通电流的2

k-1

倍。

[0035]

进一步地,所述偏置电路,mn0a和mn0b的电流按照1:1复制,mn0a与电流源mn1的导通电流、mp0与电流源mp1的导通电流都是按照1:1复制。

[0036]

进一步地,三个电阻r1、r2、r3设定了自动档位选择环路的控制电压vc的高阈值和低阈值。

[0037]

进一步地,所述计数方向产生电路,根据判决信号nh、nl和超宽带环形振荡电路的控制电压vc1调谐增益的正负性,产生方向信号up。如果控制电压vc1的调谐增益为正数,nh由1变0则up=1、nl由1变0则up=0;如果电压vc1的调谐增益为负数,nh由1变0则up=0、nl由1变0则up=1。如果nh=1且nl=1,方向信号up保持不变。

[0038]

进一步地,所述计数时钟产生电路,如果nh=1且nl=1,不输出信号。如果up=1且s<k:1>全是1或up=0且s<k:2>全是0,也不输出信号。其他情况下,均对方波n1进行分频作为输出。

[0039]

进一步地,所述k位可逆计数器,当输入方向信号up=1时,进行增计数,方向信号up=0时,进行减计数。

[0040]

本发明提出的基于自动电流档位选择的超宽锁频范围频率锁定环形振荡器的工作原理如下所述。

[0041]

供电电流和负载电容是决定环型振荡器振荡频率的主要因素。一般而言,供电电流越大,负载电容越小,振荡频率越高。所以,可以通过调节供电电流和负载电容来控制环振振荡频率。

[0042]

锁频环路和自动档位选择环路分别通过调节负载电容、调节供电电流来控制频率。锁频环路输出的电压vc1连续改变环形振荡电路中负载电容的容值,自动档位选择环路按照二进制的规律改变供电电流。它们分别执行细调功能和粗调功能。

[0043]

锁频环路有两个功能:鉴频、积分。锁频环路中的两个电阻rref1、rref2、电容cref和s1a、s1b、s2a、s2b、s3a、s3b组成鉴频电路;四个电容cs、cp、cn、cl、开关s4a、s4b和运算放大器opa1组成积分电路。

[0044]

鉴频电路通过对电容cref进行充电来判定当前频率是否等于电阻rref1、rref2和电容cref设定的频率。它共有三个工作状态:复位相、充电相、采样相。三个工作状态分别受状态信号rst、ch、sh的控制。

[0045]

在复位相,电容cref上极板直接连到地,下极板直接连到电源,上下两极板的电压差ve=-vdd。在充电相,电容cref上极板通过电阻rref1连接到电源进行充电,下极板通过电阻rref2连接到地进行放电。如果当前振荡频率等于设定频率,充电相结束时电容cref上下两极板电压差ve=0。在采样相,积分电路对电压差ve进行采样。

[0046]

积分电路有两个工作状态:采样相、积分相。它们分别受状态信号sh、sl的控制。在采样相,电容cs对电压差ve进行采样。在积分相,运算放大器组成的积分电路对电容cs上下极板的电压差进行积分。

[0047]

锁频环路通过鉴频和积分让当前振荡频率逐渐靠近由电阻rref1、rref2和电容cref设定的频率,它执行细调功能。

[0048]

为了保证较低的相位噪声,调谐增益不会太大。所以当供电电流固定,只有压控电容的控制电压变化时,锁频环路能锁定的频率范围十分有限。为了实现宽锁频范围,引入自动档位选择环路,自动执行粗调功能,在众多电流档位中自动选择最合适的一个。

[0049]

下面说明自动档位选择环路的工作原理。

[0050]

先假设超宽带环形振荡电路中电压vc1的调谐增益为正。

[0051]

控制电压vc向上越过了高阈值v

thh

时,判决信号nh由1变0。这说明设定频率高于目前电流档位内的最高频率,电流需要增大。此时自动档位选择环路自增电流档位。方向信号up=1,k位可逆计数器进行增计数。

[0052]

控制电压vc向下越过了低阈值v

thl

时,判决信号nl由1变0。这说明设定频率低于目前电流档位内的最低频率,电流需要减小。此时自动档位选择环路自减电流档位。方向信号up=0,k位可逆计数器进行减计数。

[0053]

如果超宽带环形振荡电路中电压vc1调谐增益为负,判决信号nh由1变0时,说明设定频率低于目前电流档位内的最低频率,电流需要减小,此时自动档位选择环路自减电流档位;判决信号nl由1变0时,说明设定频率高于目前电流档位内的最高频率,电流需要增大,此时自动档位选择环路自增电流档位。

[0054]

控制电压vc大于高阈值v

thh

或者低于低阈值v

thl

时,计数方向产生电路保持方向信号up,计数时钟产生电路产生时钟驱动k位可逆计数器调节电流档位。这与电压vc1调谐增益的正负无关。

[0055]

当控制电压vc稳定介于高阈值v

thh

和低阈值v

thl

之间时,计数时钟产生电路不产生时钟,k位可逆计数器不再动作,电流档位保持不变。此时的电流档位是最合适的电流档位。

[0056]

在最高的电流档位且up=1或在最低电流档位且up=0时,计数时钟产生电路都不再产生时钟信号,避免自动档位选择环路循环遍历电流档位。

[0057]

由于k个nmos电流源和k个pmos电流源是按照二进制规律变化的,除去所有电流源都不导通这一状态,共有2

k-1个电流档位。2

k-1个电流档位自动切换,使得锁频范围可以达到数百倍。

[0058]

上述技术方案具有如下优点:频率锁定范围可以达到数百倍;频率锁定过程是全自动的,无需片外电路辅助协同,易于全集成。

附图说明

[0059]

图1是本发明总体框图。

[0060]

图2是本发明中超宽带环形振荡电路图。

[0061]

图3是本发明中锁频环路图。

[0062]

图4是本发明中自动档位选择环路图。

[0063]

图5是本发明中超宽带环形振荡电路实例图

[0064]

图6是本发明中锁频环路实例图。

[0065]

图7是本发明中自动档位选择环路实例图。

[0066]

图8是电流档位和每个档位内频率范围图。

具体实施方式

[0067]

下面结合附图和实施例,对本发明的具体实施方式作进一步详细描述。以下实施例用于说明本发明,但不用来限制本发明的范围。

[0068]

本实施例中k=8,并且超宽带环形振荡电路中控制电压vc1的调谐增益是正数。记电源电压为vdd。

[0069]

本发明实施例中的超宽带环形振荡电路如图2和5所示。

[0070]

两个全差分环振单元u1、u2,四个压控电容c1、c2、c3、c4,mn0a、mn0b、mp0和参考电流源组成的偏置电路,8个反相器都按照前文所述和图中所示进行连接,在此不再赘述。

[0071]

8个nmos电流源mn1、

……

mn8,8个pmos电流源mp1、

……

mp8和16个开关sn1、sp1、

……

sn8、sp8也按照前文所述和图中所示进行连接,在此不再赘述。

[0072]

本发明实施例的锁频环路如图3和6所示。

[0073]

八个开关s1a、s1b、s2a、s2b、s3a、s3b、s4a和s4b,两个电阻rref1、rref2,五个由同一个单位电容复制若干份数组成的电容cref、cs、cp、cn、cl,和一个运算放大器opa1都按照前文所述和图中所示进行连接,在此不再赘述。运算放大器opa1具有轨到轨输入范围,开环电压增益大于60db,相位裕度大于60

°

。

[0074]

状态信号产生电路采用三个nand latch来实现,它们输出的状态信号rst、ch、sh是占空比为25%的方波,相位依次超前90

°

。sh与sl之间是取反关系。vc1和vc之间的电平移位用源极跟随器实现。

[0075]

本发明实施例的自动档位选择环路如图4和7所示。

[0076]

两个迟滞比较器comp1、comp2、三个阻值相等的电阻r1、r2、r3和8位可逆计数器按照前文所述和图中所示进行连接,在此不再赘述。

[0077]

计数方向产生电路采用nand latch实现。因为电压vc1调谐增益是正数,判决信号nh接在置数端、nl接在复位端。计数时钟产生电路采用12分频电路和逻辑门组成,实现前文所述的功能。本实施例中控制电压vc的高阈值为v

thh

=2

·

vdd/3+δv,控制电压vc的低阈值为v

thl

=vdd/3-δv,δv是迟滞比较器门限宽度的一半。

[0078]

本实例的具体工作过程和工作原理如下所述。

[0079]

上电后,起初超宽带环形振荡电路处在自由振荡状态,输出四个方波信号n1、n2、n3、n4接入锁频环路。锁频环路开始工作,振荡频率逐渐接近电阻rref1、rref2和电容cref设定的频率。自动档位选择环路也开始自动搜寻最合适的电流档位。

[0080]

在鉴频电路复位相,开关s1a、s1b导通,其余开关关断。节点vp0、vn0的电压分别是

[0081]

vp0=0

ꢀꢀꢀ

(公式1)

[0082]

vn0=-vdd

ꢀꢀꢀ

(公式2)

[0083]

在鉴频电路充电相,开关s2a、s2b导通,其余开关关断。节点vp0、vn0的电压随时间变化的表达式是

[0084][0085][0086]

假设充电相持续时间为t1。充电相结束后,电容cref上下两极板电压差ve为

[0087][0088]

如果满足

[0089]

t1=2 ln 2 r

ref

c

ref

ꢀꢀꢀ

(公式6)

[0090]

那么充电相结束后,电容cref上下两极板的电压差ve就为零。把2 ln 2 r

ref

c

ref

记作t0,称作设定充电时间,对应的频率称作设定频率。

[0091]

如果充电相结束电容cref上下两极板的电压差ve为零,那么实际充电时间等于设定充电时间,实际振荡频率等于设定频率,环路进入锁定状态。

[0092]

如果ve为正,说明实际充电时间比设定充电时间要长,实际振荡频率小于设定频率。反馈环路需要拉高振荡频率。如果ve为负,说明实际充电时间比设定充电时间要短,实际振荡频率大于设定频率。反馈环路需要拉低振荡频率。

[0093]

鉴频电路和积分电路同时处在采样相。在采样相,开关s3a、s3b导通,其余开关关断。电容cref与cs并联,cs对电压差ve进行采样。在本实施例中,令cs=cref。

[0094]

假设在采样相之前,电容cs上下极板的电压差为v

n

,而在采样相结束时,cs上下极板的电压差为v

n+1

。那么按照电荷守恒可以得到

[0095][0096]

采样相之后,电容cs上下极板的电压差,就是它原来的电压差与电压差ve的平均值。每次采样,积分电路都可以获得电压差ve的信息。

[0097]

在积分电路积分相,开关s4a、s4b闭合。运算放大器组成的积分电路对电容cs上下极板的电压差进行积分。推导得到在复频域积分相输出电压表达式为

[0098][0099]

公式8表示了一个积分系统。其中v

out

(0)由采样相结束后电容cs上下极板电压差v

n+1

决定。而电压v

n+1

含有电压差ve的信息。所以,在积分相,积分电路能够对鉴频电路输出的电压差ve进行积分。

[0100]

如果当前振荡频率低于设定频率,那么充电相持续时间高于设定充电时间,充电相结束后,电压差ve大于0。经过积分后,控制电压vc上升。由于调谐增益为正数,所以振荡频率也上升。新电压差ve比之前变小,向0靠近。重复上述过程,直到电压差ve=0,环路锁定。

[0101]

如果当前振荡频率高于设定频率,那么充电相持续时间低于设定充电时间,充电相结束后,电压差ve小于0。经过积分后,控制电压vc下降。由于调谐增益为正数,所以振荡频率也下降。新电压差ve的绝对值比之前变小,向0靠近。重复上述过程,直到环路锁定。

[0102]

在本实施例中,状态信号ch是占空比为25%的方波信号,充电相持续时间是当前振荡周期的1/4。所以如果环路锁定,则有

[0103][0104]

所以设定频率,即锁定时的振荡频率为

[0105][0106]

在本实施例中,除去8个nmos电流源和8个pmos电流源都不导通这一状态,共有255个电流档位。如图8所示,记这些电流档位为g

i

,并记每个电流档位内通过调节压控电容可以获得的最大频率和最小频率分别是f

h

(i)、f

l

(i),其中i=1,2,

……

255,每个档位内最大频率和最小频率的比值为m,本实施例中m为1.2。为了保证能连续覆盖所有频率,相邻两个档位之间频率关系满足f

h

(i)≥f

l

(i+1),其中i大于等于5,即从第5档位开始,能连续覆盖所有频率。

[0107]

如果电流档位为g

i

时,锁频环路正常工作,而且控制电压vc持续上升,向上越过高阈值v

thh

。此时自动档位选择环路k位可逆计数器自增,电流档位自增至档位g

i+1

。如果设定频率小于f

h

(i+1),控制电压vc会降低到高阈值v

thh

和低阈值v

thl

之间,自动档位选择环路不再动作;如果设定频率大于f

h

(i+1),自动档位选择环路继续自增至档位g

i+2

,直至找到最合适的电流档位。

[0108]

如果电流档位为g

i

时,锁频环路正常工作,而且控制电压vc持续降低,向下越过低阈值v

thl

。此时自动档位选择环路k位可逆计数器自减,电流档位自增至档位g

i-1

。如果设定频率大于f

l

(i-1),控制电压vc会上升到高阈值v

thh

和低阈值v

thl

之间,自动档位选择环路不再动作;如果设定频率小于f

l

(i-1),自动档位选择环路继续自减至档位g

i-2

,直至找到最合适的电流档位。

[0109]

当控制电压vc稳定介于高阈值v

thh

和低阈值v

thl

之间时,计数时钟产生电路不产生时钟,k位可逆计数器不再动作,电流档位保持不变。此时的电流档位是最合适的电流档位。

[0110]

电流档位是g

255

且up=1、电流档位是g1且up=0时,计数时钟产生电路不再产生时钟,以保证设定频率大于f

h

(255)或者小于f

l

(1)时,自动档位选择环路不会循环遍历电流档位。

[0111]

在本发明实施例中,255个电流档位,可以实现数百倍锁频范围。

[0112]

同时,从本发明实施例中可以看出,本发明无需外部电路协同,使用电阻rref1、rref2和电容cref设定频率后,电路会在超宽频率范围内自动锁定到设定频率,且频率锁定过程是全自动的,无需片外电路辅助协同,易于全集成。

[0113]

以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明技术原理的前提下,还可以做出若干改进和变型,这些改进和变型也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1