一种针对POWER-DOWN模式的高可靠性AD采样方法与流程

一种针对power-down模式的高可靠性ad采样方法

技术领域

[0001]

本发明应用于机载伺服运动控制领域,涉及一种针对power-down模式的高可靠性ad采样方法。

背景技术:

[0002]

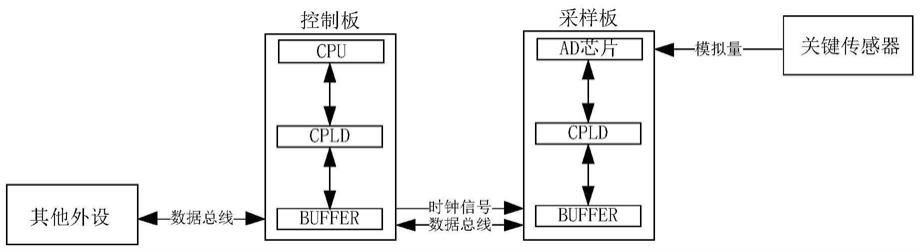

机载伺服运动控制系统的很多关键传感器输出是模拟量,需要进行ad采样转为数字量,然后通过数据总线传输给cpu进行数字闭环控制。如果cpu收到的ad采样数据不正常会导致闭环回路控制失效,损坏伺服运动机构。因此ad采样流程必须兼顾快速性、准确性和可靠性。ad采样流程如图1所示。

[0003]

采样板上的ad芯片是ad采样流程中最核心的器件,如果ad芯片在busy信号下降沿时convst信号为低电平就会进入power-down(低功耗)模式,不再进行ad采样,返回的数据为进入该模式前最后一次采样的数据,造成ad采样流程失效。ad芯片进入power-down模式的原理如图2所示。

技术实现要素:

[0004]

要解决的技术问题

[0005]

为了解决ad芯片进入power-down模式导致ad采样流程失效的问题,本发明提出了一种针对power-down模式的高可靠性ad采样方法。

[0006]

技术方案

[0007]

一种针对power-down模式的高可靠性ad采样方法,其特征在于采样板包括ad芯片、cpld和buffer,控制板包括cpu、cpld和buffer,两者之间有时钟信号传输和数据总线连接,包含以下四个措施:

[0008]

第一:降低时钟信号的地环路干扰:调整控制板cpld和采样板cpld上的时钟管脚和地管脚,让时钟管脚和地管脚在设计允许范围内尽可能接近,从而减小时钟信号地环路面积;

[0009]

第二:避开信号抖动区域设置convst信号:采样板cpld延后2个时钟周期再设置convst信号,可以保证避开时钟信号和数据信号抖动区域,确保设置的convst信号正确;

[0010]

第三:ad芯片进入power-down模式检测:每次执行ad转换指令,即convst信号先置0然后置1,后判断convst信号和busy信号状态,如果发现同时为低电平,表示ad芯片进入power-down模式,状态标志位ad_status_flag置为0;否则,状态标志位ad_status_flag置为1;

[0011]

第四:ad芯片进入power-down模式恢复:每次读取ad芯片采样数据的时候,先读取状态标志位ad_status_flag的值,如果该值为1,表示ad芯片工作正常,则读取ad芯片采集数据;如果该值为0,表示ad芯片进入power-down模式,此时对ad芯片进行复位和初始化操作,然后重新获取ad芯片采集数据。

[0012]

有益效果

[0013]

本发明提出的一种针对power-down模式的高可靠性ad采样方法,包含两方面内容:一方面是采取措施降低ad芯片进入power-down模式的概率;另一方面是当ad芯片进入power-down模式后采取措施让其快速恢复正常工作,满足正常ad采样流程的时间要求。

[0014]

本发明有效降低了ad芯片进入power-down模式的概率,一旦进入power-down模式后也可以快速恢复,满足正常ad采样流程的时间要求,保证正确性的基础上提高了采样流程的可靠性,为机载伺服系统实现精确闭环控制提供了准确的关键传感器信息。

附图说明

[0015]

图1是ad采样流程图。

[0016]

图2是ad芯片进入power-down模式的原理。

[0017]

图3是ad芯片进入power-down模式的检测及恢复流程。

具体实施方式

[0018]

现结合实施例、附图对本发明作进一步描述:

[0019]

为了保证ad采样流程快速准确可靠,本发明提出了一种针对power-down模式的高可靠性ad采样方法,具体包含以下四个措施:

[0020]

第一,降低时钟信号的地环路干扰。由于地环路干扰影响时钟信号会导致ad芯片进入power-down模式,因此需要采取措施降低地环路干扰。由于地环路面积越大,地环路干扰越强,在其他信号地环路面积不变的条件下,减小时钟信号地环路面积可以降低地环路干扰。具体措施是优化控制板cpld逻辑和采样板cpld逻辑,调整两块cpld上的时钟管脚和地管脚,让时钟管脚和地管脚在设计允许范围内尽可能接近,从而减小时钟信号地环路面积。

[0021]

第二,避开信号抖动区域设置convst信号。控制板cpu发出写信号后,由于振铃现象会对数据总线上的时钟信号和数据信号造成抖动,若此时采样板cpld根据数据信号设置convst信号会发生采集错误导致ad芯片进入power-down模式。因此,采样板cpld延后2个时钟周期再设置convst信号,可以保证避开时钟信号和数据信号抖动区域,确保设置的convst信号正确。

[0022]

第三,ad芯片进入power-down模式检测。在采样板cpld逻辑中进行ad芯片进入power-down模式检测,具体措施是每次执行ad转换指令(convst信号先置0然后置1)后判断convst信号和busy信号状态,如果发现同时为低电平,表示ad芯片进入power-down模式,状态标志位ad_status_flag置为0;否则,状态标志位ad_status_flag置为1。

[0023]

第四,ad芯片进入power-down模式恢复。在控制板操作系统中进行ad芯片进入power-down模式恢复,具体措施是每次读取ad芯片采样数据的时候,先读取状态标志位ad_status_flag的值,如果该值为1,表示ad芯片工作正常,则读取ad芯片采集数据;如果该值为0,表示ad芯片进入power-down模式,此时对ad芯片进行复位和初始化操作,然后重新获取ad芯片采集数据。

[0024]

ad芯片进入power-down模式的检测及恢复流程如图3所示。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1