1.本发明涉及一种传输电路,特别是涉及一种可以减少接口数量的传输电路。

背景技术:2.在现有技术中,物理层(physical layer)和数据链路层(data link layer)之间常会利用千兆媒体独立接口(gigabit media independent interface,gmii)或简化千兆媒体独立接口(reduced gigabit media independent interface,rgmii)来进行数据的传输。千兆媒体独立接口包括了2个时钟脉冲接口、8个数据输入接口、8个数据输出接口、2个输出控制信号接口以及2个输入控制信号接口。在每个时钟脉冲周期中,千兆媒体独立接口的每个数据接口都可以接收或输出一比特的信号。由于千兆媒体独立接口所需的接口数量较多,因此芯片内部的走线较为复杂,进而增加整体的面积需求,并且过多的接口也使得外部电路的设计较为复杂而不具有弹性。

3.为了减少接口的数量,简化千兆媒体独立接口可以在每个时钟脉冲的正缘和负缘触发的时间点,都可以各自传送1比特的信号。如此一来,在数据接口数量减半的情况下,简化千兆媒体独立接口仍然可以维持与千兆媒体独立接口相同的传输频率。然而,不论是简化千兆媒体独立接口或千兆媒体独立接口,都有固定的接口数量,因此当应用所需要的传输速度较低时,则仍然难以提供更有弹性的设计。

技术实现要素:4.本发明的一实施例提供一种传输电路,传输电路包括数据输入接口、串并转换器、接口译码器、并串转换器及处理单元。

5.串并转换器与数据输入接口耦合,串并转换器将至少从数据输入接口所接收的多个数据信号转换为并行信号组,并行信号组包括多个并行传输的数字信号。接口译码器与串并转换器耦合,接口译码器译码并行信号组以产生并行传输的译码数据信号组。并串转换器与接口译码器耦合,并串转换器将译码数据信号组转换为串行传输的多个输入数据信号。处理单元与并串转换器耦合,处理单元接收并处理输入数据信号。

6.本发明的另一实施例提供一种传输系统,传输系统包括上层传输电路、第一下层传输电路以及第二下层传输电路。

7.上层传输电路包括第一上层输出接口和第二上层输出接口。

8.第一下层传输电路包括第一数据输入接口、第一串并转换器、第一接口译码器、第一并串转换器以及第一处理单元。

9.第一数据输入接口与上层传输电路的第一上层输出接口耦合。第一串并转换器与第一数据输入接口耦合,第一串并转换器将至少从第一数据输入接口所接收的多个第一数据信号转换为第一并行信号组,第一并行信号组包括多个并行传输的数字信号。第一接口译码器与第一串并转换器耦合,第一接口译码器译码第一并行信号组以产生并行传输的第一译码数据信号组。

10.第一并串转换器与第一接口译码器耦合,第一并串转换器将第一译码数据信号组转换为串行传输的多个第一输入数据信号。第一处理单元与第一并串转换器耦合,第一处理单元接收并处理多个第一输入数据信号。

11.第二下层传输电路包括第二数据输入接口、第二串并转换器、第二接口译码器、第二并串转换器以及第二处理单元。

12.第二数据输入接口与上层传输电路的第二上层输出接口耦合。第二串并转换器与第二数据输入接口耦合,第二串并转换器将至少从第二数据输入接口所接收的多个第二数据信号转换为第二并行信号组,第二并行信号组包括多个并行传输的数字信号。第二接口译码器与第二串并转换器耦合,第二接口译码器译码第二并行信号组以产生并行传输的第二译码数据信号组。

13.第二并串转换器与第二接口译码器耦合,第二并串转换器将第二译码数据信号组转换为串行传输的多个第二输入数据信号。第二处理单元与第二并串转换器耦合,第二处理单元接收并处理多个第二输入数据信号。

附图说明

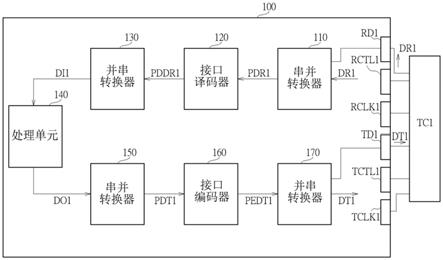

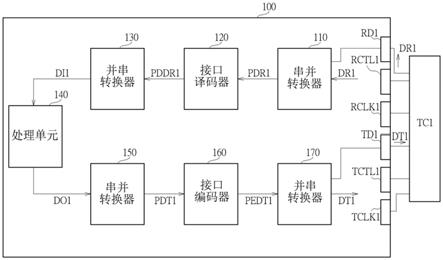

14.图1是本发明一实施例的传输电路的示意图。

15.图2是本发明另一实施例的传输电路的示意图。

16.图3是本发明一实施例的传输系统的示意图。

17.图4是本发明另一实施例的传输系统的示意图。

具体实施方式

18.图1是本发明一实施例的传输电路100的示意图。在图1中,传输电路100可耦合到另一传输电路tc1,并可与传输电路tc1进行数据的传输。在有些实施例中,传输电路100可以例如是物理层(physical layer)的传输电路,而传输电路tc1则可以是数据链路层(data link layer)的传输电路。在现有技术中,若物理层的传输电路与数据链路层的传输电路之间要以简化千兆媒体独立接口(reduced gigabit media independent interface,rgmii)来进行数据传输,则两个传输电路必须各自包括四个上行数据传输接口和四个下行数据传输接口,因此在设计上较不具弹性。相比之下,传输电路100则可以通过一个传输接口来进行上行数据的传输和/或一个传输接口来进行下行数据的传输。

19.在图1中,传输电路100可以包括数据输入接口rd1、串并转换器(serial to parallel converter)110、接口译码器120、并串转换器(parallel to serial converter)130以及处理单元140。

20.数据输入接口rd1可以从传输电路tc1的对应接口串行地接收多个数据信号dr1。串并转换器110可以与数据输入接口rd1耦合,并可以将从数据输入接口rd1所接收的多个数据信号dr1转换为并行信号组pdr1,并行信号组pdr1可以包括多个并行传输的数字信号。

21.接口译码器120可以与串并转换器110耦合,并可以对并行信号组pdr1进行译码以产生并行传输的译码数据信号组pddr1。在有些实施例中,界面译码器120可以根据简化千兆媒体独立接口的规范对并行信号组pdr1进行译码。在此情况下,并行信号组pdr1可以包括8个同步传输的数字信号。由于串并转换器110可以将串行传输的多个数据信号dr1转换

为并行传输的并行信号组pdr1,因此接口译码器120可以利用一般简化千兆媒体独立接口所使用的译码机制来进行译码,而无须另外重新设计,进而简化设计上的复杂度。

22.此外,由于在将多个数据信号dr1转换为并行传输的并行信号组pdr1的过程中,必须等待并行信号组pdr1中的每一个数字数据都接收齐全后,才能一并输出,因此接口译码器120可以操作在较低的频率,而可以节省电能损耗。举例来说,若传输电路100的时钟脉冲频率为125m赫兹,则在正负缘都可以用来判读传输数据的情况下,传输电路100和tc1之间的数据传输速率可以达到每秒250m比特。在此情况下,若并行信号组pdr1中包括8个比特时,接口译码器120的时钟脉冲仅需要操作在31.25m赫兹就足以满足目标的数据传输速率。也就是说,传输电路100可以通过调整接口译码器120的操作频率来执行其他同样使用简化千兆媒体独立接口的功能,达到电路共享的功效。

23.并串转换器130可与接口译码器120耦合,并可以将译码数据信号组pddr1转换为串行传输的多个输入数据信号di1。处理单元140可以与并串转换器130耦合,并可以接收和处理这些输入数据信号di1。

24.在图1中,传输电路100也可以向传输电路tc1传输数据。举例来说,处理单元140也可以产生串行传输的多个输出数据信号do1。传输电路100还可以包括串并转换器150、接口编码器160、并串转换器170以及数据输出接口td1。

25.串并转换器150可以与处理单元140耦合,并可以将多个输出数据信号do1转换为并行信号组pdt1,而并行信号组pdt1可以包括多个并行传输的数字数据。

26.接口编码器160可以与串并转换器150耦合,并可以将并行信号组pdt1编码以产生并行传输的编码数据信号组pedt1。在有些实施例中,接口译码器120和接口编码器160可以由两个独立的电路来实施,然而在有些实施例中,接口译码器120和接口编码器160也可以合并设计,或可共享部分的功能模块。

27.并串转换器170可以与接口编码器160耦合,并可以将编码数据信号组pedt1转换为串行传输的多个数据信号dt1,而数据输出接口td1则可以串行地输出多个数据信号dt1至传输电路tc1。

28.由于传输电路100可以在内部将串行数据信号转换为并行信号,再将并行信号转换为串行数据信号,因此可以利用单一个数据输入接口rd1来接收传输电路tc1所传来的数据,并且可以利用单一个数据输出接口td1来输出数据至传输电路tc1。然而在有些实施例中,传输电路100也可以利用两个或三个资料输入接口来接收传输电路tc1所传来的数据,并且利用两个或三个数据输出接口来输出数据至传输电路tc1。

29.图2是本发明一实施例的传输电路200的示意图。传输电路100和200具有相似的结构,并可以根据相似的原理操作。然而,传输电路200还可以包括数据输入接口rd2和数据输出接口td2。

30.在此情况下,数据输入接口rd2和rd1可共同接收数据信号dr1。也就是说,在时钟脉冲频率维持于125m赫兹的情况下,通过数据输入接口rd1和rd2来并行接收数据信号即可达到每秒250m比特的传输速度。此时,串并转换器210可以将从数据输入接口rd1和rd2所接收的多个数据信号dr1转换为并行信号组pdr1。如此一来,传输电路200便同样可以使用接口译码器120来进行译码。此外,在此实施例中,若要维持每秒250m比特的传输速度,则可以将接口译码器120的操作频率调整为62.5m赫兹以配合传输电路200接收数据信号dr1的速

度。

31.接着,第一并串转换器230便可以将译码数据信号组pddr1转换为串行传输的多个输入数据信号di1,并交由处理单元240接收和处理。

32.相似地,当传输电路200要传送数据信号dt1至传输电路tc1时,处理单元240可以产生串行传输的多个输出数据信号do1,而串并转换器250则可以将多个输出数据信号do1转换为并行信号组pdt1,并通过接口编码器160来进行编码。接着并串转换器270可以将编码数据信号组pedt1转换为串行传输的多个数据信号dt1,然后再通过数据输出接口td1和数据输出接口td2并行输出多个串行的数据信号dt1至传输电路tc1。

33.也就是说,通过串并转换的机制,传输电路就可以根据传输的需求选择适当的资料接口数量来进行简化千兆媒体独立接口上的数据传输,使得电路设计更具有弹性。

34.此外,在图1中,传输电路100可以包括输出控制接口tctl1、输出时钟脉冲接口tclk1、以及输入控制接口rctl1和输入时钟脉冲接口rclk1。在传输电路100通过数据输出接口td1输出数据时,传输电路100可以通过输出控制接口tctl1输出控制信号,并通过输出时钟脉冲接口tclk1输出时钟脉冲信号,以使传输电路tc1可以顺利接收数据。相对地,在通过数据输入接口rd1接收数据时,输入控制接口rctl1可以接收控制信号,而输入时钟脉冲接口rclk1则可以接收时钟脉冲信号,以确保传输电路100可以顺利接收数据。

35.在有些实施例中,传输电路之间可以采用一对多的方式传输。举例来说,数据链路层的上层传输电路可以与多个物理层的下层传输电路相耦合并进行数据传输。在此情况下,多个下层传输电路可以共同耦合到上层传输电路的控制接口和时钟脉冲接口,以减少两层传输电路之间的走线。

36.图3是本发明一实施例的传输系统10的示意图。在图3中,传输系统10可以包括下层传输电路100a、100b、100c和100d,以及上层传输电路uc1。在有些实施例中,下层传输电路100a、100b、100c和100d可以与传输电路100具有相同的构造,并且可以根据相同的原理操作,而上层传输电路uc1则可以与传输电路tc1具有相同的构造,并可以根据相同的原理操作。举例来说,上层传输电路uc1可以是对应于数据链路层(data link layer)的传输电路,而下层传输电路100a、100b、100c和100d则可以是对应于物理层(physical layer)的传输电路。

37.在图3中,上层传输电路uc1可以包括上层输出接口utd1、utd2、utd3和utd4、上层输入接口urd1、urd2、urd3和urd4、上层输出控制接口utctl1、上层输出时钟脉冲接口utclk1、上层输入控制接口urctl1和上层输入时钟脉冲接口urclk1。

38.在此情况下,下层传输电路100a的数据输入接口rd1a可以耦合至上层输出接口utd1,而下层传输电路100a的数据输出接口td1a可以耦合至上层输入接口urd1。下层传输电路100b的数据输入接口rd1b可以耦合至上层输出接口utd2,而下层传输电路100b的数据输出接口td1b可以耦合至上层输入接口urd2。下层传输电路100c的数据输入接口rd1c可以耦合至上层输出接口utd3,而下层传输电路100c的数据输出接口td1c可以耦合至上层输入接口urd3。下层传输电路100d的数据输入接口rd1d可以耦合至上层输出接口utd4,而下层传输电路100d的数据输出接口td1d可以耦合至上层输入接口urd4。

39.此外,下层传输电路100a、100b、100c和100d的输入控制接口rctla、rctlb、rctlc和rctld都可以耦合至上层输出控制接口utctl1,而下层传输电路100a、100b、100c和100d

的输入时钟脉冲接口rclka、rclkb、rclkc和rclkd都可以耦合至上层输出时钟脉冲接口utclk1。下层传输电路100a、100b、100c和100d的输出控制接口tctla、tctlb、tctlc和tctld都可以耦合至上层输入控制接口urctl1,而下层传输电路100a、100b、100c和100d的输出时钟脉冲接口tclka、tclkb、tclkc和tclkd都可以耦合至上层输入时钟脉冲接口urclk1。也就是说,在传输系统10中,上层传输电路uc1可以通过相同的输入/输出控制接口和输入/输出时钟脉冲接口来控制下层传输电路100a、100b、100c和100d。

40.在传输系统10中,每个下层传输电路100a、100b、100c和100d可以仅包括一个数据输出接口和一个数据输入接口,然而在有些实施例中,下层传输电路100a至100d也可以包括两个或三个数据输入/输出接口。

41.图4是本发明一实施例的传输系统20的示意图。传输系统20可以包括下层传输电路200a和200b以及上层传输电路uc1。下层传输电路200a和200b可与传输电路200具有相同的结构。下层传输电路200a可以包括数据输入接口rd1a和rd2a,以及数据输出接口td1a和td2a。数据输入接口rd1a和rd2a可以分别耦合至上层输出接口utd1和utd3,而数据输出接口td1a和td2a可分别耦合至上层输入接口urd1和urd3。相似地,下层传输电路200b可以包括数据输入接口rd1b和rd2b以及数据输出接口td1b和td2b。数据输入接口rd1b和rd2b可以分别耦合至上层输出接口utd2和utd4,而数据输出接口td1b和td2b可以分别耦合至上层输入接口urd2和urd4。

42.也就是说,下层传输电路200a可以同时通过资料输入接口rd1a和rd2a来接收上层输出接口utd1和utd3所传来的数据,并可以同时通过数据输出接口td1a和td2a来输出数据至上层输入接口urd1和urd3。

43.此外,在图4中,传输系统20还可包括管理控制电路mc1,管理控制电路mc1可以在下层传输电路200a、200b和上层传输电路uc1之间将控制信号和时钟脉冲信号传送到对应的传输电路。在有些实施例中,管理控制电路mc1和下层传输电路200a和200b可以设置在相同的芯片上,并且可以共同视为多物理层的电路结构cs1。

44.举例来说,管理控制电路mc1可以耦合至上层输出控制接口utctl1、上层输出时钟脉冲接口utclk1、上层输入控制接口urctl1、上层输入时钟脉冲接口urclk1以及下层传输电路200a和200b。也就是说,管理控制电路mc1可以根据传输的需求,使得下层传输电路200a、200b和上层传输电路uc1能够各自接收或传送对应的控制信号时钟脉冲信号。通过管理控制电路mc1,就可以进一步简化上层传输电路uc1与下层传输电路200a和200b之间的走线,使得传输系统20的设计更加弹性。

45.综上所述,本发明的实施例所提供的传输电路和传输系统可以包括利用串行信号和并行信号的转换器,因此可以允许传输电路在利用简化千兆媒体独立接口进行电路之间的数据传输时,弹性地使用一至三个数据输入接口和一至三个数据输出接口来传输数据。如此一来,就可以简化传输电路的设计以及彼此之间的走线,进而减少整体所需要的电路面积。

46.以上所述仅为本发明的较佳实施例,对本发明所做的等同变化和修改,都应属于本发明所涵盖范围。

47.附图标记说明

48.100、200、tc1:传输电路

49.110、150、210、250:串并转换器

50.120:接口译码器

51.130、170、230、270:并串转换器

52.140、240:处理单元

53.160:接口编码器

54.dr1、dt1:数据信号

55.pdr1、pdt1:并行信号组

56.pddr1:译码数据信号组

57.di1:输入数据信号

58.pedt1:编码数据信号组

59.do1:输出数据信号

60.rd1、rd2、rd1a、rd1b、rd1c、rd1d、rd2a、rd2b:数据输入接口

61.rctl1、rctla、rctlb、rctlc、rctld:输入控制接口

62.rclk1、rclka、rclkb、rclkc、rclkd:输入时钟脉冲接口

63.td1、td2、td1a、td1b、td1c、td1d、td2a、td2b:数据输出接口

64.tctl1、tctla、tctlb、tctlc、tctld:输出控制接口

65.tclk1、tclka、tclkb、tclkc、tclkd:输出时钟脉冲接口

66.10、20:传输系统

67.100a、100b、100c、100d、200a、200b:下层传输电路

68.uc1:上层传输电路

69.urd1、urd2、urd3、urd4:上层输入接口

70.urctl1:上层输入控制接口

71.urclk1:上层输入时钟脉冲接口

72.utd1、utd2、utd3、utd4:上层输出接口

73.utctl1:上层输出控制接口

74.utclk1:上层输出时钟脉冲接口