一种封装模块、封装方法及电子设备与流程

1.本发明涉及电子设备技术领域,尤其是涉及一种封装模块、封装方法及电子设备。

背景技术:

2.随着电子产品向小型化、轻薄化的方向发展,电子产品的封装技术不断演进。为了应对电子器件之间的电磁干扰(electromagnetic interference,emi),传统方法通过外加金属屏蔽罩来进行外部电磁屏蔽,然而,屏蔽罩需要占用设备空间,是设备小型化的一大障碍。

3.系统级封装(system in a package,sip)是将多种不同类型的芯片集成在一个封装内以实现高集成度要求。对于复杂的系统级封装,封装内部各电子器件之间也会相互干扰,因此在封装内部也需要进行电磁隔离。

4.现有技术中,通常是用激光在系统级封装的塑封体上开设沟槽,沟槽与设置于系统级封装电路板的露铜区域连接。用电磁屏蔽材料填充沟槽,电磁屏蔽材料与系统级封装表面的共形屏蔽层连接,隔离系统级封装内的电子器件。然而,通过激光开设的沟槽通常为倒梯形结构,该系统级封装的结构可靠性较低。此外,现有技术中通过激光开槽露出电路板的露铜区域,开槽深度较深,封装模块的单位小时产能(units per hour,uph)较低,亟需提升效率。

技术实现要素:

5.本技术实施例提供了一种封装模块、封装方法及电子设备,可以实现系统级封装模块内部各电子器件之间的电磁屏蔽以及封装模块和外部电子器件之间的电磁屏蔽,通过借助胶体形成靠近电路板的表面的宽度大于远离电路板的表面的宽度的空隙,减小了激光开槽深度或者不需要使用激光开槽,提高了作业uph和系统级封装模块的机械可靠性。同时,由于胶体部分不需要激光处理,因此在激光开槽时不会接触到露铜区域或者不需要使用激光开槽,可以保护电路板的露铜区域不被损坏。

6.第一方面,本技术提供一种封装模块,包括:第一电路板、第一塑封体、第二塑封体、电磁屏蔽体、电磁屏蔽层、第一电子器件和第二电子器件。第一塑封体、第二塑封体和电磁屏蔽体设置于第一电路板的第一表面。第一电路板的第一表面设置有第一露铜区域,第一露铜区域与第一电路板的地信号电连接,电磁屏蔽体的至少部分底面与第一露铜区域的至少一部分连接。电磁屏蔽体嵌设于第一塑封体和第二塑封体之间。电磁屏蔽层至少设置于第一塑封体的外表面、第二塑封体的外表面以及电磁屏蔽体的外表面。第一电子器件和第二电子器件设置于第一电路板的第一表面。第一塑封体覆盖第一电子器件,第二塑封体覆盖第二电子器件。电磁屏蔽体的第一截面包括第一边和第二边,第一边和电磁屏蔽层接触,第二边和电路板接触,第一边的长度不大于第二边的长度,第一截面所在的平面与电路板所在的平面垂直,第一截面所在的平面与电磁屏蔽体的长度延伸方向垂直。

7.在本技术中,第一露铜区域与第一电路板的地信号电连接,电磁屏蔽体从而通过

第一露铜区域与第一电路板的地信号电连接,电磁屏蔽层通过电磁屏蔽体与第一电路板的地信号电连接,从而实现封装模块内部第一电子器件与第二电子器件之间的电磁屏蔽,以及封装模块内部与封装模块外部电路的电磁屏蔽。电磁屏蔽体和电磁屏蔽层的接触宽度不大于电磁屏蔽体和电路板的接触宽度,优化了封装模块的应力分布,提升了封装模块的机械可靠性。

8.一种可能的实现方式中,第一边的长度不大于1mm。相对现有技术,减小了电磁屏蔽体与电磁屏蔽层的接触宽度,可以减小电磁屏蔽体所受的应力,从而提高封装模块的机械可靠性。此外,由于电磁屏蔽层设置于塑封材料的表面,降低了封装模块的整体高度,减轻了封装模块的重量。

9.一种可能的实现方式中,第一塑封体和第二塑封体的组分至少不溶于水或不溶于酸碱性溶液。第一塑封体和第二塑封体的组分可以包括环氧树脂等。第一塑封体和第二塑封体的组分可以是至少不溶于水或不溶于酸碱性溶液的环氧树脂。

10.一种可能的实现方式中,电磁屏蔽体和电磁屏蔽层的组分包括导电材料。其中,导电材料至少包括铝、铜、金或银中的一种或多种。通过使用导电性良好的金属材料,可以提高电磁屏蔽效果。

11.一种可能的实现方式中,第一电子器件和第二电子器件至少包括射频电路、功率放大电路、基带电路、音频电路、存储器电路中的一种或多种,第一电子器件和第二电子器件不同。第一电子器件和第二电子器件可以是不同功能电路的电子器件,例如,第一电子器件是射频电路的电子器件,第二电子器件为音频电路的电子器件;或者第一电子器件为基带电路的电子器件,第二电子器件为功率放大电路的电子器件。第一电子器件和第二电子器件也可以是不同工作频段的射频电路的电子器件,例如,第一电子器件为蓝牙电路的电子器件,第二电子器件为工作频率与蓝牙电路不同的射频电路的电子器件。为了避免两个电子器件之间的电磁干扰,将不同的两个电子器件分别设置在不同的电磁屏蔽腔,屏蔽了第一电子器件和第二电子器件之间的电磁干扰。例如,第一电子器件设置于电磁屏蔽体和设置于第一塑封体的外表面的电磁屏蔽层围设的电磁屏蔽腔,第二电子器件设置于电磁屏蔽体和设置于第二塑封体的外表面的电磁屏蔽层围设的电磁屏蔽腔。

12.在本实现方式中,不同功能和不同尺寸的电子器件可应用于封装模块中。

13.一种可能的实现方式中,第一露铜区域与第一电子器件之间设置有间隙,电磁屏蔽体与第一电子器件之间设置有间隙,第一露铜区域与第二电子器件之间设置有间隙,电磁屏蔽体与第二电子器件之间设置有间隙,从而保证电子器件不和电路板的地信号短路。

14.一种可能的实现方式中,第一电路板的至少部分侧面与电磁屏蔽层的至少一部分连接。使得第一电子器件设置于电磁屏蔽体和设置于第一塑封体外表面的电磁屏蔽层以及第一电路板的至少部分侧面围设的电磁屏蔽腔,第二电子器件设置于电磁屏蔽体和设置于第二塑封体外表面的电磁屏蔽层以及第一电路板的至少部分侧面围设的电磁屏蔽腔。进一步提高了两个电磁屏蔽腔体的屏蔽性能。

15.一种可能的实现方式中,电磁屏蔽体与第一露铜区域连接,电磁屏蔽体进而通过第一露铜区域与第一电路板的地信号电连接。

16.一种可能的实现方式中,电磁屏蔽体和设置于第一塑封体外表面的电磁屏蔽层围设成第一屏蔽腔,第一电子器件位于第一屏蔽腔。电磁屏蔽体和设置于第二塑封体外表面

的电磁屏蔽层围设成第二屏蔽腔,第二电子器件位于第二屏蔽腔。电磁屏蔽层通过电磁屏蔽体与第一电路板电导通,从而实现封装模块的电磁屏蔽。电磁屏蔽层和电磁屏蔽体共同实现第一电子器件和第二电子器件之间的电磁屏蔽,以及封装模块和外部电子器件之间的电磁屏蔽。

17.一种可能的实现方式中,电磁屏蔽体至少包括第一侧面,第一侧面位于封装模块的侧面,第一侧面与电磁屏蔽层连接,电磁屏蔽体的至少一个侧面位于系统级封装模块的边沿位置,电磁屏蔽体和封装模块的边沿共同将一个电子器件围设在内;或者,电磁屏蔽体为环形结构,一个电子器件被围设于环形内。

18.在本实现方式中,可根据电子器件的位置,利用封装模块的边沿规划尽量短的接地路径,在使得电磁屏蔽体起到较佳的电磁屏蔽效果的同时,尽量减小封装模块的尺寸,节省材料和工艺成本。

19.第二方面,本技术提供一种封装方法,包括:在设置于第一电路板的第一露铜区域点胶,形成胶体。第一电路板的第一表面还设置有第一电子器件和第二电子器件,第一露铜区域与第一电路板的地信号电连接,第一露铜区域位于第一电子器件和第二电子器件之间。第一露铜区域与第一电子器件之间设置有间隙,第一露铜区域与第二电子器件之间设置有间隙;胶体与第一电子器件之间设置有间隙,胶体与第二电子器件之间设置有间隙。在第一电路板的第一表面形成塑封体,塑封体覆盖第一电子器件、第二电子器件、以及至少部分胶体。去除胶体得到空隙,空隙将塑封体分隔得到第一塑封体第二塑封体。向空隙内填充导电材料,导电材料形成电磁屏蔽体,电磁屏蔽体的至少部分底面与第一露铜区域的至少一部分连接,电磁屏蔽体与第一电子器件之间设置有间隙,电磁屏蔽体与第二电子器件之间设置有间隙。在第一塑封体的至少部分外表面、第二塑封体的至少部分外表面和电磁屏蔽体的至少部分外表面设置电磁屏蔽层。电磁屏蔽体的第一截面包括第一边和第二边,第一边和电磁屏蔽层接触,第二边和电路板接触,第一边的长度不大于第二边的长度,第一截面所在的平面与电路板所在的平面垂直,第一截面所在的平面与电磁屏蔽体的长度延伸方向垂直。

20.在本技术中,第一露铜区域与第一电路板的地信号电连接,电磁屏蔽体从而通过第一露铜区域与第一电路板的地信号电连接,电磁屏蔽层通过电磁屏蔽体与第一电路板的地信号电连接,从而实现封装模块内部第一电子器件与第二电子器件之间的电磁屏蔽,以及封装模块内部与封装模块外部电路的电磁屏蔽。通过点胶、去除胶体形成空隙,在空隙处形成电磁屏蔽体,使得电磁屏蔽体与电磁屏蔽层的接触宽度不大于电磁屏蔽体与电路板的接触宽度,优化了封装模块的应力分布。由于通过点胶以及去除胶体形成空隙,在空隙处形成电子屏蔽体,胶体部分不需要通过激光处理,相对于现有技术,提升了封装模块的产能,以及封装模块的机械可靠性。

21.一种可能的实现方式中,当胶体比塑封体高时,洗掉至少部分胶体后得到空隙,其中,洗掉至少部分胶体包括:通过水或酸碱性溶液中的一种或多种洗掉至少部分胶体。采用水洗方式得到空隙,相对于现有技术通过激光开槽,提升了封装模块的产能以及生产效率。

22.一种可能的实现方式中,当胶体比塑封体低时,首先去除塑封体的部分塑封材料,露出至少部分胶体。然后洗掉至少部分胶体,得到第一空隙,空隙包括第一空隙。其中,洗掉至少部分胶体包括:通过水或酸碱性溶液中的一种或多种洗掉至少部分胶体。

23.由于胶体部分没有塑封材料,可以采用水洗或酸碱性溶液去除,相对现有技术通过激光开槽,提升了封装模块的产能以及生产效率。

24.一种可能的实现方式中,当胶体比塑封体低时,去除塑封体的部分塑封材料,包括通过激光或者研磨方式去除塑封体的部分塑封材料。当通过激光去除塑封体的部分塑封材料时,通过激光去除塑封体的部分塑封材料得到第二空隙,空隙为第一空隙和第二空隙的组合。当通过研磨去除塑封体的部分塑封材料时,空隙为第一空隙。当通过激光加研磨方式去除塑封体的部分塑封材料时,通过激光去除塑封体的部分塑封材料得到第二空隙,空隙为第一空隙和第二空隙的组合。

25.在本实现方式中,通过借助胶体形成空隙,胶体部分不需要激光处理;相对现有技术,减小了激光开槽深度或者不需要使用激光开槽,提高了作业uph和系统级封装模块的机械可靠性。同时,由于胶体的保护,在激光开槽时不会接触到露铜区域或者不需要使用激光开槽,可以保护露铜区域不被损坏。

26.一种可能的实现方式中,胶体的组分至少溶于水或溶于酸碱性溶液。胶体的组分可以包括环氧树脂等。

27.一种可能的实现方式中,第一边的长度不大于1mm。通过减小第一边的长度,可以减小电磁屏蔽体所受的应力,从而提高封装模块的可靠性。

28.一种可能的实现方式中,第一塑封体和第二塑封体的组分至少不溶于水或不溶于酸碱性溶液。第一塑封体和第二塑封体的组分可以包括环氧树脂等

29.一种可能的实现方式中,电磁屏蔽体和电磁屏蔽层的组分包括导电材料。其中,导电材料至少包括铝、铜、金或银中的一种或多种,通过使用导电性良好的金属材料,可以提高电磁屏蔽效果。

30.一种可能的实现方式中,第一电子器件和第二电子器件至少包括射频电路、功率放大电路、基带电路、音频电路、存储器电路中的一种或多种,第一电子器件和第二电子器件不同。第一电子器件和第二电子器件可以是不同功能电路的电子器件,例如,第一电子器件是射频电路的电子器件,第二电子器件为音频电路的电子器件;或者第一电子器件为基带电路的电子器件,第二电子器件为功率放大电路的电子器件。第一电子器件和第二电子器件也可以是不同工作频段的射频电路的电子器件,例如,第一电子器件为蓝牙电路的电子器件,第二电子器件为工作频率与蓝牙电路不同的射频电路的电子器件。为了避免两个电子器件之间的电磁干扰,将不同的两个电子器件分别设置在不同的电磁屏蔽腔,屏蔽了第一电子器件和第二电子器件之间的电磁干扰。例如,第一电子器件设置于电磁屏蔽体和设置于第一塑封体的外表面的电磁屏蔽层围设的电磁屏蔽腔,第二电子器件设置于电磁屏蔽体和设置于第二塑封体的外表面的电磁屏蔽层围设的电磁屏蔽腔。

31.在本实现方式中,不同功能和不同尺寸的电子器件可应用于封装模块中。

32.一种可能的实现方式中,第一电路板的至少部分侧面与电磁屏蔽层的至少一部分连接。使得第一电子器件设置于电磁屏蔽体和设置于第一塑封体外表面的电磁屏蔽层以及第一电路板的至少部分侧面围设的电磁屏蔽腔,第二电子器件设置于电磁屏蔽体和设置于第二塑封体外表面的电磁屏蔽层以及第一电路板的至少部分侧面围设的电磁屏蔽腔。进一步提高了两个电磁屏蔽腔体的屏蔽性能。

33.一种可能的实现方式中,电磁屏蔽体与第一露铜区域电连接,电磁屏蔽体进而通

过第一露铜区域与第一电路板的地信号电连接。

34.一种可能的实现方式中,电磁屏蔽体和设置于第一塑封体外表面的电磁屏蔽层围设成第一屏蔽腔,第一电子器件位于第一屏蔽腔。电磁屏蔽体和设置于第二塑封体外表面的电磁屏蔽层围设成第二屏蔽腔,第二电子器件位于第二屏蔽腔。电磁屏蔽层通过电磁屏蔽体与第一电路板电导通,从而实现封装模块的电磁屏蔽。电磁屏蔽层和电磁屏蔽体共同实现第一电子器件和第二电子器件之间的电磁屏蔽,以及封装模块和外部电子器件之间的电磁屏蔽。

35.一种可能的实现方式中,电磁屏蔽体至少包括第一侧面,第一侧面位于封装模块的侧面,第一侧面与电磁屏蔽层连接,电磁屏蔽体的至少一个侧面位于系统级封装模块的边沿位置,电磁屏蔽体和封装模块的边沿共同将一个电子器件围设在内;或者,电磁屏蔽体为环形结构,一个电子器件被围设于环形内。

36.在本实现方式中,可根据电子器件的位置,利用封装模块的边沿规划尽量短的接地路径,在使得电磁屏蔽体起到较佳的电磁屏蔽效果的同时,尽量减小封装模块的尺寸,节省材料和工艺成本。

37.第三方面,本技术提供一种电子设备,包括:第二电路板。第二电路板上设置有如前述第一方面及其可能的实现方式中提供的封装模块。由于封装模块的电磁屏蔽层设置于塑封材料的表面,降低了封装模块的整体高度,节省了电子设备的空间,优化了电子设备的空间利用率,有助于电子设备的轻薄化。

38.一种可能的实现方式中,第二电路板还设置有第三电子器件和金属屏蔽罩,金属屏蔽罩罩设第三电子器件。该封装模块可以实现封装模块内部电子器件之间的电磁屏蔽,也可以实现封装模块与第三电子器件之间的电磁屏蔽。此外,电磁屏蔽层设置于封装模块的外表面,占用的空间较小,比使用金属屏蔽罩节省了设计空间。

附图说明

39.为了更清楚地说明本技术具体实施方式的技术方案,下面将对具体实施方式中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本技术的一些实施方式,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

40.图1是本技术实施例提供的一种电路板结构示意图;

41.图2是图1所示的电路板沿a-a方向的剖视结构示意图;

42.图3是本技术实施例提供的一种系统级封装模块的结构示意图;

43.图4是本技术实施例提供的一种封装整板的结构示意图;

44.图5是本技术实施例提供的一种系统级封装模块的实现流程图;

45.图6a是本技术实施例提供的一种在整板上点胶后的单板结构图;

46.图6b是本技术实施例提供的一种在整板上塑封后的单板结构图;

47.图6c是本技术实施例提供的一种在整板上开槽后的单板结构图;

48.图6d是本技术实施例提供的一种在整板上研磨后的单板结构图;

49.图6e是本技术实施例提供的一种在整板上去除胶体后的单板结构图;

50.图6f是本技术实施例提供的另一种在整板上去除胶体后的单板结构图;

51.图6g是本技术实施例提供的一种在整板上填充屏蔽材料后的单板结构图;

52.图6h是本技术实施例提供的一种对整板分板后的单模块结构图;

53.图7a是本技术实施例提供的另一种在整板上塑封后的单板结构图;

54.图7b是本技术实施例提供的另一种在整板上去除胶体后的单板结构图;

55.图8是本技术实施例提供的一种系统级封装模块的俯视示意图;

56.图9是本技术实施例提供的另一种系统级封装模块的俯视示意图;

57.图10是本技术实施例提供的另一种系统级封装模块的俯视示意图。

具体实施方式

58.为了更加清楚说明本技术实施例的方案,下面将结合附图对本技术实施例作进一步的详细描述。

59.其中,在本技术实施例的描述中,除非另有说明,“/”表示或的意思,例如,a/b可以表示a或b;本文中的“和/或”仅仅是一种描述关联对象的关联关系,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b这三种情况。

60.以下,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本技术实施例的描述中,除非另有说明,“多个”的含义是两个或两个以上。

61.下面对本技术中涉及到的基本概念进行解释说明。需要说明的是,这些解释是为了让本技术实施例更容易被理解,而不应该视为对本技术实施例所要求的保护范围的限定。

62.共形屏蔽(conformal shielding):在塑封体的表面形成电磁屏蔽,将屏蔽层和塑封体融合在一起,实现整个塑封模块的屏蔽;

63.分腔屏蔽(compartment shielding):在塑封体的内部通过电磁屏蔽材料进行隔离,实现塑封体内部各腔体之间的屏蔽;

64.系统级封装(system in package,sip):将多种功能芯片和元器件集成在一个封装内,从而实现一个完整的功能。与片上系统(system on chip,soc)相对应,不同的是系统级封装是采用不同芯片进行并排或叠加的封装方式,而片上系统则是高度集成的芯片产品;

65.电磁干扰(electromagnetic interference,emi):电子产品工作会对周边的其他电子产品造成干扰,电磁干扰种类有传导干扰和辐射干扰。

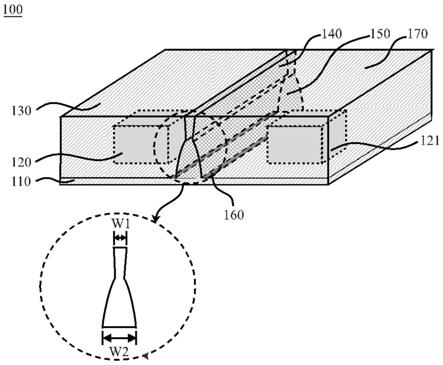

66.图1是本技术实施例提供的一种电路板结构示意图。

67.如图1所示,电路板300上设置有系统级封装模块100和金属屏蔽罩400。系统级封装模块100包括电磁屏蔽层170,系统级封装模块100通过电磁屏蔽层170实现屏蔽,电磁屏蔽层170隔离了系统级封装模块100与外部电路的电磁干扰。

68.图2为图1所示的电路板沿a-a方向的剖视结构示意图。

69.电路板300还设置有电子器件200,金属屏蔽罩400罩设电子器件200。

70.如图2所示,电磁屏蔽层170设置于系统级封装模块100的外表面,电磁屏蔽层170占用的空间较小。屏蔽罩400和电子器件200之间存在间隙,比系统级封装模块100占用更多

的设计空间。

71.为了便于描述,本实施例以系统级封装模块100、电子器件200和金属屏蔽罩400的数量均为1个为例,进行示意性说明。系统级封装模块100、电子器件200和金属屏蔽罩400的数量也可以是多个。本技术对系统级封装模块、电子器件以及金属屏蔽罩的数量不做限定。

72.系统级封装模块100可以包括射频功率放大电路、蓝牙电路、wi-fi电路、音频电路、存储器电路、电源电路等,电子器件200可以包括射频、蓝牙、导航等电路。

73.图3是本技术实施例提供的一种系统级封装模块的结构示意图。如图3所示,本技术实施例提供的系统级封装模块100,包括:载板110、电子器件120和电子器件121、塑封体130、槽体140、电磁屏蔽体150、露铜区域160和电磁屏蔽层170。

74.电子器件120和电子器件121设置于载板110的第一表面,例如,电子器件120和电子器件121焊接于载板110的第一表面。

75.槽体140设置于电子器件120和电子器件121之间。槽体140的至少部分底面与露铜区域160的至少一部分连接。

76.塑封体130覆盖载板110的第一表面的至少一部分,塑封体130还覆盖电子器件120和电子器件121。槽体140中填充电磁屏蔽材料形成电磁屏蔽体150。塑封体130的外表面设置有电磁屏蔽层170。电磁屏蔽层170与电磁屏蔽体150连接,且电磁屏蔽层170通过电磁屏蔽体150与载板110上的露铜区域160连接,电磁屏蔽层170进而与载板110的地信号电连接,从而实现系统级封装模块100的上下电导通。电磁屏蔽层170和电磁屏蔽体150共同实现系统级封装模块100内部电子器件120和电子器件121之间的分腔屏蔽,以及系统级封装模块100和电子器件200之间的共形屏蔽。

77.槽体140的横截面远离载板110的宽度为第一宽度w1,槽体140的横截面靠近载板110的宽度为第二宽度w2,第一宽度w1不大于第二宽度w2。

78.为了便于理解上述系统级封装模块的结构,结合附图对本技术提供的系统级封装模块的实现方案进行详细说明。

79.图4示意了一种封装整板的结构示意图。

80.整板500上分布有呈矩阵分布的多个单板。由于多个单板的结构相同,处理步骤相同。为了清楚地描述,以位于整板的单板510为例,示例性说明。

81.如图4所示,单板510的载板110上设置有用于设置电子器件的焊点,电子器件可以包括电子器件120和电子器件121。载板110上可以设置有更多个电子器件。为了便于说明,本技术实施例以载板上设置有两个电子器件(电子器件120和电子器件121)进行示例性说明。本技术实施例对设置于载板的电子器件的数量不做限定。

82.其中,载板110一般为印刷电路板(printed circuit board,pcb)。示例性地,载板110的厚度大约为0.4mm,载板可以采用叠层板材结构。需要说明的是,载板的类型、厚度和结构的示例性说明是为了让本技术实施例更容易被理解,而不应该视为对本技术实施例所要求的保护范围的限定。

83.电子器件120和/或电子器件121可以是射频功率放大电路、存储器、蓝牙电路、wi-fi电路、音频电路等。电子器件120和电子器件121可以分别属于不同功能电路的器件,例如,电子器件120属于基带电路的器件,电子器件121为射频电路的器件。电子器件120和电子器件121也可以是相同功能电路的不同频段模块的器件,例如,电子器件120可以是3g射

频电路的器件,电子器件121为4g射频电路的器件。

84.示例性地,电子器件120和/或电子器件121的高度可以为0.3~1.3mm。

85.载板110上还设置有露铜区域160。露铜区域160与载板110的地信号电连接。露铜区域160设置于电子器件120和电子器件121之间。露铜区域160可以为设置于载板110的接地铜箔。此外,露铜区域160与电子器件120和电子器件121之间保持一定间隙,防止电子器件与露铜区域160短路。示例性地,露铜区域的宽度可以为0.1mm,露铜区域与电子器件之间的距离可以为0.25mm。

86.图5是本技术实施例提供的一种系统级封装模块的实现流程图,图6a-图6h为图5中步骤s101-步骤s106对应的实施方式的单板结构示意图。

87.s101:在设置于载板110的露铜区域160上点胶,形成胶体180。

88.示例性地,胶体的材料可以是可溶于水或酸碱性溶液的环氧树脂,比如水溶胶。

89.图6a示意一种在整板上点胶后的单板结构图。

90.如图6a所示,胶体180的长度延伸方向可以和露铜区域160的长度延伸方向相同。胶体180的至少部分底面与露铜区域160的至少一部分连接。胶体180的高度可以比电子器件120或电子器件121中的至少任一个器件高。胶体180的高度也可以比电子器件120或电子器件121中的至少任一个器件低。其中,胶体180的横截面靠近载板110的宽度大于远离载板110的宽度。

91.示例性地,露铜区域160的宽度可以为0.1mm,胶体180的下表面宽度可以为0.08-0.12mm,胶体180底部与电子器件之间的距离可以为0.25mm。需要说明的是,焊盘的宽度、胶体的宽度以及胶体与电子器件之间的距离的示例性说明是为了让本技术实施例更容易被理解,而不应该视为对本技术实施例所要求的保护范围的限定。

92.s102:在载板110的上表面通过塑封工艺形成塑封体130。

93.图6b示意一种在整板上塑封后的单板结构图。

94.塑封体130可以将胶体180以及载板110上设置的包括电子器件120和电子器件121的至少两个电子器件覆盖在塑封体130内。塑封体130的高度大于电子器件120和电子器件121的高度。塑封体130的高度可以大于胶体180的高度。

95.示例性地,塑封体130的形状可以是长方体、半球形或其他不规则立体形状等。塑封体130的高度可以是0.4-1.4mm,塑封体130可以比最高的电子器件高0.1mm。塑封体130可以覆盖载板110的第一表面的全部。塑封体130也可以覆盖载板110的第一表面的一部分,并与载板110上的露铜区域连接。

96.塑封体130不仅可以起到保护电子器件的作用,还可以提高系统级封装模块100的散热性能。示例性地,塑封体130的材质可以是不可溶于水,不可溶于酸碱性溶液的环氧树脂等。

97.s103:去除塑封体130的部分塑封材料,露出胶体180。

98.在一种可能的实施方式中,当胶体180比电子器件低时,可以通过激光开槽方式对塑封体130进行处理,去除塑封体130的部分塑封材料,形成激光槽141,露出至少部分胶体180。

99.图6c示意一种在整板上开槽后的单板结构图。

100.如图6c所示,激光槽141位于至少部分胶体180上方,激光槽141使至少部分胶体

180与外部空间连通。其中,激光开槽时激光在塑封体130内会发生折射和散射,塑封体130越靠近载板110的部分接触激光的时间越短,吸收的能量越少,被灼蚀的部分越少,因此形成的激光槽141的横截面形状可以为倒梯形。激光槽141的横截面的最大宽度为第一宽度w1,胶体180的横截面的最大宽度为第二宽度w2,第一宽度w1不大于第二宽度w2。激光槽141的开槽深度h1不大于塑封体130的高度h2。示例性地,激光槽141的横截面远离载板的表面宽度w1为0.2mm,靠近载板的表面宽度为0.15mm,开槽深度h1为0.5mm。激光槽141的长度延伸方向可以和胶体180的长度延伸方向相同,或激光槽141的长度延伸方向可以和露铜区域160的长度延伸方向相同。由于激光槽141的开槽深度h1小于塑封体130的高度h2,因此激光开槽过程中不会接触到露铜区域160,可以保护露铜区域160不被损坏。

101.在另一种可能的实施方式中,当胶体180比电子器件低时,可以先通过研磨方式降低塑封体130的高度。其中,研磨后塑封体130的高度大于电子器件的高度。然后,通过激光开槽方式对塑封体130进行处理,去除塑封体130的部分塑封材料,形成激光槽141,露出至少部分胶体180。

102.在另一种可能的实施方式中,当胶体180比电子器件高时,可以通过研磨方式降低塑封体130的高度,露出至少部分胶体180。

103.图6d示意一种在整板上研磨后的单板结构图。

104.如图6d所示,研磨露出至少部分胶体180后,胶体180顶部与塑封体130顶部平齐,至少部分胶体180与外部空间连通。由于不需要对塑封体130进行激光开槽处理,进一步降低了露铜区域160被损坏的风险。

105.在另一种可能的实施方式中,当胶体180的高度比电子器件高时,可以通过激光开槽方式对塑封体130进行处理,去除塑封体130的部分塑封材料,形成激光槽141,露出至少部分胶体180。

106.在另一种可能的实施方式中,当胶体180的高度比电子器件高时,也可以先通过研磨方式降低塑封体130的高度。其中,研磨后塑封体130的高度大于电子器件的高度。然后,通过激光开槽方式对塑封体130进行处理,去除塑封体130的部分塑封材料,形成激光槽141,露出至少部分胶体180。

107.s104:去除胶体180形成槽体140。其中,槽体140可以为空隙。

108.示例性地,胶体180的材料为可溶于水的环氧树脂时,可以采用高压水洗方式去除;或者,胶体180的材料为可溶于酸碱性溶液的环氧树脂时,可以采用有机溶液清洗方式去除。

109.在一种可能的实施方式中,激光槽141和去除胶体180形成的空槽142共同形成槽体140。

110.图6e示意一种在整板上去除胶体后的单板结构图。

111.如图6e所示,去除胶体180后,形成的空槽142和激光槽141连通,共同形成槽体140,槽体140的横截面远离载板的第一宽度w1不大于靠近载板的第二宽度w2。槽体140位于相邻的两个电子器件120和电子器件121之间,且贯穿塑封体130的上下表面。槽体140可以将系统级封装模块100分成多个腔体。露铜区域160与外部空间连通,且至少部分露铜区域160位于槽体140的底部。

112.在另一种可能的实施方式中,胶体180上方没有激光槽141,通过去除胶体180后直

接形成槽体140。

113.图6f示意另一种在整板上去除胶体后的单板结构图。

114.如图6f所示,去除胶体180后,直接形成槽体140,槽体140的横截面远离载板的第一宽度w1不大于靠近载板的第二宽度w2。槽体140位于相邻的两个电子器件120和电子器件121之间,且贯穿塑封体130的上下表面。槽体140可以将系统级封装模块100分成多个腔体。露铜区域160与外部空间连通,且露铜区域160位于槽体140的底部。

115.s105:在槽体140内填充电磁屏蔽材料,形成电磁屏蔽体150。

116.示例性地,电磁屏蔽材料可以是导电银浆或导电铜浆等。为了排除向槽体140内填充电磁屏蔽材料过程中形成的气泡。可以在填充屏蔽材料之后,放置在真空环境进行排气。之后放置于高温环境,使得导电银浆或导电铜浆固化。经过高温固化后,电磁屏蔽体150的体积缩小,使得电磁屏蔽体150固化后的高度小于塑封体130的高度。

117.图6g示意一种在整板上填充屏蔽材料后的单板结构图。

118.如图6g所示,电磁屏蔽体150与位于槽体140底部的露铜区域160连接,电磁屏蔽体150进而通过露铜区域160和载板的地信号连接。电磁屏蔽体150的至少部分底面与露铜区域160的至少一部分连接,并保证电磁屏蔽体150与露铜区域160接触良好。

119.对整板500上的多个单板510同时执行步骤s101-步骤s105,可以提高作业效率。

120.s106:对整板500进行分板,形成单模块520。

121.示例性地,可以采用激光分板或者铣刀分板等。

122.图6h示意一种对整板分板后的单模块结构图。

123.如图6h所示,对整板500进行分板后,形成单模块520。以其中一个单模块520为例,载板110的侧面设置有连接单板的地信号的导电层111,分板后导电层111暴露于载板110的侧面的外表面。示例性地,导电层的材料可以为金属,例如,铝、铜、金、银等。

124.s107:在单模块520的塑封体130的外表面形成一层电磁屏蔽层170,形成系统级封装模块100。

125.示例性地,可以采用喷涂机通过喷涂工艺在塑封体130的外表面形成电磁屏蔽层170;或者,采用磁控溅射设备通过溅射工艺在塑封体130的外表面形成电磁屏蔽层170。示例性地,电磁屏蔽层的材料可以为金属,例如,铝、铜、金、银等。电磁屏蔽层170的厚度为0.01mm。与现有的金属屏蔽罩相比,电磁屏蔽层170设置于塑封体130的外表面,减少了系统级封装模块100占用的设计空间。

126.如图3所示,电磁屏蔽层170覆盖载板110侧面的导电层,电磁屏蔽层170与该导电层、电磁屏蔽体150以及露铜区域160连通,将电子器件120和电子器件121围设在不同的电磁屏蔽腔内,可以隔离系统级封装模块100内部电子器件120和电子器件121之间的电磁干扰,并隔离系统级封装模块100和电子器件200之间的电磁干扰。

127.在一种实施方式中,通过上述步骤s101形成的胶体180的高度比电子器件120和电子器件121的高度高。通过上述步骤s102形成的塑封体的高度可以比胶体180的高度低,且塑封体的高度大于电子器件120和电子器件121的高度。

128.图7a示意另一种在整板上塑封后的单板结构图。

129.如图7a所示,塑封体130位于载板上且覆盖载板的第一表面的至少一部分,至少两个电子器件120和电子器件121被包裹在塑封体130内,胶体180未被完全包裹在塑封体130

内。胶体180的高度大于塑封体130的高度,塑封体130的高度大于电子器件的高度。

130.图7b示意另一种在整板上去除胶体后的单板结构图。

131.如图7b所示,直接去除胶体180,形成槽体140。由于胶体180的高度比塑封体130的高度高,不需要对塑封体130进行研磨或激光开槽处理,从而降低了露铜区域160被损坏的概率。

132.图8是本技术实施例提供的一种系统级封装模块的俯视示意图,图9和图10是本技术实施例提供的另一种系统级封装模块的俯视示意图。参考图8、图9和图10所示,槽体140的形状和数量存在多种可能,与系统级封装模块中需要屏蔽的电子器件的形状、数量有关。槽体140的至少一个侧面位于系统级封装模块的边沿位置;或者,槽体140为环形凹槽,电子器件位于环形凹槽内。槽体140贯穿塑封体130的上下表面且位于相邻电子器件之间,起到分隔相邻电子器件的作用。

133.如图8所示,槽体可以呈直线型,直线型槽体140和系统级封装模块的边缘共同将相邻电子器件120和电子器件121分隔开,降低它们之间的电磁干扰。

134.如图9所示,槽体可以呈t型,槽体140和系统级封装模块的边缘共同将电子器件120、电子器件121和电子器件122分隔开,降低它们之间的电磁干扰。

135.如图10所示,槽体可以呈环型,槽体140将电子器件121围设在内,从而将电子器件120和电子器件121分隔开,降低它们之间的电磁干扰。

136.此外,一个系统级封装模块内一般分布着多个电子器件,且电子器件的尺寸和位置不同,为了使槽体140可以起到较佳的隔断作用,同时尽量减小系统级封装模块的整体尺寸,在设置槽体140的形状时,应当根据电子器件的位置,利用系统级封装模块的边缘,规划出较短的槽体路线,以节省材料和工艺成本。

137.本实施例提供的系统级封装模块的分腔屏蔽接地方法,通过借助胶体形成靠近载板的表面的宽度大于远离载板的表面的宽度的槽体结构,减小了激光开槽深度或者不需要使用激光开槽,提高了作业uph和系统级封装模块的机械可靠性。同时,由于胶体部分不需要激光处理,因此在激光开槽时不会接触到露铜区域或者不需要使用激光开槽,可以保护露铜区域不被损坏。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1