[0001]

本发明属于位移编码器技术领域,涉及一种插值系统,尤其涉及一种基于二阶跟踪环的插值系统及方法。

背景技术:[0002]

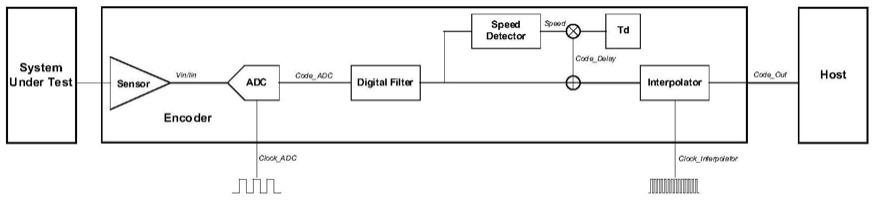

在角度或者线性位移编码器中,通常输出的位移和角度信号需要比采样adc输出信号更高的更新速度(插值),并且需要在匀速情况下实现零延时输入输出特性(也就是需要补偿编码器内部模块产生的延时),传统的插值以及延时补偿的算法结构如图1所示。

[0003]

被测系统(systemundertest)的被测量信号(磁场,电场,光强等)被编码器(encoder)中的传感器(sensor)转换为模拟电信号(电压或者电流:vin/iin),再被编码器中的模数转换器(adc)以一个频率较低的时钟(clock_adc)采样并转换成数字信号(code_adc)。通常为了滤除sensor和adc中的噪声,需要一个数字滤波器(digitalfilter)接在adc之后。然后,为达到测量控制器(host)要求的更高的数据刷新率,需要一个工作在更快的时钟(clock_interpolator)频率下的插值器(interpolator)来将低速的模数转换器和数字滤波器的输出信号(code_adc)插值到高速的编码器输出信号code_out.

[0004]

另外,在某些应用中,对于匀速变化的信号(例如匀速转动的角度信号),系统希望得到一个零延时的输出,此时就需要对系统中的传感器,模数转换器,数字滤波器以及插值器产生的信号延时来进行补偿,补偿的办法是先由速度探测模块(speeddetector)来计算出匀速信号的速度(图1中的speed),再将速度信号和要补偿的时间td相乘来得到延时补偿code(code_delay),最后将补偿code加到输出信号中来实现延时补偿。

[0005]

以上所述传统插值系统结构有如下两个缺点:

[0006]

(1)数字滤波器和插值器串联结构,系统复杂度较高;

[0007]

(2)延时补偿模块中的速度探测模块,对于信号中包含的噪声(特别是高频噪声)很敏感,输入信号中的噪声会被速度探测模块放大到速度信号中去,从而降低了系统的噪声性能。

[0008]

普通跟踪环的典型结构如图2所示,其输入为code_adc,输出为code_out,跟踪环将code_out与code_adc相减后得到的输入输出误差信号code_error输入由两个积分器和一路与第一个积分器并联的等比例通路形成的环路滤波器,并将环路滤波器的输出作为跟踪环的输出信号code_out。

[0009]

由于两个积分器在频率为零时的增益为无穷大,所以在输入信号为不变信号或者为匀速信号时,跟踪环总是随着时间的增加趋于将code_error抑制为零。另一方面,由于第二个积分器的输入信号(如图2中的code_velocity)是输出信号对时间的导数,所以其大小也就与输出信号的速度成正比。

[0010]

有鉴于此,如今迫切需要设计一种新的插值系统,以便克服现有插值系统存在的上述至少部分缺陷。

技术实现要素:[0011]

本发明提供一种基于二阶跟踪环的插值系统及方法,可降低系统的复杂度,降低成本。

[0012]

为解决上述技术问题,根据本发明的一个方面,采用如下技术方案:

[0013]

一种基于二阶跟踪环的插值系统,所述插值系统包括:第一积分器、第二积分器、第一加法器、第二加法器、第一插值器、第二插值器、第一乘法器ki、第二乘法器kp及延时电路;

[0014]

所述第一加法器的第一输入端连接输入信号,第一加法器的第二输入端连接延时电路的输出端,第一加法器的输出端分别连接第一乘法器ki的输入端、第二乘法器kp的输入端;

[0015]

第一乘法器ki的输出端连接第一积分器的输入端,第一积分器的输出端连接第二加法器的第一输入端;第二乘法器kp的输出端连接第二加法器的第二输入端,第二加法器的输出端连接第一插值器的输入端;

[0016]

所述第一插值器的输出端连接第二积分器的输入端,第二积分器的输出端还连接第二插值器的输入端,第二插值器的输出端连接延时电路的输入端。

[0017]

作为本发明的一种实施方式,所述第一加法器接收输入信号及系统输出信号,并获取两者的误差值,将误差值分别输送至第一乘法器ki及第二乘法器kp;

[0018]

所述第一乘法器ki将误差值乘以ki后输送至第一积分器做积分,第二乘法器kp将误差值乘以kp;所述第一积分器输出的信号及第二乘法器kp输出的信号通过第二加法器相加,并将相加后的结果输送至第一插值器;

[0019]

所述第一插值器经过处理后将数据输送至第二积分器积分,第二积分器输出的信号作为系统输出信号;所述第二插值器接收所述系统输出信号,经过处理后输送至延时电路,经过延时电路延时后输送至所述第一加法器。

[0020]

作为本发明的一种实施方式,所述插值系统还包括除法器;所述第二加法器的输出端连接除法器的输入端,除法器的输出端连接第一插值器的输入端。

[0021]

作为本发明的一种实施方式,第二个积分器的工作频率被设置成比输入信号频率或者第一个积分器工作频率乘以n倍,这里n等于输出信号或者第一个积分器工作频率需要的插值的倍数。

[0022]

作为本发明的一种实施方式,在第一个积分器和等比例支路相加的加法器输出端得到了code_out的速度code_velocity,此时只需要将这个速度值除以n倍就可以得到在第二个积分器工作频率加快n倍后所需要的正确的输入值。所以在连续的两个code_velocity采样点的中间,使用前一个code_velocity值除以n倍来推算code_out插值数值:

[0023][0024]

而对于延时补偿功能,在反馈之路上加入一个延时单元来实现,利用跟踪环的闭环跟踪特性,迫使输出code_out超前延时td来使得反馈信号code_fb来跟踪上输入信号code_adc,从而实现了延时补偿。

[0025]

作为本发明的一种实施方式,所述第一插值器包括上采样器,用以提高采样速率。

[0026]

作为本发明的一种实施方式,所述第二插值器包括下采样器,用以降低采样率。

[0027]

根据本发明的另一个方面,采用如下技术方案:一种基于二阶跟踪环的插值方法,所述插值方法包括:

[0028]

第一加法器接收输入信号及系统输出信号,并获取两者的误差值,将误差值分别输送至第一乘法器ki及第二乘法器kp;

[0029]

所述第一乘法器ki将误差值乘以ki后输送至第一积分器做积分,第二乘法器kp将误差值乘以kp;所述第一积分器输出的信号及第二乘法器kp输出的信号通过第二加法器相加,并将相加后的结果输送至第一插值器;

[0030]

所述第一插值器经过处理后将数据输送至第二积分器积分,第二积分器输出的信号作为系统输出信号;所述第二插值器接收所述系统输出信号,经过处理后输送至延时电路,经过延时电路延时后输送至所述第一加法器。

[0031]

作为本发明的一种实施方式,第二个积分器的工作频率被设置成比输入信号频率或者第一个积分器工作频率乘以n倍,这里n等于输出信号或者第一个积分器工作频率需要的插值的倍数。

[0032]

在第一个积分器和等比例支路相加的加法器输出端得到了code_out的速度code_velocity,此时只需要将这个速度值除以n倍就可以得到在第二个积分器工作频率加快n倍后所需要的正确的输入值。所以在连续的两个code_velocity采样点的中间,使用前一个code_velocity值除以n倍来推算code_out插值数值:

[0033][0034]

而对于延时补偿功能,在反馈之路上加入一个延时单元来实现,利用跟踪环的闭环跟踪特性,迫使输出code_out超前延时td来使得反馈信号code_fb来跟踪上输入信号code_adc,从而实现了延时补偿。本发明与传统设计补偿延时的方法不同,本设计的延时补偿并不需要速度探测模块,所以也就避免了速度探测产生的噪声干扰问题。

[0035]

本发明的有益效果在于:本发明提出的基于二阶跟踪环的插值系统及方法,将跟踪环和插值器结合,代替传统设计中复杂的数字滤波器和插值器,可降低系统的复杂度,降低成本。此外,本发明在反馈支路上插入的延时模块,可以精准地控制延时补偿量,而不像传统设计的复杂延时补偿而又易受输入信号噪声影响。

附图说明

[0036]

图1为现有插值系统的组成示意图。

[0037]

图2为现有普通跟踪环的典型结构示意图。

[0038]

图3为本发明一实施例中插值系统的组成示意图。

[0039]

图4为本发明一实施例中插值数值的波动示意图。

具体实施方式

[0040]

下面结合附图详细说明本发明的优选实施例。

[0041]

为了进一步理解本发明,下面结合实施例对本发明优选实施方案进行描述,但是应当理解,这些描述只是为进一步说明本发明的特征和优点,而不是对本发明权利要求的限制。

[0042]

该部分的描述只针对几个典型的实施例,本发明并不仅局限于实施例描述的范围。相同或相近的现有技术手段与实施例中的一些技术特征进行相互替换也在本发明描述和保护的范围内。

[0043]

说明书中的“连接”既包含直接连接,也包含间接连接,如通过一些有源器件、无源器件或电传导媒介进行的连接;还可包括本领域技术人员公知的在可实现相同或相似功能目的的基础上通过其他有源器件或无源器件的连接,如通过开关、跟随电路等电路或部件的连接。

[0044]

本发明揭示了一种基于二阶跟踪环的插值系统,图3为本发明一实施例中插值系统的组成示意图;请参阅图3,所述插值系统包括:第一积分器1、第二积分器2、第一加法器3、第二加法器4、第一插值器5、第二插值器6、第一乘法器(ki)7、第二乘法器(kp)8及延时电路9。

[0045]

所述第一加法器3的第一输入端连接输入信号,第一加法器3的第二输入端连接延时电路9的输出端,第一加法器3的输出端分别连接第一乘法器7的输入端、第二乘法器8的输入端。第一乘法器7的输出端连接第一积分器1的输入端,第一积分器1的输出端连接第二加法器4的第一输入端;第二乘法器8的输出端连接第二加法器4的第二输入端,第二加法器4的输出端连接第一插值器5的输入端。所述第一插值器5的输出端连接第二积分器2的输入端,第二积分器2的输出端还连接第二插值器6的输入端,第二插值器6的输出端连接延时电路9的输入端。

[0046]

在本发明的一实施例中,所述第一加法器3接收输入信号及系统输出信号,并获取两者的误差值,将误差值分别输送至第一乘法器7及第二乘法器8。所述第一乘法器7将误差值乘以ki后输送至第一积分器1做积分,第二乘法器8将误差值乘以kp;所述第一积分器1输出的信号及第二乘法器8输出的信号通过第二加法器4相加,并将相加后的结果输送至第一插值器5。所述第一插值器5经过处理后将数据输送至第二积分器2积分,第二积分器2输出的信号作为系统输出信号;所述第二插值器6接收所述系统输出信号,经过处理后输送至延时电路9,经过延时电路9延时后输送至所述第一加法器3。

[0047]

请继续参阅图3,在本发明的一实施例中,所述插值系统还包括除法器10(也可以是乘法器);所述第二加法器4的输出端连接除法器10的输入端,除法器10的输出端连接第一插值器5的输入端。

[0048]

在一实施例中,第二个积分器的工作频率被设置成比输入信号频率或者第一个积分器工作频率乘以n倍,这里n等于输出信号或者第一个积分器工作频率需要的插值的倍数。

[0049]

在本发明的一实施例中,在第一个积分器和等比例支路相加的加法器输出端得到了code_out的速度code_velocity,此时只需要将这个速度值除以n倍就可以得到在第二个积分器工作频率加快n倍后所需要的正确的输入值。所以在连续的两个code_velocity采样点的中间,使用前一个code_velocity值除以n倍来推算code_out插值数值(可参阅图4):

[0050][0051]

而对于延时补偿功能,在反馈之路上加入一个延时单元来实现,利用跟踪环的闭环跟踪特性,迫使输出code_out超前延时td来使得反馈信号code_fb来跟踪上输入信号

code_adc,从而实现了延时补偿。

[0052]

本发明还揭示一种基于二阶跟踪环的插值方法,所述插值方法包括:

[0053]

第一加法器接收输入信号及系统输出信号,并获取两者的误差值,将误差值分别输送至第一乘法器ki及第二乘法器kp;

[0054]

第一乘法器ki将误差值乘以ki后输送至第一积分器做积分,第二乘法器kp将误差值乘以kp;所述第一积分器输出的信号及第二乘法器kp输出的信号通过第二加法器相加,并将相加后的结果输送至第一插值器;

[0055]

第一插值器经过处理后将数据输送至第二积分器积分,第二积分器输出的信号作为系统输出信号;第二插值器接收所述系统输出信号,经过处理后输送至延时电路,经过延时电路延时后输送至所述第一加法器。

[0056]

在本发明的一实施例中,第二个积分器的工作频率被设置成比输入信号频率或者第一个积分器工作频率乘以n倍,这里n等于输出信号或者第一个积分器工作频率需要的插值的倍数。

[0057]

在第一个积分器和等比例支路相加的加法器输出端得到了code_out的速度code_velocity,此时只需要将这个速度值除以n倍就可以得到在第二个积分器工作频率加快n倍后所需要的正确的输入值。所以在连续的两个code_velocity采样点的中间,使用前一个code_velocity值除以n倍来推算code_out插值数值(可参阅图4):

[0058][0059]

而对于延时补偿功能,在反馈之路上加入一个延时单元来实现,利用跟踪环的闭环跟踪特性,迫使输出code_out超前延时td来使得反馈信号code_fb来跟踪上输入信号code_adc,从而实现了延时补偿。本发明与传统设计补偿延时的方法不同,本设计的延时补偿并不需要速度探测模块,所以也就避免了速度探测产生的噪声干扰问题。

[0060]

综上所述,本发明提出的基于二阶跟踪环的插值系统及方法,将跟踪环和插值器结合,代替传统设计中复杂的数字滤波器和插值器,可降低系统的复杂度,降低成本。此外,本发明在反馈支路上插入的延时模块,可以精准地控制延时补偿量,而不像传统设计的复杂延时补偿而又易受输入信号噪声影响。

[0061]

以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

[0062]

这里本发明的描述和应用是说明性的,并非想将本发明的范围限制在上述实施例中。实施例中所涉及的效果或优点可因多种因素干扰而可能不能在实施例中体现,对于效果或优点的描述不用于对实施例进行限制。这里所披露的实施例的变形和改变是可能的,对于那些本领域的普通技术人员来说实施例的替换和等效的各种部件是公知的。本领域技术人员应该清楚的是,在不脱离本发明的精神或本质特征的情况下,本发明可以以其它形式、结构、布置、比例,以及用其它组件、材料和部件来实现。在不脱离本发明范围和精神的情况下,可以对这里所披露的实施例进行其它变形和改变。