输出级电路和AB类放大器的制作方法

输出级电路和ab类放大器

技术领域

1.本公开涉及集成电路技术领域,更具体地涉及一种输出级电路和ab类放大器。

背景技术:

2.放大器是能把输入信号的电压或功率放大的器件。ab类功率放大器(class ab)是依赖于偏置电流的大小和输出电平的a类和b类放大器的结合器件,可以使工作于推挽工作方式的两个晶体管的工作区间互有覆盖,弥补了a类放大器和b类放大器的缺点,所以ab类放大器具有效率高、失真较小、功放晶体管功耗较小、以及散热好等优点,成为目前放大器常用的类型。

3.通常,如果从各电路实现的功能来划分,传统的ab类放大器的输出级电路包括静态电流控制电路和输出端电路,静态电流控制电路用于控制输出端电路的静态电流的大小,并实现ab类的工作方式。

4.所述实现ab类的工作方式是指:在静态时具有较小的流经输出端电路的静态电流,以及在动态时能输出较大的电流至负载,并具有较高的输出效率、较小的交越失真。

5.现有的class ab运放的输出级电路中晶体管(一般选取金属氧化物半导体场效应晶体管(mos管))尺寸都不太大,因为如果增加输出级mos管尺寸,mos管的栅极寄生电容也会随之增加,这就会给运放的补偿增加难度。

6.如图1所示,为通用的class ab结构的输出极电路100,其包括:串联连接在供电端与地之间的晶体管m3和晶体管m4,串联连接在供电端与晶体管m3的控制端之间的电阻rc和电容cc,串联连接在晶体管m4的控制端与地之间的电容cc和电阻rc,以及连接在晶体管m3的控制端与晶体管m4的控制端之间的晶体管m1和晶体管m2,其中,晶体管m3和晶体管m4作为输出级的mos管,rc为补偿电阻,cc为补偿电容,cout为输出电容,cp为晶体管m3和晶体管m4的寄生电容,vbp和vbn分别为晶体管m1和晶体管m2栅端接入的偏置电压,且晶体管m1和晶体管m3均为pmos管,晶体管m2和晶体管m4均为nmos管。由于class ab结构是对称的,这里只以pmos管的部分(晶体管m3)举例说明。

7.当晶体管m3尺寸较小时,寄生电容cp很小,可以忽略不计。在图1所示结构中包含一个主极点fp1,一个非主极点fp2和一个零点fz1,fp1=1/ra/cc,fp2=1/cout/rout,fz1=1/rc/cc,其中ra为a点的阻抗,rout为运放的输出阻抗。可以通过调整rc的值,使fz1=fp2。这样系统就只会剩下一个主极点fp1,因此class ab结构的输出极电路100会具有很好的稳定性。

8.但当晶体管m3尺寸较大时,寄生电容cp较大,此时补偿电阻rc和补偿电容cc产生的零点被消除,系统只剩一个主极点fp1和一个非主极点fp2,其中,fp1=1/ra/(cc+cp),fp2=1/cout/rout。由于系统存在两个极点,所以class ab结构的输出极电路100是不稳定的,同时对于一些应用场景中输出极需要选用很大的mos管尺寸来满足大静态电流的需求也是无法实现的。

技术实现要素:

9.为了解决上述技术问题,本公开提供了一种输出级电路和ab类放大器,可以提高运放的稳定性,且能满足大静态电流的需求。

10.一方面本公开提供了一种输出级电路,包括:

11.输出端电路,其包括串联在供电端与地之间的第一晶体管和第二晶体管,且该第一晶体管和第二晶体管的中间节点用于提供输出电压;

12.补偿电路,具有连接前述第一晶体管的第一输出端和连接前述第二晶体管的第二输出端,用于对前述输出端电路提供进行高频极点补偿后的控制信号;

13.电压偏置电路,用于根据第一偏置电压和第二偏置电压对前述补偿电路的电压产生偏置。

14.优选地,前述补偿电路包括:

15.串联连接在供电端与前述电压偏置电路之间的第一电阻和第一电容;

16.串联连接在供电端与前述补偿电路第一输出端之间的第二电容;

17.第一缓冲器,该第一缓冲器的输入端连接在前述第一电容与前述电压偏置电路的连接节点,输出端作为前述补偿电路的第一输出端,连接前述第一晶体管的控制端。

18.优选地,前述补偿电路还包括:

19.串联连接在前述电压偏置电路与地之间的第三电容和第二电阻;

20.串联连接在前述补偿电路的第二输出端与地之间的第四电容;

21.第二缓冲器,该第二缓冲器的输入端连接在前述第三电容与前述电压偏置电路的连接节点,输出端作为前述补偿电路的第二输出端,连接前述第二晶体管的控制端。

22.优选地,前述电压偏置电路包括:

23.第三晶体管,连接在前述第一电容与前述第三电容之间,控制端接入前述第一偏置电压,且该第三晶体管与第一电容的连接节点作为前述第一缓冲器的输入端,该第三晶体管与第三电容的连接节点作为前述第二缓冲器的输入端;

24.第四晶体管,并联连接在前述第三晶体管两端,控制端接入前述第二偏置电压。

25.优选地,前述控制信号包括第一控制信号和第二控制信号,

26.前述第一晶体管的第一端连接在供电端,第二端与前述第二晶体管的第一端连接,控制端与前述补偿电路的第一输出端连接,用以接入前述第一控制信号,前述第二晶体管的第二端接地,控制端与前述补偿电路的第二输出端连接,用以接入前述第二控制信号。

27.优选地,该输出级电路还包括:

28.输出电容,连接在前述第一晶体管和第二晶体管的连接节点与地之间。

29.优选地,该输出级电路还包括:

30.偏置电压产生电路,用以提供前述第一偏置电压和前述第二偏置电压。

31.优选地,前述第一晶体管、第二晶体管、第三晶体管和第四晶体管的其中任一为金属氧化物半导体场效应晶体管。

32.优选地,前述第一晶体管和第三晶体管均为p型金属氧化物半导体场效应晶体管,且前述第二晶体管和第四晶体管均为n型金属氧化物半导体场效应晶体管。

33.另一方面本公开提供了一种ab类放大器,其中,包括如前所述的输出级电路。

34.本公开的有益效果是:本公开提供了一种输出级电路和ab类放大器,其中,该输出

级电路包括:输出端电路,其包括第一晶体管和第二晶体管,且该第一晶体管和第二晶体管的中间节点用于提供输出电压;补偿电路,具有连接该第一晶体管的第一输出端和连接该第二晶体管的第二输出端,用于对该输出端电路提供进行高频极点补偿后的控制信号;电压偏置电路,用于根据第一偏置电压和第二偏置电压对前述补偿电路的电压产生偏置。由此可以提高应用有该输出级电路的ab类放大器的稳定性,且能满足其大静态电流的需求。

附图说明

35.通过以下参照附图对本公开实施例的描述,本公开的上述以及其他目的、特征和优点将更为清楚。

36.图1示出现有技术中公开的一种通用class ab结构的输出极电路的示意图;

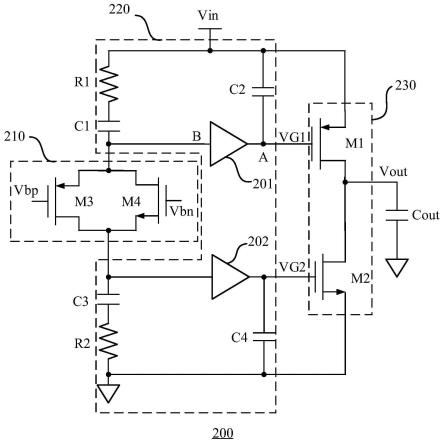

37.图2示出本公开实施例提供的一种class ab结构的输出极电路的示意图。

具体实施方式

38.为了便于理解本公开,下面将参照相关附图对本公开进行更全面的描述。附图中给出了本公开的较佳实施例。但是,本公开可以通过不同的形式来实现,并不限于本文所描述的实施例。相反的,提供这些实施例的目的是使对本公开内容的理解更加透彻全面。

39.在下文中描述了本公开的许多特定的细节,例如部件的结构、材料、尺寸、处理工艺和技术,以便更清楚地理解本公开。但正如本领域的技术人员能够理解的那样,可以不按照这些特定的细节来实现本公开。

40.应当理解,在以下的描述中,“电路”可包括单个或多个组合的硬件电路、可编程电路、状态机电路和/或能存储由可编程电路执行的指令的元件。当称元件或电路“连接到”另一元件或称元件/电路“连接在”两个节点之间时,它可以直接耦合或连接到另一元件或者可以存在中间元件,元件之间的连接可以是物理上的、逻辑上的、或者其结合。相反,当称元件“直接耦合到”或“直接连接到”另一元件时,意味着两者不存在中间元件。

41.在本技术中,mosfet(metal-oxide-semiconductor field-effect transistor,金属氧化物半导体场效应晶体管)包括第一端、第二端和控制端,在mosfet的导通状态,电流从第一端流至第二端。p型mosfet的第一端、第二端和控制端分别为源极、漏极和栅极,n型mosfet的第一端、第二端和控制端分别为漏极、源极和栅极。

42.除非另有定义,本文所使用的所有的技术和科学术语与属于本公开的技术领域的技术人员通常理解的含义相同。在本公开的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本公开。

43.现有的class ab运放的输出级电路中晶体管(一般选取金属氧化物半导体场效应晶体管(mos管))的尺寸都不太大,因为如果增加输出级mos管尺寸,mos管的栅极寄生电容也会随之增加,以图1中所示pmos管的部分(晶体管3)为例,当晶体管m3尺寸较大时,寄生电容cp较大,此时补偿电阻rc和补偿电容cc产生的零点被消除,系统只剩一个主极点fp1和一个非主极点fp2,其中,fp1=1/ra/(cc+cp),fp2=1/cout/rout。由于系统存在两个极点,所以class ab结构的输出极电路是不稳定的,这就会给运放的补偿增加难度。

44.因此,一般情况下class ab结构的输出极电路中mos管尺寸都选取的不太大。而受输出级电路中mos管尺寸的影响,class ab运放输出端拉灌电流也不能太大,这对于一些应

用场景中需要输出极选用很大的mos管尺寸来满足大静态电流的需求也是无法实现的。

45.基于此,本公开提供了一种输出级电路及ab类放大器,旨在通过简单的电路设计,不仅提高了运放的稳定性,而且能满足大静态电流的需求,不局限输出级选用的mos管尺寸,提高了该输出级电路的适用性。

46.下面,参照附图对本公开进行详细说明。

47.图2示出本公开实施例提供的一种class ab结构的输出极电路的示意图。

48.参考图2,一方面本公开实施例提供了一种输出级电路200,其包括:

49.输出端电路230,该输出端电路230包括串联在供电端vin与地之间的第一晶体管m1和第二晶体管m2,且该第一晶体管m1和第二晶体管m2的中间节点用于提供输出电压vout;

50.补偿电路220,该补偿电路220具有连接前述第一晶体管m1的第一输出端和连接前述第二晶体管m2的第二输出端,用于对前述输出端电路230提供进行高频极点补偿后的控制信号(vg1和vg2);

51.电压偏置电路210,该电压偏置电路210用于根据第一偏置电压vbp和第二偏置电压vbn对前述补偿电路220的电压产生偏置。

52.进一步地,前述补偿电路220包括:

53.串联连接在供电端vin与前述电压偏置电路210之间的第一电阻r1和第一电容c1;

54.串联连接在供电端vin与前述补偿电路220的第一输出端之间的第二电容c2,该第二电容c2与第一缓冲器201输出端之间具有连接节点a;

55.第一缓冲器201,该第一缓冲器201的输入端连接在前述第一电容c1与前述电压偏置电路210的连接节点b,输出端(连接节点a)作为前述补偿电路220的第一输出端,连接前述第一晶体管m1的控制端。

56.进一步地,前述补偿电路220还包括:

57.串联连接在前述电压偏置电路210与地之间的第三电容c3和第二电阻r2;

58.串联连接在前述补偿电路220的第二输出端与地之间的第四电容c4;

59.第二缓冲器202,该第二缓冲器202的输入端连接在前述第三电容c3与前述电压偏置电路210的连接节点,输出端作为前述补偿电路220的第二输出端,连接前述第二晶体管m2的控制端。

60.进一步地,前述电压偏置电路210包括:

61.第三晶体管m3,该第三晶体管m3连接在前述第一电容c1与前述第三电容c3之间,控制端接入前述第一偏置电压vbp,且该第三晶体管m3与第一电容c1的连接节点b作为前述第一缓冲器201的输入端,该第三晶体管m3与第三电容c3的连接节点作为前述第二缓冲器202的输入端;

62.第四晶体管m4,该第四晶体管m4并联连接在前述第三晶体管m3的两端,控制端接入前述第二偏置电压vbn。

63.进一步地,前述控制信号包括第一控制信号vg1和第二控制信号vg2,

64.且前述第一晶体管m1的第一端连接在供电端vin,第二端与前述第二晶体管m2的第一端连接,控制端与前述补偿电路220的第一输出端连接,用以接入前述第一控制信号vg1,前述第二晶体管m2的第二端接地,控制端与前述补偿电路220的第二输出端连接,用以

接入前述第二控制信号vg2。

65.进一步地,该输出级电路200还包括:

66.输出电容cout,该输出电容cout连接在前述第一晶体管m1和第二晶体管m2的连接节点与地之间。

67.进一步地,该输出级电路200还包括:

68.偏置电压产生电路(未示出),该偏置电压产生电路用以提供前述第一偏置电压vbp和前述第二偏置电压vbn。

69.在本实施例中,该偏置电压产生电路根据不同的应用场景自主选择,可以是独立的电路组件,也可以是集成与同一芯片中的前级电路,例如在一ab类放大器中该偏置电压的产生电路为输入级电路与输出级电路之间的中间级电路,在此不作限制。

70.进一步地,前述第一晶体管m1、第二晶体管m2、第三晶体管m3和第四晶体管m4的其中任一为金属氧化物半导体场效应晶体管(metal oxide semiconductor field-effect transistor,mosfet),简称为mos管。

71.在本实施例中,该第一晶体管和第三晶体管均为p型mos管,且该第二晶体管和第四晶体管均为n型mos管。

72.另一方面本公开实施例提供了一种ab类放大器,其中,该ab类放大器包括如前所述的输出级电路200。

73.在一种应用场景中,该输出级电路200作为ab类功率放大器(class ab)的输出级电路,由于class ab结构是对称的,故在本实施例中,该第一电容c1和第三电容c3作为补偿电容,二者的规格相同,即c1=c3=cc,该第一电阻r1与第二电阻r2作为补偿电阻,二者的的规格同样相同,即r1=r2=rc,第一缓冲器201与第二缓冲器202的电路参数(开环增益、输出阻抗等)相同,而第二电容c2与第四电容c4分别为第一晶体管m1于第二晶体管m2的寄生电容,c2=c4=cp。

74.在本实施例中,在class ab结构运放的输出级电路200中,通过补偿电路220中的第一缓冲器201和第二缓冲器202,将第一电容c1和第一电阻r1加到第一缓冲器201的输入端和供电端vin之间,将第三电容c3和第二电阻r2加到第二缓冲器201的输入端和地之间,阻隔该第一晶体管m1的寄生电容c2在第一缓冲器201的输出端,以及将该第二晶体管m2的寄生电容c4阻隔在第二缓冲器202的输出端,这样寄生电容cp的存在就不会影响补偿电阻rc引入零点的产生。

75.假设缓冲器(201/202)的开环增益为a,开环输出阻抗为rout1,连接节点a处的阻抗为ra,连接节点b处的阻抗为rb。则可以得到

76.ra=rout1/(1+a),

77.此时系统含有三个极点(pole)和一个零点(zero),其中

78.第一极点:fp1=1/rb/cc,

79.第二极点:fp2=1/cout/rout,其中,rout为运放的输出阻抗,

80.第三极点:fp3=1/ra/cp,

81.第一零点:fz1=1/rc/cc。

82.如果缓冲器(201/202)的开环增益a足够大,开环输出阻抗ra可以变得很小,那么第三极点fp3就可以位于高频段中较高频点的区域,对运放系统的稳定性几乎不产生影响。

那么就可以通过调整补偿电阻rc的值,使fz1=fp2,这样运放系统就因为只剩下一个主极点fp1,就能获得良好的稳定性。

83.所以,通过在该运放的输出级电路中,利用在第一晶体管m1和第二晶体管m2的栅极控制端各自连接的第一缓冲器201和第二缓冲器202,就可以将输出端电路230中的寄生电容(c2/c4)和现有技术中的补偿电容串联补偿电阻构成的补偿网络相隔离开来,并使输出端电路200的寄生电容(c2/c4)引入的极点推向高频,提高该运放输出级电路的稳定性。从而使class ab放大器中输出级电路的输出mos管(m1和m2)可以选用很大的尺寸来满足大电流的需求,提高了该输出级电路的适用性。

84.综上所述,本公开实施例提供的一种输出级电路和ab类放大器,其中,该输出级电路200包括:输出端电路230,其包括第一晶体管m1和第二晶体管m2,且该第一晶体管m1和第二晶体管m2的中间节点用于提供输出电压vout;补偿电路220,具有连接该第一晶体管m1的第一输出端和连接该第二晶体管m2的第二输出端,用于对该输出端电路230提供进行高频极点补偿后的控制信号(vg1和vg2);电压偏置电路210,用于根据第一偏置电压vbp和第二偏置电压vbn对前述补偿电路220的电压产生偏置。由此可以提高应用有该输出级电路的ab类放大器的稳定性,且能满足大静态电流的需求。

85.应当说明的是,在本公开的描述中,需要理解的是,术语“上”、“下”、“内”等指示方位或位置关系,仅是为了便于描述本公开和简化描述,而不是指示或暗示所指的组件或元件必须具有特定的方位,以特定的方位构造和操作,因此不能理解为对本公开的限制。

86.此外,在本文中,所含术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。

87.最后应说明的是:显然,上述实施例仅仅是为清楚地说明本公开所作的举例,而并非对实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引申出的显而易见的变化或变动仍处于本公开的保护范围之中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1