振荡器的制作方法

1.本发明涉及电子电路技术领域,尤其涉及一种振荡器。

背景技术:

2.振荡器是一种能量转换装置,可以产生一定频率、一定振幅和一定波形的交流信号。由于对集成度的要求,微控制器(micro controller unit,mcu)芯片内部需要集成高精度振荡器。

3.在芯片内,传统rc振荡器采用一个比较器对rc充放电做控制;传统电流源型锯齿波振荡器采用电流源和电流阱分别对电容充放电,然后通过两路比较器设定充放电电压阈值,通过sr触发器实现充放电的切换。

4.然而,现有的振荡器结构中都使用了比较器,由于比较器存在延时,在输出频率较低时(例如小于1mhz)时误差较小,但是当输出频率超过10mhz后,比较器的延时随温度以及电压变化,输出时钟频率误差较大。

技术实现要素:

5.本发明实施例解决的是输出时钟频率随温度以及电压的变化而变化所导致误差较大的技术问题。

6.为解决上述技术问题,本发明实施例提供一种振荡器,包括:斩波电压平均值反馈电路、rc充放电电路、阈值电压检测电路、esr触发控制电路、稳定时钟输出电路以及斩波时钟自举电路,其中:所述斩波电压平均值反馈电路,其第一输入端输入温漂校准参考电压,其第二输入端与所述rc充放电电路的第一电压输出端耦接,其时钟信号输入端与所述斩波时钟自举电路的时钟信号输出端耦接,其使能信号输入端与所述斩波时钟自举电路的使能信号输出端耦接;所述阈值电压检测电路,其第一输入端与第二输入端均与所述斩波电压平均值反馈电路的输出端耦接,其第三输入端与所述rc充放电电路的第二电压输出端耦接,其第四输入端与所述rc充放电电路的第三电压输出端耦接;所述rc充放电电路,其第一输入端与所述esr触发控制电路的第一输出端耦接,其第二输入端与所述esr触发控制电路的第二输出端耦接;所述esr触发控制电路,其第一输入端与所述阈值电压检测电路的第一输出端耦接,其第二输入端与所述阈值电压检测电路的第二输出端耦接,其第三输入端输入使能信号;所述稳定时钟输出电路,其第一输入端与所述esr触发控制电路的第二输出端耦接,其第二输入端与所述esr触发控制电路的第一输出端耦接,其第一输出端输出第一输出时钟信号,其第二输出端输出第二输出时钟信号,其第三输出端输出时钟稳定指示信号;所述斩波时钟自举电路,其时钟信号输入端与所述稳定时钟输出电路的第二输出端耦接,其使能信号输入端与所述稳定时钟输出电路的第三输出端耦接。

7.可选的,所述斩波电压平均值反馈电路包括:斩波运算放大器coa以及积分环路,其中:所述斩波运算放大器coa,其第一输入端输入所述温漂校准参考电压,其第二输入端与所述积分电路的输入端耦接,其输出端与所述积分电路的输出端、所述阈值电压检测电

路的第一输入端及其第二输入端耦接;所述积分环路,其输入端与所述rc充放电电路的第一电压输出端耦接。

8.可选的,所述积分环路包括积分电阻rx以及积分电容cx,其中:所述积分电阻rx,其第一端与所述rc充放电电路的第一电压输出端耦接,其第二端与所述积分电容cx的第一端、所述斩波运算放大器coa的第二输入端耦接;所述积分电容cx,其第二端与所述斩波运算放大器coa的输出端耦接。

9.可选的,所述斩波运算放大器coa包括:第一斩波电路、第二斩波电路、第三斩波电路、第一运算放大器、第二运算放大器、第三运算放大器、第四运算放大器、噪声带阻滤波器以及输出滤波电容,其中:所述第一运算放大器、所述第二运算放大器以及所述第三运算放大器为轨对轨差分输入轨对轨差分输出运算放大器,所述第四运算放大器为轨对轨差分输入轨对轨单端输出运算放大器,其中:所述第一斩波电路,其第一输入端为所述斩波运算放大器coa的第一输入端,其第二输入端为所述斩波运算放大器coa的第二输入端;所述第一运算放大器,其第一输入端与所述第一斩波电路的第一输出端、所述第三运算放大器的第一输出端耦接,其第二输入端与所述第一斩波电路的第二输出端、所述第三运算放大器的第二输出端耦接;所述第二斩波电路,其第一输入端与所述第一运算放大器的第一输出端耦接,其第二输入端与所述第一运算放大器的第二输出端耦接;所述第二运算放大器,其第一输入端与所述第二斩波电路的第一输出端耦接,其第二输入端与所述第二斩波电路的第二输出端耦接;所述第三斩波电路,其第一输入端与所述第二运算放大器的第一输出端耦接,其第二输入端与所述第二运算放大器的第二输出端耦接;所述噪声带阻滤波器,其第一输入端与所述第三斩波电路的第一输出端耦接,其第二输入端与所述第三斩波电路的第二输出端耦接;所述第三运算放大器,其第一输入端与所述噪声带阻滤波器的第一输出端耦接,其第二输入端与所述噪声带阻滤波器的第二输出端耦接;所述第四运算放大器,其第一输入端与所述第二斩波电路的第一输出端耦接,其第二输入端与所述第二斩波电路的第二输出端耦接,其输出端为所述斩波运算放大器coa的输出端;所述输出滤波电容,耦接在所述第四运算放大器的第二输入端与所述第四运算放大器的输出端之间;所述第一斩波电路、所述第二斩波电路、所述第三斩波电路以及所述噪声带阻滤波器均包括使能信号输入端以及时钟信号输入端,其所述第一斩波电路、所述第二斩波电路、所述第三斩波电路以及所述噪声带阻滤波器的使能信号输入端均与所述斩波电压平均值反馈电路的使能信号输入端耦接,所述第一斩波电路、所述第二斩波电路、所述第三斩波电路以及所述噪声带阻滤波器的时钟信号输入端均与所述斩波电压平均值反馈电路的时钟信号输入端耦接。

10.可选的,所述斩波时钟自举电路,包括:第一可编程计数器、第一d触发器、第二d触发器以及第一反相器,其中:所述第一可编程计数器,其时钟信号输入端与所述稳定时钟输出电路的第二输出端耦接,其使能信号输入端与所述稳定时钟输出电路的第三输出端耦接,其控制端输入第一控制信号,其输出端与所述第一d触发器的时钟信号输入端耦接;所述第一d触发器,其数据端与所述第一反相器的输出端耦接,其输出端与所述第一反相器的输入端、所述第二d触发器的时钟信号输入端以及所述斩波电压平均值反馈电路的时钟信号输入端耦接,其使能端与所述稳定时钟输出电路的第三输出端耦接;所述第二d触发器,其数据端输入预设的电源电压,其输出端与所述斩波电压平均值反馈电路的使能信号输入端耦接,其使能端与所述稳定时钟输出电路的第三输出端耦接。

11.可选的,所述阈值电压检测电路包括:第一比较器与第二比较器,其中:所述第一比较器,其第一输入端与所述斩波电压平均值反馈电路的输出端耦接,其第二输入端与所述rc充放电电路的第二电压输出端耦接,其输出端与所述esr触发控制电路的第一输入端耦接;所述第二比较器,其第一输入端与所述斩波电压平均值反馈电路的输出端耦接,其第二输入端与所述rc充放电电路的第三电压输出端耦接,其输出端与所述esr触发控制电路的第二输入端耦接。

12.可选的,所述esr触发控制电路包括:第一与非门、第二与非门以及缓冲器,其中:所述第一与非门,其第一输入端与所述阈值电压检测电路的第一输出端耦接,其使能端与所述缓冲器的输出端耦接,其第二输入端与所述第二与非门的输出端耦接,其输出端为所述esr触发控制电路的第二输出端;所述第二与非门,其第一输入端与所述阈值电压检测电路的第二输出端耦接,其使能端与所述缓冲器的输入端耦接,其第二输入端与所述第一与非门的输出端耦接,其输出端为所述esr触发控制电路的第一输出端;所述缓冲器,其输入端输入使能信号,其输出端还与所述斩波时钟自举电路的使能信号输入端耦接。

13.可选的,所述稳定时钟输出电路包括:频率稳定指示电路、第一与门以及第二与门,其中:所述频率稳定指示电路,其输入端与所述esr触发控制电路的第二输出端耦接,其输出端与所述第一与门的第一输入端、所述第二与门的第一输入端、所述斩波时钟自举电路的使能信号输入端耦接;所述第一与门,其第二输入端与所述esr触发控制电路的第二输出端耦接,其输出端输出所述第一输出时钟信号;所述第二与门,其第二输入端与所述esr触发控制电路的第一输出端耦接,其输出端输出所述第二输出时钟信号。

14.可选的,所述频率稳定指示电路包括:第二可编程计数器、第三d触发器、第四d触发器以及第二反相器,其中:所述第二可编程计数器,其使能信号输入端输入使能信号,其时钟信号输入端为所述频率稳定指示电路的输入端,其控制端输入第二控制信号,其输出端与所述第三d触发器的时钟信号输入端耦接;所述第三d触发器,其数据端与所述第二反相器的输出端耦接,其输出端与所述第二反相器的输入端、所述第四d触发器的时钟信号输入端耦接,其使能端输入所述使能信号;所述第四d触发器,其数据端输入预设的电源电压,其输出端为所述频率稳定指示电路的输出端,其使能端输入所述使能信号。

15.可选的,所述rc充放电电路,包括:第一可调电阻、第二可调电阻、第一可调电容、第二可调电容以及第一开关电路、第二开关电路、第三开关电路、第四开关电路、第五开关电路以及第六开关电路,其中:所述第一开关电路,其动端输入电源电压,其定端与所述第一可调电阻的第一端耦接,其控制端与所述esr触发控制电路的第二输出端耦接;所述第一可调电阻,其第二端与所述第五开关电路的动端、所述第二开关电路的定端以及所述第一可调电容的第一端耦接,且其第二端还与所述阈值电压检测电路的第三输入端耦接;所述第五开关电路,其定端与所述第一可调电容的第二端耦接,其控制端与所述esr触发控制电路的第一输出端耦接;所述第一可调电容,其第二端与地耦接;所述第二开关电路,其动端与所述rc充放电电路的第一电压输出端耦接,其控制端与所述esr触发控制电路的第二输出端耦接;所述第三开关电路,其动端输入所述电源电压,其定端与所述第二可调电阻的第一端耦接,其控制端与所述esr触发控制电路的第一输出端耦接;所述第二可调电阻,其第二端与所述第六开关电路的动端、所述第四开关电路的定端以及所述第二可调电容的第一端耦接,且其第二端还与所述阈值电压检测电路的第四输入端耦接;所述第六开关电路,其

定端与所述第二可调电容的第二端耦接,其控制端与所述esr触发控制电路的第二输出端耦接;所述第二可调电容,其第二端与地耦接;所述第四开关电路,其动端与所述rc充放电电路的第一电压输出端耦接,其控制端与所述esr触发控制电路的第一输出端耦接。

16.可选的,所述温漂校准参考电压由温漂校准参考电压生成电路生成,并经由所述温漂校准参考电压生成电路的输出端输出。

17.可选的,所述温漂校准参考电压生成电路包括:pmos电流源、第一nmos电流源、第二nmos电流源,以及依次串联的第三可调电阻、第四可调电阻、第五可调电阻以及第六可调电阻,其中:所述pmos电流源的第一输出端与所述第五可调电阻的第二端、所述第六可调电阻的第一端耦接;所述第一nmos电流源的输入端与所述pmos电流源的第二输出端耦接,所述第一nmos电流源的输出端与所述pmos电流源的输入端耦接;所述第二nmos电流源的输入端与所述pmos电流源的第三输出端耦接,所述第二nmos电流源的输出端与所述第四可调电阻的第一端、所述第三可调电阻的第二端耦接;所述第三可调电阻,其第一端输入电源电压,其第二端与所述第四可调电阻的第一端耦接;所述第四可调电阻,其第二端与所述第五可调电阻的第一端、所述nmos电流源的输出端耦接,与所述温漂校准参考电压生成电路的输出端耦接;所述第五可调电阻,其第一端与所述温漂校准参考电压生成电路的输出端耦接,其第二端与所述第六可调电阻的第一端、所述pmos电流源的输出端耦接;所述第六可调电阻,其第二端接地。

18.可选的,所述pmos电流源包括:第一pmos管、第二pmos管、第三pmos管以及第四pmos管,其中:所述第一pmos管,其源极输入电源电压,其栅极与所述第二pmos管的栅极、所述第二pmos管的漏极耦接,其漏极与所述第一nmos电流源的输入端耦接;所述第二pmos管,其源极输入所述电源电压,其漏极与其栅极与所述第一nmos电流源的输出端耦接;所述第三pmos管,其源极输入所述电源电压,其栅极与所述第一pmos管的栅极、所述第二pmos管的栅极耦接,其漏极与所述第二nmos电流源的输入端耦接;所述第四pmos管,其源极输入所述电源电压,其栅极与所述第一pmos管的栅极、所述第二pmos管的栅极、第三pmos管的栅极均耦接,其漏极为所述pmos电流源的第一输出端。

19.可选的,所述第一nmos电流源包括:第一nmos管、第二nmos管、第一pnp三极管、第二pnp三极管以及电流电阻,其中:所述第一nmos管,其栅极与其漏极耦接,其源极与所述第一pnp三极管的发射极耦接,所述第一nmos管的漏极为所述第一nmos电流源的输入端;所述第二nmos管,其栅极与所述第一nmos管的栅极耦接,其漏极为所述第一nmos电流源的输出接,其源极与所述电流电阻的第一端耦接;所述电流电阻,其第二端与所述第二pnp三极管的发射极耦接;所述第一pnp三极管,其基极与其集电极耦接且均接地;所述第二pnp三极管,其基极与其集电极耦接且均接地。

20.可选的,所述第二nmos电流源包括:第三nmos管以及第四nmos管,其中:所述第三nmos管,其栅极与其漏极耦接,为所述第二nmos电流源的输入端,其源极接地;所述第四nmos管,其栅极与所述第三nmos管的栅极耦接,其漏极为所述第二nmos电流源的输出端,其源极接地。

21.与现有技术相比,本发明实施例的技术方案具有以下有益效果:

22.通过温漂校准参考电压生成电路生成具有特定温度系数的温漂校准参考电压,配合带有自校准反馈环路的斩波电压平均值反馈电路,实现输出时钟频率与温度和电压无

关。

23.进一步,斩波电压平均值反馈电路中的积分环路能够消除高频噪声,且通过积分环路能够消除斩波运算放大器中的比较器的延迟时间。斩波运算放大器带有自校准反馈环路,可以在降低失调电压和闪烁噪声的同时抑制斩波噪声,且振荡器的高频率相位噪声也能够被负反馈结构所抑制,对高频电源噪声的敏感度较低。

24.此外,通过斩波时钟自举电路实现斩波运算放大器的时钟自举,能够提供频率稳定的时钟信号。

附图说明

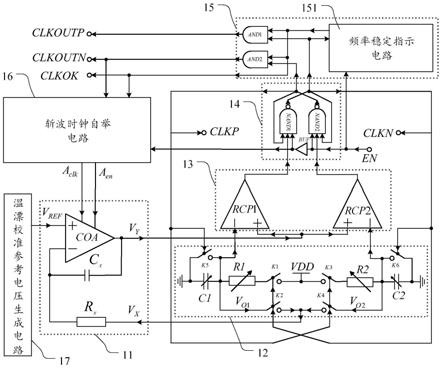

25.图1是本发明实施例中的一种振荡器的结构示意图;

26.图2是本发明实施例中的一种斩波运算放大器的结构示意图;

27.图3是本发明实施例中的一种频率稳定指示电路的结构示意图;

28.图4是本发明实施例中的一种斩波时钟自举电路的结构示意图;

29.图5是本发明实施例中的一种温漂校准参考电压生成电路的结构示意图;

30.图6是本发明实施例中的一种积分环路输出噪声的传输特性示意图;

31.图7是本发明实施例中的一种积分环路相位噪声的传输特性示意图;

32.图8是本发明实施例中的一种普通运算放大器的输出噪声示意图;

33.图9是本发明实施例中的一种普通斩波运算放大器的输出噪声示意图;

34.图10是本发明实施例中的一种包含自校准反馈环路的斩波运算放大器的输出噪声示意图;

35.图11是本发明实施例中的一种斩波电压平均值反馈电路的输出噪声示意图。

具体实施方式

36.由上可知,现有的振荡器结构中都使用了比较器,由于比较器存在延时,在输出频率较低时(例如小于1mhz)时误差较小,但是当输出频率超过10mhz后,比较器的延时随温度以及电压变化,输出时钟频率误差较大。

37.在本发明实施例中,通过温漂校准参考电压生成具有特定温度系数的温漂校准参考电压,配合带有自校准反馈环路的斩波电压平均值反馈电路,实现输出时钟频率与温度和电压无关。

38.为使本发明的上述目的、特征和有益效果能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

39.参照图1,本发明实施例提供了一种振荡器,包括:斩波电压平均值反馈电路11、rc充放电电路12、阈值电压检测电路13、esr触发控制电路14、稳定时钟输出电路15、斩波时钟自举电路16以及温漂校准参考电压生成电路17。

40.在具体实施中,斩波电压平均值反馈电路11的第一输入端输入温漂校准参考电压,斩波电压平均值反馈电路11的第二输入端与rc充放电电路12的第一电压输出端耦接,斩波电压平均值反馈电路11的时钟信号输入端与斩波时钟自举电路16的时钟信号输出端耦接,斩波电压平均值反馈电路11的使能信号输入端与斩波时钟自举电路16的使能信号输出端耦接;

41.阈值电压检测电路13的第一输入端以及第二输入端均与斩波电压平均值反馈电路11的输出端耦接,阈值电压检测电路13的第三输入端与rc充放电电路12的第二电压输出端耦接,阈值电压检测电路13的第四输入端与rc充放电电路12的第三电压输出端耦接;

42.rc充放电电路12的第一输入端与esr触发控制电路14的第一输出端耦接,rc充放电电路12的第二输入端与esr触发控制电路14的第二输出端耦接;

43.esr触发控制电路14的第一输入端与阈值电压检测电路13的第一输出端耦接,esr触发控制电路14的第二输入端与阈值电压检测电路13的第二输出端耦接;其中输入端en为整个电路的输入使能,控制整个电路的开启与关断。

44.稳定时钟输出电路15的第一输入端与esr触发控制电路14的第二输出端耦接,稳定时钟输出电路15的第二输入端与esr触发控制电路14的第一输出端耦接,稳定时钟输出电路15的第一输出端输出第一输出时钟信号clkoutp,稳定时钟输出电路15的第二输出端输出第二输出时钟信号clkoutn,稳定时钟输出电路15的第三输出端输出时钟稳定指示信号clkok。

45.斩波时钟自举电路16的时钟信号输入端与稳定时钟输出电路15的第二输出端耦接,斩波时钟自举电路16的使能信号输入端与稳定时钟输出电路15的第三输出端耦接。

46.下面对上述的振荡器的具体结构进行详细说明。

47.在具体实施中,斩波电压平均值反馈电路11可以包括斩波运算放大器coa以及积分环路。

48.在本发明实施例中,斩波运算放大器coa的第一输入端输入温漂校准参考电压,斩波运算放大器coa的第二输入端与积分电路的输入端耦接,斩波运算放大器coa的输出端与积分电路的输出端、阈值电压检测电路13的第一输入端、阈值电压检测电路13的第二输入端耦接。

49.积分电路的输入端还可以与rc充放电电路12的第一电压输出端耦接。

50.在具体实施中,积分环路可以包括积分电阻rx以及积分电容cx,其中:

51.积分电阻rx的第一端与rc充放电电路12的第一电压输出端耦接,积分电路的第二端与积分电容cx的第一端、斩波运算放大器coa的第二输入端耦接;积分电容cx的第二端与斩波运算放大器coa的输出端耦接。

52.在具体应用中,积分电阻rx的第一端可以为积分环路的输入端,积分电容cx的第二端可以为积分环路的输出端。

53.在具体实施中,斩波运算放大器coa的第一输入端可以为其对应的“+”输入端,斩波运算放大器coa的第二输入端可以为其对应的

“‑”

输入端。

54.可以理解的是,在实际应用中,积分环路的结构并不仅限于上述示例。

55.下面对本发明实施例中提供的斩波运算放大器coa进行详细说明。参照图2,给出了本发明实施例中的一种斩波运算放大器coa的结构示意图。

56.在本发明实施例中,斩波运算放大器coa可以包括第一斩波电路cp1、第二斩波电路cp2、第三斩波电路cp3、第一运算放大器a1、第二运算放大器a2、第三运算放大器a3、第四运算放大器a4、噪声带阻滤波器nf以及输出滤波电容cc,其中:

57.第一斩波电路cp1,其第一输入端为斩波运算放大器coa的第一输入端,其第二输入端为斩波运算放大器coa的第二输入端;

58.第一运算放大器a1为轨对轨差分输入轨对轨差分输出运算放大器,第一运算放大器a1的第一输入端与第一斩波电路cp1的第一输出端、第三运算放大器a3的第一输出端耦接,第一运算放大器a1的第二输入端与第一斩波电路cp1的第二输出端、第三运算放大器a3的第二输出端耦接;

59.第二斩波电路cp2的第一输入端与第一运算放大器a1的第一输出端耦接,第二斩波电路cp2的第二输入端与第一运算放大器a1的第二输出端耦接;

60.第二运算放大器a2为轨对轨差分输入轨对轨差分输出运算放大器,第二运算放大器a2的第一输入端与第二斩波电路cp2的第一输出端耦接,第二运算放大器a2的第二输入端与第二斩波电路cp2的第二输出端耦接;

61.第三斩波电路cp3的第一输入端与第二运算放大器a2的第一输出端耦接,第三斩波电路cp3的第二输入端与第二运算放大器a2的第二输出端耦接;

62.噪声带阻滤波器nf的第一输入端与第三斩波电路cp3的第一输出端耦接,噪声带阻滤波器nf的第二输入端与第三斩波电路cp3的第二输出端耦接;

63.第三运算放大器a3为轨对轨差分输入轨对轨差分输出运算放大器,第三运算放大器a3的第一输入端与噪声带阻滤波器nf的第一输出端耦接,第三运算放大器a3的第二输入端与噪声带阻滤波器nf的第二输出端耦接;

64.第四运算放大器a4的第一输入端与第二斩波电路cp2的第一输出端耦接,第四运算放大器a4的第二输入端与第二斩波电路cp2的第二输入端耦接,第四运算放大器a4的输出端为斩波运算放大器coa的输出端;

65.输出滤波电容cc耦接在第四运算放大器a4的第二输入端与第四运算放大器a4的输出端之间。

66.在本发明实施例中,第一斩波电路cp1、第二斩波电路cp2、第三斩波电路cp3以及噪声带阻滤波器nf均包括使能信号输入端以及时钟信号输入端,且:第一斩波电路cp1、第二斩波电路cp2、第三斩波电路cp3以及噪声带阻滤波器nf的使能信号输入端,均与斩波电压平均值反馈电路11的使能信号输入端耦接;第一斩波电路cp1、第二斩波电路cp2、第三斩波电路cp3以及噪声带阻滤波器nf的时钟信号输入端,均与斩波电压平均值反馈电路11的时钟信号输入端耦接。

67.换而言之,第一斩波电路cp1、第二斩波电路cp2、第三斩波电路cp3以及噪声带阻滤波器nf的使能信号输入端输入的使能信号,是斩波时钟自举电路16的使能信号输出端输出的使能信号a

en

;第一斩波电路cp1、第二斩波电路cp2、第三斩波电路cp3以及噪声带阻滤波器nf的时钟信号输入端输入的时钟信号,是斩波时钟自举电路16的时钟信号输出端输出的时钟信号a

clk

。

68.在本发明实施例中,第一运算放大器a1的第一输入端为其“+”输入端,第一运算放大器a1的第二输入端为其

“‑”

输入端,第一运算放大器a1的第一输出端为其“+”输出端,第一运算放大器a1的第二输出端为其

“‑”

输出端。

69.相应地,对于第二运算放大器a2以及第三运算放大器a3,对应的第一输入端均为其“+”输入端,对应的第二输入端为

“‑”

输入端,对应的第一输出端为“+”输出端,对应的第二输出端均为

“‑”

输出端。

70.对于第四运算放大器a4,其第一输入端为其“+”输入端,其第二输入端为其

“‑”

输

入端。

71.在图2中,斩波运算放大器coa的第一输入端为inp,斩波运算放大器coa的第二输入端为inn,斩波运算放大器coa的输出端为vout。实质上,将图2中的斩波运算放大器coa应用在图1中时,其中的inp端口为斩波运算放大器coa的“+”输入端,其中的inn端口为斩波运算放大器coa的

“‑”

输入端,其中的vout端口输出的电压为v

y

。

72.采用上述结构的斩波运算放大器coa,其内部包含自校准反馈环,从而能够滤除斩波纹波。在低频时能够去除闪烁噪声和失调电压,高频噪声能够被耦接的积分环路滤除,因此输出的时钟信号的抖动较小。

73.参照图1,在本发明实施例中,rc充放电电路12可以包括第一可调电阻r1、第二可调电阻r2、第一可调电容c1、第二可调电容c2以及第一开关电路k1、第二开关电路k2、第三开关电路k3、第四开关电路k4、第五开关电路k5、第六开关电路k6,其中:

74.第一开关电路k1的动端输入电源电压vdd,第一开关电路k1的定端与第一可调电阻r1的第一端耦接,第一开关电路k1的控制端与esr触发控制电路14的第二输出端耦接;

75.第一可调电阻r1的第二端与第五开关电路k5的动端、第二开关电路k2的定端以及第一可调电容c1的第一端耦接,第一可调电阻r1的第二端还与阈值电压检测电路13的第三输入端耦接;换而言之,第一可调电阻r1的第二端可以为rc充放电电路12的第二电压输出端;

76.第五开关电路k5的定端与第一可调电容c1的第二端耦接,第五开关电路k5的控制端与esr触发控制电路14的第一输出端耦接;

77.第一可调电容c1的第二端接地,且第五开关电路k5的定端也接地;

78.第二开关电路k2的动端与rc充放电电路12的第一电压输出端耦接,第二开关电路k2的控制端与esr触发控制电路14的第二输出端耦接;

79.第三开关电路k3的动端输入电源电压vdd,第三开关电路k3的定端与第二可调电阻r2的第一端耦接,第三开关电路k3的控制端与esr触发控制电路14的第一输出端耦接;

80.第二可调电阻r2的第二端与第六开关电路k6的动端、第四开关电路k4的定端以及第二可调电容c2的第一端耦接,第二可调电阻r2的第二端还与阈值电压检测电路13的第四输入端耦接;换而言之,第二可调电阻r2的第二端可以为rc充放电电路12的第三电压输出端;

81.第六开关电路k6的定端可以与第二可调电容c2的第二端耦接,第六开关电路k6的控制端与esr触发控制电路14的第二输出端耦接;

82.第二可调电容c2的第二端与地耦接,且第六开关电路k6的第二端也接地;

83.第四开关电路k4的动端与rc充放电电路12的第一电压输出端耦接,第四开关电路k4的控制端与esr触发控制电路14的第一输出端耦接。

84.在本发明实施例中,rc充放电电路12可以等效为一个由斩波电压平均值反馈电路11的输出电压作为控制信号的压控振荡器。第二开关电路k2的定端的电压、第四开关电路k4的定端的电压合成为经由rc充放电电路12的第一电压输出端输出的电压,并输入至斩波电压平均值反馈电路11。由于虚短虚断特性,rc充放电电路12的第一电压输出端输出的电压维持在温漂校准参考电压v

ref

附近。

85.参照图1,由斩波电压平均值反馈电路11的输出v

y

作为控制信号对rc充放电电路

12进行间接控制。第二开关电路k2的定端的电压v

o1

与第四开关电路k4的定端的电压v

o2

合成为v

x

,并经由积分电阻rx输入至斩波运算放大器coa的第二输入端。由于虚短虚断特性,v

x

维持在v

ref

附近。

86.参照图1,在具体实施中,阈值电压检测电路13可以包括:第一比较器rcp1以及第二比较器rcp2,其中:

87.第一比较器rcp1的第一输入端与斩波电压平均值反馈电路11的输出端耦接,第一比较器rcp1的第二输入端与rc充放电电路12的第二电压输出端耦接,第一比较器rcp1的输出端与esr触发控制电路14的第一输入端耦接;

88.第二比较器rcp2的第一输入端与斩波电压平均值反馈电路11的输出端耦接,第二比较器rcp2的第二输入端与rc充放电电路12的第三电压输出端耦接,第二比较器rcp2的输出端与esr触发控制电路14的第二输入端耦接。

89.在本发明实施例中,第一比较器rcp1的第一输入端可以为阈值电压检测电路13的第一输入端,第一比较器rcp1的第二输入端可以为阈值电压检测电路13的第二输入端,第一比较器rcp1的输出端可以为阈值电压检测电路13的第一输出端。

90.第二比较器rcp2的第一输入端可以为阈值电压检测电路13的第三输入端,第二比较器rcp2的第二输入端可以为阈值电压检测电路13的第四输入端,第二比较器rcp2的输出端可以为阈值电压检测电路13的第二输出端。

91.在具体实施中,第一比较器rcp1与第二比较器rcp2为互补轨对轨输入比较器。

92.在具体实施中,esr触发控制电路14包括:第一与非门nand1、第二与非门nand2以及缓冲器buf,其中:

93.第一与非门nand1的第一输入端与阈值电压检测电路13的第一输出端耦接,第一与非门nand1的使能端与缓冲器buf的输出端耦接,第一与非门nand1的第二输入端与第二与非门nand2的输出端耦接;第一与非门nand1的输出端为esr触发控制电路14的第二输出端clkn;

94.第二与非门nand2的第一输入端与阈值电压检测电路13的第二输出端耦接,第二与非门nand2的使能端与缓冲器buf的输入端耦接,第二与非门nand2的第二输入端与第一与非门nand1的输出端耦接,第二与非门nand2的输出端为esr触发控制电路14的第一输出端clkp。

95.缓冲器buf在en使能时实现一个ns级别的延时,从而保证esr触发控制电路进入正常工作状态。

96.在具体实施中,稳定时钟输出电路15可以包括:频率稳定指示电路151、第一与门and1以及第二与门and2,其中:

97.频率稳定指示电路151的输入端与esr触发控制电路14的第二输出端耦接,频率稳定指示电路151的输出端与第一与门and1的第一输入端、第二与门and2的第一输入端以及斩波时钟自举电路16的使能信号输入端耦接;

98.第一与门and1的第二输入端与esr触发控制电路14的第二输出端耦接,第一与门and1的输出端输出第一输出时钟信号clkoutp;

99.第二与门and2的第二输入端与esr触发控制电路14的第一输出端耦接,第二与门and2的输出端输出第二输出时钟信号clkoutn。

100.在本发明实施例中,频率稳定指示电路151的输入端可以为稳定时钟输出电路15的第一输入端clkn;第二与门and2的第二输入端可以为稳定时钟输出电路15的第二输入端clkp;频率稳定指示电路151的输出端可以为稳定时钟输出电路15的第三输出端,用以输出时钟稳定指示信号clkok;

101.第一与门and1的输出端可以为稳定时钟输出电路15的第一输出端,用以输出第一输出时钟信号clkoutp;

102.第二与门and2的输出端可以为稳定时钟输出电路15的第二输出端,用以输出第二输出时钟信号clkoutn。

103.参照图3,给出了本发明实施例中的一种频率稳定指示电路151的结构示意图。

104.在具体实施中,频率稳定指示电路151可以包括:第二可编程计数器、第三d触发器d3、第四d触发器d4以及第二反相器inv2,其中:

105.第二可编程计数器的使能信号输入端输入使能信号en,第二可编程计数器的时钟信号输入端为频率稳定指示电路151的输入端,第二可编程计数器的控制端输入第二控制信号f<15:0>,第二可编程计数器的输出端与第三d触发器d3的时钟信号输入端耦接;

106.第三d触发器d3的数据端d与第二反相器inv2的输出端耦接,第三d触发器d3的输出端q与第二反相器inv2的输入端、第四d触发器d4的时钟信号输入端耦接,第三d触发器d3的复位端输入是使能信号en;

107.第四d触发器d4的数据端d输入预设的电源电压vdd,第四d触发器d4的输出端q为频率稳定指示电路151的输出端,第四d触发器d4的复位端输入是使能信号en。

108.在本发明实施例中,第二可编程计数器可以为16位可编程计数器,其中输入的第二控制信号f<15:0>为延时输出时钟稳定指示信号clkok的时钟周期个数。对于16为可编程计数器,其对应的延时时长的范围为0~2

16

‑

1个周期。

109.例如,第二控制信号为0x0003,则延迟3个周期后输出时钟稳定指示信号clkok至斩波时钟自举电路16。

110.参照图4,给出了本发明实施例中的一种斩波时钟自举电路16的结构示意图。

111.在具体实施中,斩波时钟自举电路16可以包括第一可编程计数器、第一d触发器d1、第二d触发器以及第一反相器inv1,其中:

112.第一可编程计数器的第一时钟信号输入端是第二输出时钟信号clkoutn,第一可编程计数器的使能信号输入端是时钟稳定指示信号clkok,第一可编程计数器的控制端输入第一控制信号,第一可编程计数器的输出端与第一d触发器d1的时钟信号输入端耦接;

113.第一d触发器d1的数据端d与第一反相器inv1的输出端耦接,第一d触发器d1的输出端q与第一反相器inv1的输入端、第二d触发器d2的时钟信号输入端以及斩波电压平均值反馈电路11的时钟信号输入端耦接,第一d触发器的复位端输入时钟稳定指示信号clkok;

114.第二d触发器d2的数据端d输入预设的电源电压vdd,第二d触发器d2的输出端q与斩波电压平均值反馈电路11的使能信号输入端耦接,第二d触发器d2的复位端输入时钟稳定指示信号clkok。

115.在本发明实施例中,第一可编程计数器的第一时钟信号输入端可以为斩波时钟自举电路16的时钟信号输入端,第一可编程计数器的使能信号输入端可以为斩波时钟自举电路16的使能信号输入端,第一d触发器d1的输出端q可以为斩波时钟自举电路16的时钟信号

输出端,输出时钟信号a

clk

;第二d触发器d2的输出端q可以为斩波时钟自举电路16的使能信号输出端,输出使能信号a

en

。

116.在具体实施中,第一可编程计数器的可以为64位可编程计数器,其中输入的第一控制信号(c<63:0>)为分频比值,用以对输入的第二输出时钟信号clkoutn进行分频。

117.在具体实施中,温漂校准参考电压可以由温漂校准参考电压生成电路17生成。

118.参照图5,给出了本发明实施例中的一种温漂校准参考电压生成电路17的结构示意图。

119.在本发明实施例中,温漂校准参考电压生成电路17可以包括:pmos电流源、第一nmos电流源、第二nmos电流源,以及依次串联的第三可调电阻r3、第四可调电阻r4、第五可调电阻r5以及第六可调电阻r6,其中:

120.pmos电流源的第一输出端与第五可调电阻r5的第二端、第六可调电阻r6的第一端耦接;

121.第一nmos电流源的输入端与pmos电流源的第二输出端耦接,第一nmos电流源的输出端与pmos电流源的输入端耦接;

122.第二nmos电流源的输出端与第四可调电阻r4的第一端、第三可调电阻r3的第二端耦接;

123.第三可调电阻r3,其第一端输入电源电压,其第二端与第四可调电阻r4的第一端耦接;

124.第四可调电阻r4,其第二端与第五可调电阻r5的第一端、nmos电流源的输出端耦接,与温漂校准参考电压生成电路的输出端耦接;

125.第五可调电阻r5,其第一端与温漂校准参考电压生成电路的输出端耦接,其第二端与第六可调电阻r6的第一端、pmos电流源的输出端耦接;

126.第六可调电阻r6,其第二端接地。

127.在具体实施中,pmos电流源可以包括:第一pmos管mp1、第二pmos管mp2、第三pmos管mp3以及第四pmos管mp4,其中:

128.第一pmos管mp1,其源极输入电源电压,其栅极与第二pmos管mp2的栅极、第二pmos管mp2的漏极耦接,其漏极与第一nmos电流源的输入端耦接;

129.第二pmos管mp2,其源极输入电源电压,其漏极与其栅极与第一nmos电流源的输出端耦接;

130.第三pmos管mp3,其源极输入电源电压,其栅极与第一pmos管mp1的栅极、第二pmos管mp2的栅极耦接,其漏极与第二nmos电流源的输入端耦接;

131.第四pmos管mp4,其源极输入电源电压,其栅极与第一pmos管mp1的栅极、第二pmos管mp2的栅极、第三pmos管mp3的栅极均耦接,其漏极为pmos电流源的第一输出端。

132.在具体实施中,第一nmos电流源可以包括:第一nmos管mn1、第二nmos管mn2、第一pnp三极管q1、第二pnp三极管q2以及电流电阻r

ptat

,其中:

133.第一nmos管mn1,其栅极与其漏极耦接,其源极与第一pnp三极管q1的发射极耦接,第一nmos管mn1的漏极为第一nmos电流源的输入端;

134.第二nmos管mn2,其栅极与第一nmos管mn1的栅极耦接,其漏极为第一nmos电流源的输出接,其源极与电流电阻r

ptat

的第一端耦接;

135.电流电阻r

ptat

,其第二端与第二pnp三极管q2的发射极耦接;

136.第一pnp三极管q1,其基极与其集电极耦接且均接地;

137.第二pnp三极管q2,其基极与其集电极耦接且均接地。

138.在具体实施中,第二nmos电流源可以包括:第三nmos管mn3以及第四nmos管mn4,其中:

139.第三nmos管mn3,其栅极与其漏极耦接,为第二nmos电流源的输入端,其源极接地;第四nmos管mn4,其栅极与第三nmos管mn3的栅极耦接,其漏极为所述第二nmos电流源的输出端,其源极接地。

140.可以理解的是,pmos电流源的具体结构可以并不仅限于上述示例,nmos电流源的具体结构也可以并不仅限于上述示例。

141.在本发明实施例中,通过对第三可调电阻~第六可调电阻的电阻值以及第一pnp三极管与第二pnp三极管的个数比例进行调整,可以对温漂校准参考电压生成电路17输出的温漂校准参考电压的温漂系数进行调整,进而将温漂校准参考电压的输出频率调整为与温度无关。

142.下面对本发明上述实施例中提供的振荡器的工作原理进行详细说明。

143.温漂校准参考电压v

ref

电压分压比为α,α=vdd/v

ref

。v

ref

电压分压比与rc充放电电路12中的第一可调电阻、第二可调电阻、第一可调电容以及第二可调电容,决定输出的时钟信号的频率。斩波电压平均值反馈电路11中,积分环路的积分电容cx以及积分电阻rx,决定输出的时钟信号的噪声性能。

144.rc充放电电路12可以等效为由v

y

作为控制信号的压控振荡器。

145.根据斩波运算放大器coa的虚短和虚断,对积分环路进行求解可得:

[0146][0147]

对上式(2.1)两边求积分可得:

[0148][0149]

对上式(2.2)化简可得:

[0150][0151]

当振荡器处于稳态时,上式(2.3)中的v

y

(0)决定输出的稳态直流分量,交流分量为0,因此:

[0152][0153]

对上式(2.4)化简可得:

[0154][0155]

当存在以t为周期的周期稳态时,

[0156][0157]

由此,建立了稳态积分周期与温漂校准参考电压的关系。从上式(2.6)中可知,积分环路的稳态积分周期与积分电阻rx的电性参数以及积分电容cx的电性参数无关。

[0158]

由于rc充放电电路12中的第一可调电阻以及第二可调电阻直接输入电源电压,第一可调电容与第二可调电容接地,则有:

[0159]

v

o1,2

(t)=vdd(1

‑

e

‑

t/rc

)

ꢀꢀꢀ

(2.7)在斩波电压平均值反馈电路11中,有

[0160][0161]

将上式(2.7)代入至上式(2.8),化简得到:

[0162][0163]

上式(2.9)中的r指rc充放电电路12中第一可调电阻、第二可调电阻的电阻值,c指rc充放电电路12中的第一可调电容、第二可调电容的电容值。

[0164]

斩波电压平均值反馈电路11实现上式(2.9)中的条件,可以自动调节v

y

以维持稳定的频率输出,从而对电源电压vdd以及传输时延不敏感。在设定分压比之后,可以对第一可调电阻、第一可调电容、第二可调电阻以及第二可调电容的电性参数进行调整,以获取特定的输出频率。

[0165]

如上所述,rc充放电电路12可以等效为一个压控振荡器,定义其频率增益为k

vco

,vn表示斩波运算放大器coa等器件贡献的噪声谱,vx的周期积分等于输入电压vx乘以斩波运算放大器coa的工艺相关的比例系数β。由于斩波运算放大器coa的斩波特性在环路内,其噪声会被其自校准反馈环路所滤除。

[0166]

积分环路的输出噪声为:

[0167][0168]

积分环路的相位噪声为:

[0169][0170]

其中,a为斩波运算放大器coa的增益,s为拉普拉系数,(2.11)中的φ

n

为系统相位噪声谱。

[0171]

零极点如下式:

[0172][0173]

其中,f

z

为第一零点,f

p1

为第一极点,f

p2

为第二极点。

[0174]

积分环路输出噪声的传输特性如图6所示,相位噪声的传输特性如图7所示。图6

中,横坐标为对数频率log(freq),纵坐标为输出噪声传输特性φ

out

/vn。图7中,横坐标为对数频率log(freq),纵坐标为相位噪声传输特性φ

out

/φ

n

。在高频处输出噪声较小。

[0175]

由图6可知,在频率超过第二极点之后,积分环路的输出噪声急剧下降。由图7可知,在频率处于第一零点与第二极点之间时,相位噪声随频率增加。在频率小于第二极点时,相位噪声稳定,在低频处相位噪声较小。

[0176]

参见图8,给出了一种普通运算放大器的输出噪声示意图。参照图9,给出了一种普通斩波运算放大器coa的输出噪声示意图。参照图10,给出了一种包含自校准反馈环路的斩波运算放大器coa的输出噪声示意图。参照图11,给出了本发明实施例中的一种斩波电压平均值反馈电路11的输出噪声示意图。

[0177]

图8~图11中,横坐标为对数频率log(freq),纵坐标为噪声系数nf,f

c

为斩波电压平均值反馈电路的斩波频率。

[0178]

由图8~图11可知,本发明实施例中提供的斩波电压平均值反馈电路的输出噪声无闪烁噪声,且仅包括截止频率为f

p2

的低通热噪声。

[0179]

因此,本发明实施例中提供的斩波电压平均值反馈电路,能够对rc充放电电路12中的低频率的相位噪声进行抑制,可以在第一比较器、第二比较器中使用小尺寸的晶体管以降低功耗。斩波电压平均值反馈电路中,斩波运算放大器coa的闪烁噪声可以被反馈环路所滤除,因此可以选用小尺寸的斩波运算放大器coa来降低电路面积。高频噪声被消除,因此对高频噪声的敏感度较低。

[0180]

虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1