比较器电路及包含其的芯片的制作方法

1.本发明涉及电子技术领域,尤其涉及一种比较器电路及包含其的芯片。

背景技术:

2.比较器电路是集成电路系统的重要模块,广泛应用在各种集成电路系统中。现有的比较器电路,比较器电路的输入电压连接一个晶体管,比较器电路的输入电压必需要大于晶体管的阈值电压比较器电路才能正常输出比较结果,所以,比较器电路的输入电压的最小值要大于晶体管的阈值电压,对于小于晶体管阈值电压的输入电压无法进行比较,导致比较器电路的输入电压范围较小。

技术实现要素:

3.本发明要解决的技术问题是为了克服现有技术中比较器电路连接一个晶体管导致比较器电路的输入电压范围较小的缺陷,提供一种比较器电路及包含其的芯片。

4.本发明是通过下述技术方案来解决上述技术问题:

5.一种比较器电路,包括:放大电路和比较电路;

6.所述放大电路包括第一输入对管、第二输入对管、第三输入对管、第四输入对管、第一放大子电路和第二放大子电路;

7.所述第一输入对管、所述第二输入对管、所述第三输入对管和所述第四输入对管均包括栅极互相连接的一pmos管和一nmos管;

8.所述第一输入对管和所述第四输入对管中nmos管的栅极均用于连接第一输入电压并将所述第一输入电压分别输出至所述第一放大子电路和所述第二放大子电路,所述第二输入对管和所述第三输入对管中nmos管的栅极均用于连接第二输入电压并将所述第二输入电压分别输出至所述第一放大子电路和所述第二放大子电路;

9.所述第一放大子电路用于对所述第一输入电压和所述第二输入电压的差分电压进行增益放大并输出第一放大电压;

10.所述第二放大子电路用于对所述第一输入电压和所述第二输入电压的差分电压进行增益放大并输出第二放大电压;

11.所述比较电路用于将所述第一放大电压和所述第二放大电压进行比较得出与所述第一输入电压和所述第二输入电压相对应的比较结果。

12.较佳地,所述第一输入对管包括第一pmos管和第一nmos管;

13.所述第二输入对管包括第二pmos管和第二nmos管;

14.所述第一放大子电路包括第三nmos管、第四nmos管、第五nmos管、第六nmos管、第七nmos管、第三pmos管、第四pmos管、第五pmos管、第六pmos管、第七pmos管、第八pmos管、第九pmos管、第一开关和第二开关;

15.所述第一nmos管的栅极用于连接所述第一输入电压,所述第二nmos管的栅极用于连接所述第二输入电压,所述第一nmos管的源极与所述第二nmos管的源极和所述第三nmos

管的漏极连接,所述第一nmos管的漏极与所述第四pmos管的漏极、所述第六pmos管的源极和所述第八pmos管的漏极连接;

16.所述第一pmos管的源极与所述第二pmos管的源极和所述第三pmos管的漏极连接,所述第一pmos管的漏极与所述第四nmos管的漏极和所述第六nmos管的源极连接;

17.所述第二nmos管的漏极与所述第七pmos管的源极、所述第九pmos管的漏极和所述第五pmos管的漏极连接;

18.所述第二pmos管的漏极与所述第五nmos管的漏极和所述第七nmos管的源极连接;

19.所述第三nmos管的源极、所述第四nmos管的源极和所述第五nmos管的源极均接地,所述第三nmos管的栅极连接第二开关的固定端,所述第二开关的可动端根据选择信号选择连接外部偏置电压或地;

20.所述第四nmos管的栅极与所述第五nmos管的栅极、所述第六nmos管的漏极和所述第六pmos管的漏极连接;

21.所述第六nmos管的栅极与所述第七nmos管的栅极、所述第六pmos管的栅极和所述第七pmos管的栅极均接外部偏置电压;

22.所述第七nmos管的漏极与所述第七pmos管的漏极连接,所述第七nmos管的漏极用于输出所述第一放大电压;

23.所述第三pmos管的栅极、所述第八pmos管的栅极和所述第九pmos管的栅极均接外部偏置电压,所述第三pmos管的源极、所述第八pmos管的源极和所述第九pmos管的源极均接电源电压;

24.所述第四pmos管的栅极和所述第五pmos管的栅极均与所述第一开关的固定端连接,所述第一开关的可动端基于选择信号选择连接外部偏置电压或电源电压。

25.较佳地,所述第二输入对管包括:第八nmos管和第八pmos管;

26.所述第三输入对管包括:第九nmos管和第九pmos管;

27.所述第二放大子电路包括:第十nmos管、第十一nmos管、第十二nmos管、第十三nmos管、第十四nmos管、第十pmos管、第十一pmos管、第十二pmos管、第十三pmos管、第十四pmos管、第十五pmos管和第十六pmos管;

28.所述第八nmos管的栅极连接所述第二输入电压,所述第九nmos管的栅极连接所述第一输入电压,所述第八nmos管的源极与所述第九nmos管的源极和所述第十nmos管的漏极连接,所述第八nmos管的漏极与所述第十一pmos管的漏极、所述第十三pmos管的源极和所述第十五pmos管的漏极连接;

29.所述第八pmos管的源极与所述第九pmos管的源极和所述第十pmos管的漏极连接,所述第八pmos管的漏极与所述第十一nmos管的漏极和所述第十三nmos管的源极连接;

30.所述第九nmos管的漏极与所述第十四pmos管的源极、所述第十六pmos管的漏极和所述第十二pmos管的漏极连接;

31.所述第九pmos管的漏极与所述第十二nmos管的漏极和所述第十四nmos管的源极连接;

32.所述第十nmos管的源极、所述第十一nmos管的源极和所述第十二nmos管的源极均接地,所述第十nmos管的栅极连接外部偏置电压;

33.所述第十一nmos管的栅极与所述第十二nmos管的栅极、所述第十三nmos管的漏极

和所述第十三pmos管的漏极连接;

34.所述第十三nmos管的栅极与所述第十四nmos管的栅极、所述第十三pmos管的栅极和所述第十四pmos管的栅极均接外部偏置电压;

35.所述第十四nmos管的漏极与所述第十四pmos管的漏极连接,所述第十四nmos管的漏极用于输出所述第二放大电压;

36.所述第十pmos管的栅极、所述第十五pmos管的栅极和所述第十六pmos管的栅极均接外部偏置电压,所述第十pmos管的源极、所述第十五pmos管的源极和所述第十六pmos管的源极均接电源电压;

37.所述第十一pmos管的栅极和所述第十二pmos管的栅极均与外部偏置电压连接;

38.所述第十nmos管的栅极与所述第三nmos管的栅极接相同的偏置电压;

39.所述第四pmos管的栅极、所述第五pmos管的栅极、所述第十一pmos管的栅极和所述第十二pmos管的栅极接相同的偏置电压。

40.较佳地,所述第一输入对管、所述第二输入对管和所述第一放大子电路组成第一放大部分;

41.所述第三输入对管、所述第四输入对管和所述第二放大子电路组成第二放大部分;

42.所述第一放大部分和所述第二放大部分构成折叠共源共栅的结构。

43.较佳地,所述比较电路包括:

44.第三十一nmos管、第三十二nmos管、第三十三nmos管、第三十四nmos管、第三十五nmos管、第三十一pmos管、第三十二pmos管、第三十三pmos管、第三十四pmos管和第一反相器;

45.所述第三十五nmos管的栅极接外部时钟,所述第三十五nmos管的源极接地,所述第三十五nmos管的漏极分别与所述第三十三nmos管的源极和所述第三十四nmos管的源极连接,所述第三十三nmos管的栅极连接所述第二放大电压,所述第三十四nmos管的栅极连接所述第一放大电压,所述第三十三nmos管的漏极与所述第三十一nmos管的源极连接,所述第三十四nmos管的漏极与所述第三十二nmos管的源极连接,所述第三十一pmos管、所述第三十二pmos管、所述第三十三pmos管和所述第三十四pmos管的源极均接电源电压,所述第三十一pmos管的栅极和所述第三十四pmos管的栅极均接外部时钟,所述第三十一pmos管的漏极分别与所述第三十二pmos管的漏极、所述第三十一nmos管的漏极、所述第三十二nmos管的栅极和所述第三十三pmos管的栅极均连接,所述第三十二pmos管的栅极分别与所述第三十一nmos管的栅极、所述第三十三pmos管的漏极、所述第三十二nmos管的漏极和所述第一反相器的输入端均连接,所述第三十四pmos管的漏极与所述第一反相器的输入端连接;

46.所述第一反相器的输出端用于输出所述比较结果。

47.较佳地,所述比较器电路还包括选择信号产生电路;

48.所述选择信号产生电路的第一输入端与所述第一输入电压和所述第二输入电压的共模电压连接,所述选择信号产生电路的第二输入端与固定电压连接;

49.所述选择信号产生电路的输出端与所述放大电路的输入端连接;

50.所述选择信号产生电路用于输出所述选择信号至所述放大电路。

51.较佳地,所述选择信号产生电路包括:第五十三nmos管、第五十四nmos管、第五十五nmos管、第五十六nmos管、第五十七nmos管、第五十八nmos管、第五十一pmos管、第五十二pmos管、第五十三pmos管、第五十四pmos管、第五十五pmos管、第五十六pmos管和第二反相器;

52.第五十三nmos管的栅极连接所述共模电压,所述第五十四nmos管的栅极连接所述固定电压,所述第五十三nmos管、所述第五十四nmos管、所述第五十五nmos管和所述第五十六nmos管的源极均接地,所述第五十一pmos管、所述第五十二pmos管、所述第五十三pmos管、所述第五十四pmos管、所述第五十五pmos管和所述第五十六pmos管的源极均接电源电压,所述第五十三nmos管的漏极分别与所述第五十一pmos管的漏极、所述第五十一pmos管的栅极、所述第五十二pmos管的漏极、所述第五十三pmos管的栅极和所述第五十六nmos管的栅极均连接,所述第五十四nmos管的漏极分别与所述第五十四pmos管的漏极、所述第五十四pmos管的栅极、所述第五十三pmos管的漏极、所述第五十二pmos管的栅极连接,所述第五十五nmos管的漏极与所述第五十七nmos管的源极连接,所述第五十六nmos管的漏极与所述第五十八nmos管的源极连接,所述第五十七nmos管的漏极分别与所述第五十五pmos管的漏极、所述第五十八nmos管的栅极和所述第五十六pmos管的栅极连接,所述第五十七nmos管的栅极分别与所述第五十五pmos管的栅极、所述第五十六pmos管的漏极、所述第五十八nmos管的漏极和所述第二反相器的输入端连接;

53.所述第二反相器的输出端用于输出所述选择信号。

54.较佳地所述选择信号产生电路还包括:第五十一nmos管和第五十二nmos管;

55.所述第五十一nmos管的栅极和所述第五十二nmos管的栅极连接外部偏置电压,所述第五十一nmos管的源极和所述第五十二nmos管的源极连接地,所述第五十一nmos管的漏极分别与所述第五十三nmos管和所述第五十四nmos管的源极连接,所述第五十二nmos管的漏极分别与所述第五十五nmos管和所述第五十六nmos管的源极连接。

56.较佳地,所述固定电压的值大于nmos晶体管的阈值。

57.一种芯片,包括上述任意一项所述的比较器电路。

58.本发明的积极进步效果在于:本发明通过在放大电路中设置第一输入对管、第二输入对管、第三输入对管、第四输入对管,第一输入对管、第二输入对管、第三输入对管和第四输入对管均包括栅极互相连接的一pmos管和一nmos管,第一输入对管和第四输入对管中的pmos管和nmos管的栅极均连接第一输入电压,第二输入对管和第三输入对管中的pmos管和nmos管的栅极均连接第二输入电压,无论比较器输入的电压值为多少,总能保证输入对管中有一个晶体管是导通的,使得比较器电路的输入电压范围可以低至零,扩大了比较器电路的输入电压范围,同时通过第一放大子电路和第二放大子电路对输入的电压信号进行增益放大,可以提高比较器电路的精度。

附图说明

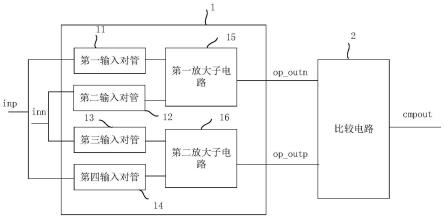

59.图1为本发明实施例1的比较器电路的结构示意图。

60.图2为本发明实施例2的放大电路的电路图。

61.图3为本发明实施例2的比较电路的电路图。

62.图4为本发明实施例2的选择信号产生电路的电路图。

具体实施方式

63.下面通过实施例的方式进一步说明本发明,但并不因此将本发明限制在所述的实施例范围之中。

64.实施例1

65.本实施例提供一种比较器电路,如图1所示,包括:放大电路1和比较电路2。

66.放大电路1包括第一输入对管11、第二输入对管12、第三输入对管13、第四输入对管14、第一放大子电路15和第二放大子电路16。

67.第一输入对管11、第二输入对管12、第三输入对管13和第四输入对管14均包括栅极互相连接的一个pmos管和一个nmos管。

68.第一输入对管11的输出端与第一放大子电路15的第一输入端连接,第二输入对管12的输出端与第一放大子电路15的第二输入端连接,第三输入对管13的输出端与第二放大子电路16的第一输入端连接,第四输入对管14的输出端与第二放大子电路16的第二输入端连接,第一放大子电路15的输出端与比较电路2的第一输入端连接,第二放大子电路16的输出端与比较电路2的第二输入端连接。

69.第一输入对管11和第四输入对管14中的pmos管和nmos管的栅极均用于连接第一输入电压inp,第二输入对管12和第三输入对管13中的pmos管和nmos管的栅极均用于连接第二输入电压inn;

70.第一输入对管11和第四输入对管14用于在第一输入电压inp低于nmos管阈值时导通pmos管并分别输出第一输入电压inp至第一放大子电路15和第二放大子电路16,在第一输入电压inp高于nmos管阈值时导通nmos管并分别输出第一输入电压inp至第一放大子电路15和第二放大子电路16;

71.第二输入对管12和第三输入对管13用于在第二输入电压inn低于nmos管阈值时导通pmos管并分别输出第二输入电压inn至第一放大子电路15和第二放大子电路16,在第二输入电压inn高于nmos管阈值时导通nmos管并分别输出第二输入电压inn至第一放大子电路15和第二放大子电路16;

72.第一放大子电路15用于对第一输入电压inp和第二输入电压inn的差分电压进行增益放大并输出第一放大电压op_outp;

73.第二放大子电路用于对第一输入电压inp和第二输入电压inn的差分电压进行增益放大并输出第二放大电压op_outn;

74.比较电路2用于将第一放大电压op_outp和第二放大电压op_outn进行比较得出与第一输入电压inp和第二输入电压inn相对应的比较结果cmpout。

75.本实施例的比较放大电路通过在输入端设置栅极互相连接的pmos管和nmos管构成的第一输入对管、第二输入对管、第三输入对管和第四输入对管,无论第一输入电压和第二输入电压的值为多少,总有一个晶体管可以导通,使得比较器的输入电压范围可以为(0,vdd),其中vdd是电源电压,扩大了比较器电路的输入电压范围。同时,比较器电路由于使用第一放大子电路和第二放大子电路进行增益放大,可以提高比较器电路的精度。

76.实施例2

77.本实施例提供的一种比较器电路是对实施例1的进一步改进,如图2所示,本实施例的比较器电路中放大电路1中包括第一放大部分101和第二放大部分102,第一放大部分

101包括第一输入对管11、第二输入对管12和第一放大子电路15,第二放大部分102包括第三输入对管13、第四输入对管14和第二放大子电路16。

78.第一输入对管11包括第一pmos管mp1和第一nmos管mn1。

79.第二输入对管12包括第二pmos管mp2和第二nmos管mn2。

80.第一放大子电路15包括第三nmos管mn3、第四nmos管mn4、第五nmos管mn5、第六nmos管mn6、第七nmos管mn7、第三pmos管mp3、第四pmos管mp4、第五pmos管mp5、第六pmos管mp6、第七pmos管mp7、第八pmos管mp8、第九pmos管m9、第一开关k1和第二开关k2。

81.第一nmos管mn1的栅极用于连接第一输入电压inp,第二nmos管mn2的栅极用于连接第二输入电压inn,第一nmos管mn1的源极与第二nmos管mn2的源极和第三nmos管mn3的漏极连接,第一nmos管mn1的漏极与第四pmos管mp4的漏极、第六pmos管mp6的源极和第八pmos管mp8的漏极连接。

82.第一pmos管mp1的源极与第二pmos管mp2的源极和第三pmos管mp3的漏极连接,第一pmos管mp1的漏极与第四nmos管mn4的漏极和第六nmos管mn6的源极连接。

83.第二nmos管mn2的漏极与第七pmos管mp7的源极、第九pmos管mp9的漏极和第五pmos管mp5的漏极连接。

84.第二pmos管mp2的漏极与第五nmos管mn5的漏极和第七nmos管mn7的源极连接。

85.第三nmos管mn3的源极、第四nmos管mn4的源极和第五nmos管mn5的源极均接地vss,第三nmos管mn3的栅极连接第二开关k2的固定端,第二开关k2的可动端连接偏置电压vbnc,偏置电压vbnc根据选择信号sw_ctl选择连接外部偏置电压vbn或地vss。

86.第四nmos管mn4的栅极与第五nmos管mn5的栅极、第六nmos管mn6的漏极和第六pmos管mp6的漏极连接。

87.第六nmos管mn6的栅极与第七nmos管mn7的栅极均接外部偏置电压vbncs,第六pmos管mp6的栅极和第七pmos管mp7的栅极均接外部偏置电压vbpcs。

88.第七nmos管mn7的漏极与第七pmos管mp7的漏极连接,第七nmos管mn7的漏极用于输出第一放大电压op_outp。

89.第三pmos管mp3的栅极、第八pmos管mp8的栅极和第九pmos管mp9的栅极均接外部偏置电压vbp,第三pmos管mp3的源极、第八pmos管mp8的源极和第九pmos管mp9的源极均接电源电压vdd。

90.第四pmos管mp4的栅极和第五pmos管mp5的栅极均与第一开关k1的固定端连接,第一开关k1的可动端连接偏置电压vbpc,偏置电压vbpc基于选择信号sw_ctl选择连接外部偏置电压vbp或电源电压vdd。

91.本实施方式中,第一输入对管11和第二输入对管12同时使用了nmos管和pmos管,以保证无论比较器电路的第一输入电压inp和第二输入电压inn是多少,第一输入对管11和第二输入对管12总能打开。第一开关k1用于基于选择信号sw_ctl来控制第四pmos管mp4的栅极和第五pmos管mp5的栅极接偏置电压vbp或接电源电压vdd,第二开关k2用于基于选择信号sw_ctl来控制第三nmos管的栅极接偏置电压vbn或接地vss。

92.当比较器的输入电压较高时,例如:第一输入电压inp=2v,第二输入电压inn=2v,选择信号sw_ctl=0时,第一nmos管mn1和第二nmos管mn2导通,第一开关k1的可动端接偏置电压vpb使得第四pmos管mp4和第五pmos管mp5导通,第二开关k2的可动端接偏置电压

vpn使得第三nmos管mn3导通,此时,第三晶体管mn3的电流打开,同时第四pmos管mp4和第五pmos管mp5的电流也打开。第六nmos管mn6、第七nmos管mn7均接外部偏置电压vbncs导通,第六pmos管mp6、第七pmos管mp7均接外部偏置电压vbpcs导通,第七nmos管mn7的漏极输出放大后的第一放大电压op_outp。

93.当比较器的输入电压较低时,例如:第一输入电压inp=0.2v,第二输入电压inn=0.2v,选择信号sw_ctl=1时,第一nmos管mn1和第二nmos管mn2关闭,第三pmos管mp3栅极、第八pmos管mp8栅极和第九pmos管mp9栅极接偏置电压vbp导通,第一pmos管mp1和第二pmos管mp2导通,第一开关k1的可动端接电源电压vdd使得第四pmos管mp4和第五pmos管mp5关闭,第二开关k2的可动端接地vss使得第三晶体管mn3关闭,此时第三晶体管mn3的电流关闭,同时第四pmos管mp4和第五pmos管mp5的电流也关闭。第六nmos管mn6、第七nmos管mn7均接外部偏置电压vbncs导通,第六pmos管mp6、第七pmos管mp7均接外部偏置电压vbpcs导通,第七nmos管mn7的漏极输出放大后的第一放大电压op_outp。

94.本实施的第一放大部分101的电路保证了共源共栅级的cascode(共源共栅)管电流与放大器1的第一输入电平inp或第二输入电压inn无关,即无论输入对管打开或者关闭,cascode管的工作状态不变,从而保证了放大器1的增益,降低了设计难度。cascode管由第六nmos管mn6、第七nmos管mn7、第六pmos管mp6、第七pmos管mp7构成。

95.本实施例的第二放大部分102中第三输入对管13包括:第八nmos管mn8和第八pmos管mp8;

96.第四输入对管14包括:第九nmos管mn9和第九pmos管mp9;

97.第二放大子电路16包括:第十nmos管mn10、第十一nmos管mn11、第十二nmos管mn12、第十三nmos管mn13、第十四nmos管mn14、第十pmos管mp10、第十一pmos管mp11、第十二pmos管mp12、第十三pmos管mp13、第十四pmos管mp14、第十五pmos管mp15和第十六pmos管mp16;

98.第八nmos管mn8的栅极连接第二输入电压inn,第九nmos管mn9的栅极连接第一输入电压inp,第八nmos管mn8的源极与第九nmos管mn9的源极和第十nmos管mn10的漏极连接,第八nmos管mn8的漏极与第十一pmos管mp11的漏极、第十三pmos管mp13的源极和第十五pmos管mp15的漏极连接;

99.第八pmos管mp8的源极与第九pmos管mp9的源极和第十pmos管mp10的漏极连接,第八pmos管mp8的漏极与第十一nmos管mn11的漏极和第十三nmos管mn13的源极连接;

100.第九nmos管mn9的漏极与第十四pmos管mp14的源极、第十六pmos管mp16的漏极和第十二pmos管mp12的漏极连接;

101.第九pmos管mp9的漏极与第十二nmos管mn12的漏极和第十四nmos管mn14的源极连接;

102.第十nmos管mn10的源极、第十一nmos管mn11的源极和第十二nmos管mn12的源极均接地vss,第十nmos管mn10的栅极连接外部偏置电压vbnc;

103.第十一nmos管mn11的栅极与第十二nmos管mn12的栅极、第十三nmos管mn13的漏极和第十三pmos管mp13的漏极连接。

104.第十三nmos管mn13的栅极与第十四nmos管mn14的栅极接外部偏置电压vbncs,第十三pmos管mp13的栅极和第十四pmos管mp14的栅极均接外部偏置电压vbpcs。

105.第十四nmos管mn14的漏极与第十四pmos管mp14的漏极连接,第十四nmos管mn14的漏极用于输出第二放大电压op_outn。

106.第十pmos管mp10的栅极、第十五pmos管mp15的栅极和第十六pmos管mp16的栅极均接外部偏置电压vbp,第十pmos管mp10的源极、第十五pmos管mp15的源极和第十六pmos管mp16的源极均接电源电压vdd。

107.第十一pmos管mp11的栅极和第十二pmos管mp12的栅极均与外部偏置电压vbpc连接;

108.第十nmos管mn10的栅极与第三nmos管mn3的栅极接相同的偏置电压vbnc;

109.第四pmos管mp4的栅极、第五pmos管mp5的栅极、第十一pmos管mp11的栅极和第十二pmos管mp12的栅极接相同的偏置电压vbpc。

110.本实施方式中,第三输入对管13和第四输入对管14同时使用了nmos管和pmos管,以保证无论比较器电路的第一输入电压inp和第二输入电压inn是多少,第三输入对管13和第四输入对管14总能打开。当比较器的输入电压较高时,例如:第一输入电压inp=2v,第二输入电压inn=2v,第八nmos管mn8和第九nmos管mn9导通,第十pmos管mp10的栅极、第十五pmos管mp15的栅极和第十六pmos管mp16的栅极均接偏置电压vbp导通,第十一pmos管mp11的栅极和第十二pmos管mp12的栅极接的偏置电压vbpc与偏置电压vbp连接,所以第十一pmos管mp11和第十二pmos管mp12导通,第十nmos管mn10的栅极接的偏置电压vbnc接偏置电压vbn,所以第十nmos管mn10导通,此时,第十晶体管mn10的电流打开,同时第十一pmos管mp11和第十二pmos管mp12的电流也打开。第十三nmos管mn13、第十四nmos管mn4均接外部偏置电压vbncs导通,第十三pmos管mp13、第十四pmos管mp14均接外部偏置电压vbpcs导通,第十四nmos管mn14的漏极输出放大后的第二放大电压op_outn。

111.当比较器的输入电压较低时,例如:第一输入电压inp=0.2v,第二输入电压inn=0.2v,第八nmos管mn8和第九nmos管mn9关闭,第八pmos管mp8和第九pmos管mp9导通,第十pmos管mp10的栅极、第十五pmos管mp15的栅极和第十六pmos管mp16的栅极均接偏置电压vbp导通,第十一pmos管mp11的栅极和第十二pmos管mp12的栅极接的偏置电压vbpc与电源电压vdd连接,所以第十一pmos管mp11和第十二pmos管mp12关闭,第十nmos管mn10栅极接的偏置电压vbnc与地vss连接,所以第十nmos管mn10关闭,此时,第十晶体管mn10的电流关闭,同时第十一pmos管mp11和第十二pmos管mp12的电流也关闭。第十三nmos管mn13、第十四nmos管mn4均接外部偏置电压vbncs导通,第十三pmos管mp13、第十四pmos管mp14均接外部偏置电压vbpcs导通,第十四nmos管mn14的漏极输出放大后的第二放大电压op_outn。

112.本实施的第二放大部分102的电路保证了共源共栅级的cascode(共源共栅)管电流与放大器1的第一输入电平inp或第二输入电压inn无关,即无论输入对管打开或者关闭,cascode管的工作状态不变,从而保证了放大器1的增益,降低了设计难度。cascode管由第十三nmos管mn13、第十四nmos管mn14、第十三pmos管mp13、第十四pmos管mp14构成。

113.本实施放大器电路中,第一放大部分101和第二放大部分102构成一个折叠共源共栅的结构,使得放大电路1可以得到较大的增益。

114.如图3所示,本实施例的比较电路2包括:第三十一nmos管mn31、第三十二nmos管mn32、第三十三nmos管mn33、第三十四nmos管mn34、第三十五nmos管mn35、第三十一pmos管mp31、第三十二pmos管mp32、第三十三pmos管mp33、第三十四pmos管mp34和第一反相器

inv1;

115.第三十五nmos管mn35的栅极接外部时钟clk,第三十五nmos管mn35的源极接地vss,第三十五nmos管mn35的漏极分别与第三十三nmos管mn33的源极和第三十四nmos管mn34的源极连接,第三十三nmos管mn33的栅极用于连接第二放大电压op_outn第三十四nmos管mn34的栅极用于连接第一放大电压op_outp,第三十三nmos管mn33的漏极与第三十一nmos管mn31的源极连接,第三十四nmos管mn34的漏极与第三十二nmos管mn32的源极连接,第三十一pmos管mp31、第三十二pmos管mp32、第三十三pmos管mp33和第三十四pmos管mp34的源极均接电源电压vdd,第三十一pmos管mp31的栅极和第三十四pmos管mp34的栅极均接外部时钟clk,第三十一pmos管mp31的漏极分别与第三十二pmos管mp32的漏极、第三十一nmos管mn31的漏极、第三十二nmos管mn32的栅极和第三十三pmos管mp33的栅极均连接,第三十二pmos管mp32的栅极分别与第三十一nmos管mn31的栅极、第三十三pmos管mp33的漏极、第三十二nmos管mn32的漏极和第一反相器inv1的输入端均连接,第三十四pmos管mp34的漏极与第一反相器inv1的输入端连接;

116.第一反相器inv1的输出端用于输出比较结果cmpout。

117.在时钟信号clk的上升沿,第三十五nmos管mn35、第三十一pmos管mp31和第三十四pmos管mp34导通,当第一输入电压inp大于第二输入电压inn时,对应的比较电路的2输入电压第一放大电压op_outp大于第二放大电压op_outn,第三十三nmos管mn33的栅极连接经放大后的第二放大电压op_outn导通,第三十四nmos管mn34的栅极连接经放大后的第一放大电压op_outp导通,第三十一nmos管mn31、第三十二nmos管mn32、第三十一pmos管mp31、第三十二pmos管mp32、第三十三pmos管mp33和第三十四pmos管mp34构成比较器,当第一放大电压op_outp大于第二放大电压op_outn,第一反相器inv1输出的比较结果cmpout的值为1。同时,在时钟信号clk的上升沿,第一比较电路cmp1还用于快速锁存比较器电路的比较结果cmpout。当时钟信号clk=0时,第一比较电路cmp1进行复位操作。

118.同理,当第一输入电压inp小于第二输入电压inn时,对应的比较电路的2输入电压第一放大电压op_outp小于第二放大电压op_outn,第一反相器inv1输出的比较结果cmpout的值为0。

119.在可选的另一实施方式中,比较器电路还包括选择信号产生电路;如图4所示,选择信号产生电路的第一输入端与第一输入电压inp和第二输入电压inn的共模电压incm连接,选择信号产生电路的第二输入端与固定电压vth_amp连接,固定电压vth_amp的值稍大于选择信号产生电路中nmos晶体管的阈值以使得第一输入电压inp和第二输入电压inn的均值大于nmos晶体管的阈值时对应的晶体管电流开启,此时vth_amp作为产生选择信号sw_ctl,应当与nmos晶体管的阈值电压相当。

120.选择信号产生电路的输出端与放大电路1的输入端连接。

121.选择信号产生电路用于输出选择信号sw_ctl至放大电路1。

122.本实施例的选择信号产生电路包括:第五十一nmos管mn51和第五十二nmos管mn52、第五十三nmos管mn53、第五十四nmos管mn54、第五十五nmos管mn55、第五十六nmos管mn56、第五十七nmos管mn57、第五十八nmos管mn58、第五十一pmos管mp51、第五十二pmos管mp52、第五十三pmos管mp53、第五十四pmos管mp54、第五十五pmos管mp55、第五十六pmos管mp56和第二反相器inv2;

123.第五十一nmos管mn51的栅极和第五十二nmos管mn52的栅极连接外部偏置电压vbn,第五十一nmos管mn51的源极和第五十二nmos管mn52的源极连接地,第五十一nmos管mn51的漏极分别与第五十三nmos管mn53和第五十四nmos管mn54的源极连接,第五十二nmos管mn52的漏极分别与第五十五nmos管mn55和第五十六nmos管mn56的源极连接;第五十三nmos管mn53的栅极连接共模电压incm,第五十四nmos管mn54的栅极连接固定电压vth_amp,第五十一pmos管mp51、第五十二pmos管mp52、第五十三pmos管mp53、第五十四pmos管mp54、第五十五pmos管mp55和第五十六pmos管mp56的源极均接电源电压vdd,第五十三nmos管mn53的漏极分别与第五十一pmos管mp51的漏极、第五十一pmos管mp51的栅极、第五十二pmos管mp52的漏极、第五十三pmos管mp53的栅极和第五十六nmos管mn56的栅极均连接,第五十四nmos管mn54的漏极分别与第五十四pmos管mp54的漏极、第五十四pmos管mp54的栅极、第五十三pmos管mp53的漏极、第五十二pmos管mp52的栅极连接,第五十五nmos管mn55的漏极与第五十七nmos管mn57的源极连接,第五十六nmos管mn56的漏极与第五十八nmos管mn58的源极连接,第五十七nmos管mn57的漏极分别与第五十五pmos管mp55的漏极、第五十八nmos管mn58的栅极和第五十六pmos管mp56的栅极连接,第五十七nmos管mn57的栅极分别与第五十五pmos管mp55的栅极、第五十六pmos管mp56的漏极、第五十八nmos管mn58的漏极和第二反相器inv2的输入端连接;第二反相器inv2的输出端用于输出选择信号sw_ctl。

124.本实施例的选择信号产生电路中第五十四nmos管mn54的栅极连接固定电压vth_amp,固定电压vth_amp值接近并稍大于nmos管的阈值电压,第五十四nmos管mn54恒导通。当第一输入电压inp和第二输入电压inn为低电压时,如第一输入电压inp=0.2v,第二输入电压inn=0.2v,共模电压incm=(inp+inn)/2=0.2v,假设nmos管的阈值电压是0.5v,vth_amp选值为0.55v。由于共模电压incm小于vth_amp,此时,第五十三nmos管mn53关闭,第五十一nmos管mn51和第五十二nmos管mn52接外部偏置电压vbn导通。由于,第五十三nmos管mn53关闭导致选择信号产生电路输出高电平信号作为选择信号sw_ctl。

125.当第一输入电压inp和第二输入电压inn为高电压时,如第一输入电压inp=2v,第二输入电压inn=2v,共模电压incm=(inp+inn)/2=2v,假设nmos管的阈值电压是0.5v,vth_amp选值为0.55v,由于共模电压incm大于vth_amp,此时,第五十三nmos管mn53导通,第五十一nmos管mn51和第五十二nmos管mn52接外部偏置电压vbn导通。由于,第五十三nmos管mn53导通导致选择信号产生电路输出低电平信号作为选择信号sw_ctl。

126.本实施例的比较器电路的工作原理是:当第一输入电压inp和第二输入电压inn为高电压时,第一nmos管mn1、第二nmos管mn2、第八nmos管mn8和第九nmos管mn9导通,选择信号产生电路输出低电平信号作为选择信号sw_ctl=0,放大电路1中第一开关k1的可动端接偏置电压vpb使得第四pmos管mp4、第五pmos管mp5、第十一pmos管mp11和第十二pmos管mp12导通,第二开关k2的可动端接偏置电压vpn使得第三nmos管mn3和第十nmos管mn10导通,第七nmos管mn7的漏极输出放大后的第二放大电压op_outn,第十四nmos管mn14的漏极输出放大后的第二放大电压op_outn。

127.当第一输入电压inp和第二输入电压inn为低电压时,第一pmos管mp1、第二pmos管mp2、第八pmos管mp8和第九pmos管mp9导通,选择信号产生电路输出高电平信号作为选择信号sw_ctl=1,第一开关k1的可动端接电源电压vdd使得第四pmos管mp4、第五pmos管mp5、第十一pmos管mp11和第十二pmos管mp12关闭,第二开关k2的可动端接地vss使得第三晶体管

mn3和第十晶体管mn10关闭。第七nmos管mn7的漏极输出放大后的第一放大电压op_outp。第十四nmos管mn14的漏极输出放大后的第二放大电压op_outn。

128.本实施例的比较器电路通过选择信号产生电路根据第一输入电压和第二输入电压的共模电压产生选择信号至放电电路,控制放大电路中的第一开关和第二开关导通对应的晶体管,使得放大电路中的共源共栅级的cascode管电流与放大器的第一输入电平或第二输入电压无关,cascode管的工作状态不变,从而保证了放大器的增益,降低了设计难度。

129.实施例3

130.本实施例提供一种芯片,该芯片包括实施例1或实施例2中的比较器电路。

131.比较器放大电路通过在放大电路中设置第一输入对管、第二输入对管、第三输入对管、第四输入对管,第一输入对管、第二输入对管、第三输入对管和第四输入对管均包括栅极互相连接的一pmos管和一nmos管,第一输入对管和第四输入对管中的pmos管和nmos管的栅极均连接第一输入电压,第二输入对管和第三输入对管中的pmos管和nmos管的栅极均连接第二输入电压,无论比较器输入的电压值为多少,总能保证输入对管中有一个晶体管是导通的,使得比较器电路的输入电压范围可以低至零,扩大了比较器电路的输入电压范围,同时通过第一放大子电路和第二放大子电路对输入的电压信号进行增益放大,可以提高比较器电路的精度。

132.本实施例的芯片,芯片输入电压范围可以低至零,扩大了输入电压的范围,同时对输入的电压信号进行增益放大,可以提高芯片的精度。

133.虽然以上描述了本发明的具体实施方式,但是本领域的技术人员应当理解,这仅是举例说明,本发明的保护范围是由所附权利要求书限定的。本领域的技术人员在不背离本发明的原理和实质的前提下,可以对这些实施方式做出多种变更或修改,但这些变更和修改均落入本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1