一种用于小数分频锁相环中全集成片上数控晶体振荡器的制作方法

1.本实用新型涉及电子技术领域,具体涉及一种用于小数分频锁相环中全集成片上数控晶体振荡器。

背景技术:

2.gps,wlan,gsm/gprs,cdma等的迅猛发展,使射频通讯系统对长期、短期频率稳定度俱佳的高性能晶体振荡器的需求迅猛攀升,温度补偿晶体振荡器(tcxo)的出现成为了手机等便携通讯终端射频电路中的关键器件之一,其中含压控频率校正功能的压控式温度补偿晶振(vc

‑

tcxo)可配合自动频率控制(afc)信号,根据高精度基站时钟脉冲自动在终端进行频偏校准,具备十分优良的长、短期频率稳定性,但缺点是价格昂贵,成本比较大,无法做到全片内集成。

技术实现要素:

3.本实用新型目的在于克服现有技术的不足,提供一种用于小数分频锁相环中全集成片上数控晶体振荡器(dcxo)。

4.为了实现上述目的,本实用新型采取的技术方案如下:

5.一种用于小数分频锁相环中全集成片上数控晶体振荡器,包括晶体振荡核心电路、限幅放大电路、晶振buffer电路、开关电容阵列电路、电压转电流buffer电路;

6.晶体振荡核心电路与开关电容阵列电路的输出端与外置晶体连接,开关电容阵列电路作为开关电路,接收自动频率控制信号,从而控制外部晶体与晶体振荡核心电路的导通;

7.晶体振荡核心电路输出端连接到限幅放大电路输入端,晶体振荡核心电路输入端连接到限幅放大电路输出端;限幅放大电路用于限制晶体振荡核心电路输出的输出电平,同时提供一个比较大的起振电流,使得晶振能够快速起振;

8.晶振buffer电路输入端与晶体振荡核心电路输出端连接,晶振buffer电路对晶振输出信号的缓冲和整形,晶振buffer电路输出端输出方波信号;

9.电压转电流buffer电路与限幅放大电路输入端连接,低温漂系数的基准电压vref通过电压转电流buffer电路产生低温度系数的电流输出给限幅放大电路,用来减小温度变化对振荡频率的影响。

10.作为一种优选技术方案,晶体振荡核心电路包括晶体振荡核心电路包括振荡管m0、mos 管m1、mos管m2、mos管m3、电阻r1、电容c1、电容c2;振荡管m0的漏极与mos 管m1的漏极、电阻r1的一端、电容c2的一端连接,且mos管m1的漏极作为outn端连接外置晶体;振荡管m0的栅极连接有电阻r1的另一端、电容c1的一端,并作为晶体振荡核心电路输出端outp连接外置晶体、晶振buffer电路、限幅放大电路;晶振管m0的源极连接到电容c1的另一端、电容c2的另一端、mos管m3的源极、接地;

11.mos管m1的栅极连接mos管m8的漏极、mos管m2的栅极、mos管m2的漏极、 mos管m3的

漏极;

12.mos管m1的源极连接到mos管m8的源极、mos管m2的源极;

13.mos管m8的栅极作为pdn端,接收主控芯片的powerdown信号;mos管m3的栅极作为晶体振荡核心电路输入端与限幅放大电路输出端连接。

14.作为一种优选技术方案,限幅放大电路包括mos管m4、mos管m5、电阻r3、电容 c3、电容c4、电容c5、电容c6;mos管m4的栅极连接电阻r3的一端、电容c4的一端、电容c3的一端;电容c3的另一端作为限幅放大电路的输入端与晶体振荡核心电路连接; mos管m4的漏极连接到mos管m3的栅极、mos管m5的漏极、mos管m17的漏极、电阻r3的另一端、电容c5的一端、电容c6的一端、且作为限幅放大电路的输出端连接到晶体振荡核心电路的输入端;

15.电容c4的另一端、电容c5的另一端、电容c6的另一端、mos管m4的源极、mos 管m17的源极接地;

16.mos管m17的的栅极作为pdp端,接收主控芯片的powerdown信号,当芯片正常工作时,mos管m17关闭,当芯片不工作时,mos管m17导通;

17.mos管m5的源极连接mos管m7的源极、mos管m2的源极、mos管m12的源极; mos管m5的栅极连接到mos管m12的栅极、mos管m12的漏极、mos管m7的漏极;

18.mos管m12的漏极作为连接端与电压转电流buffer电路,接收电压转电流buffer电路的偏置电流。

19.作为一种优选技术方案,晶振buffer电路为反相器级联形成的晶振buffer电路;在第一级反相器输入端与输出端之间串联电阻r2。

20.作为一种优选技术方案,晶振buffer电路为三级反相器级联形成的晶振buffer电路。

21.作为一种优选技术方案,第一级反相器包括p沟道mos管m10和n沟道mos管m11;第二级反相器包括n沟道mos管m18和p沟道mos管m19;第三级反相器包括p沟道 mos管m20和n沟道mos管m6;

22.mos管m10的栅极连接电阻r2的一端、mos管m11的栅极、电容c7的另一端,电容c7的一端作为晶振buffer电路的输入端与晶体振荡核心电路的输出端连接;mos管m10 的漏极连接电阻r2的另一端、mos管m11的漏极、mos管m19的栅极、mos管m18的栅极;mos管m10的源极连接mos管m19的源极、mos管m9的漏极;mos管m11的源极连接到mos管m18的源极,mos管m18的漏极连接到mos管m19的漏极、mos管 m6的栅极、mos管m20的栅极;mos管m6的漏极连接到mos管20的漏极,mos管 m6的漏极作为晶振buffer电路输出端;

23.mos管m9的栅极作为pdp端,接收主控芯片的powerdown信号,当芯片正常工作时,mos管m9导通。当芯片不工作时,mos管m9关闭。

24.作为一种优选技术方案,电压转电流buffer电路包括mos管m21,mos管m21的漏极连接到mos管m21的栅极、mos管m26的栅极,mos管m21的漏极作为iref端输入基准电流;mos管m21的源极连接到mos管m26的源极、电阻r5的一端、mos管m29的源极、mos管30的源极。mos管m26的漏极连接到mos管m24的源极、mos管m25 的源极;mos管m24的栅极连接到电阻r5的另一端,电容c12的一端、mos管m27的漏极;mos管m24的漏极连接到mos管m22的漏极、mos管m22的栅极、mos管m23的栅极;mos管m22的源极连接到mos管m23的源极、mos管m27的源极、mos管m28 的源极;mos管m23的漏极连接到mos管m25的漏极、mos管m27的栅极、mos管 m28的

栅极、电阻r4的一端;电阻r4的另一端与电容c12的另一端连接;mos管m25的栅极作为vref端输入基准电压。

25.mos管m28的漏极连接mos管m29的漏极、mos管m29的栅极、mos管m30的栅极。mos管m30的漏极作为电压转电流buffer电路输出端连接到限幅放大电路。

26.本实用新型中,把vc

‑

tcxo的功能变成片上模块,将石英晶体以外的所有器件整合到片内,并用数控电容阵列取代模拟变容管,用afc信号直接调频,这样就降低了用料与成本,使射频收发系统单芯片化。由于全集成的片上数控晶体振荡器(dcxo)借助射频基站发送的频率校正信号而产生的自动频率控制信号直接控制电容阵列,克服频率随温度和时间的漂移,同时满足系统对频率精度的要求。因此,dcxo以其易集成和低成本具有替代昂贵的压控式温度补偿晶振的巨大市场潜力。

附图说明

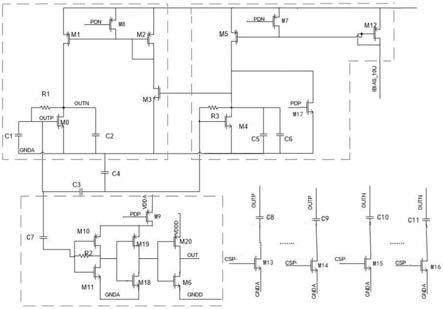

27.图1为本实用新型的电路原理图。

28.图2为电压转电流buffer电路的电路原理图。

具体实施方式

29.本实用新型的目的在于克服现有技术的缺陷,提供一种用于小数分频锁相环中全集成片上数控晶体振荡器,下面结合实施例对本实用新型作进一步详细说明。

30.实施例1

31.如图1~2所示,一种用于小数分频锁相环中全集成片上数控晶体振荡器,包括晶体振荡核心电路、限幅放大电路、晶振buffer电路、开关电容阵列电路、电压转电流buffer电路。

32.其中,晶体振荡核心电路与开关电容阵列电路的输出端与外置晶体连接,开关电容阵列电路作为开关电路,控制电路的导通。

33.晶体振荡核心电路连接有限幅放大电路,限幅放大电路用于稳定晶振输出的振荡幅度,从而减小晶振稳定输出后的平均功耗,同时提供一个比较大的起振电流,使得晶振能够快速起振。

34.晶振buffer电路与晶体振荡核心电路连接,完成对晶振输出信号的缓冲和整形,产生方波信号用于驱动后级的参考频率分频电路和pfd电路。

35.晶体振荡核心电路包括振荡管m0、mos管m1、mos管m2、mos管m3、电阻r1、电容c1、电容c2;振荡管m0的漏极与mos管m1的漏极、电阻r1的一端、电容c2的一端连接,且mos管m1的漏极作为电信号输出端outn连接外置晶体。振荡管m0的栅极连接有电阻r1的另一端、电容c1的一端、电容c3的一端、电容c7的一端;晶振管m0 的栅极还作为电信号输出端outp与外置晶振连接。晶振管m0的源极连接到电容c1的另一端、电容c2的另一端、电容c4的一端、mos管m3的源极、mos管m4的源极、电容 c5的一端、电容c6的一端、mos管m17的源极。

36.mos管m1的源极连接到mos管m8的源极、mos管m2的源极、mos管m5的源极、 mos管m7的源极、mos管m12的源极。

37.mos管m1的栅极连接mos管m8的漏极、mos管m2的栅极、mos管m2的漏极、 mos管m3的漏极。mos管m8的栅极作为pdn端,接收主控芯片的powerdown信号,当芯片正常工作时,mos

管m8关闭。当芯片不工作时,mos管m8导通。

38.限幅放大电路包括mos管m4、mos管m5、电阻r3、电容c3、电容c4、电容c5、电容c6,mos管m4的栅极连接电阻r3的一端、电容c4的另一端、电容c3的另一端; mos管m4的漏极连接到mos管m3的栅极、mos管m5的漏极、mos管m17的漏极、电阻r3的另一端、电容c5的另一端、电容c6的另一端。mos管m17的的栅极作为pdp 端,接收主控芯片的powerdown信号,当芯片正常工作时,mos管m17关闭。当芯片不工作时,mos管m17导通。

39.晶振buffer电路包括mos管m10、mos管m11、mos管m6、mos管m18、mos管 m19、mos管m20、mos管m9。mos管m10的栅极连接电阻r2的一端、mos管m11 的栅极、电容c7的另一端。mos管m10的漏极连接电阻r2的另一端、mos管m11的漏极、mos管m19的栅极、mos管m18的栅极。mos管m10的源极连接mos管m19的源极、mos管m9的漏极。mos管m11的源极连接到mos管m18的源极,mos管m18的漏极连接到mos管m19的漏极、mos管m6的栅极、mos管m20的栅极。mos管m6的漏极连接到mos管20的漏极,mos管m6的漏极作为out端,连接后级的参考频率分频电路和pfd电路。

40.mos管m9的栅极作为pdp端,接收主控芯片的powerdown信号,当芯片正常工作时,mos管m9导通。当芯片不工作时,mos管m9关闭。

41.开关电容阵列电路包括mos管m13、mos管m14、mos管m15、mos管m16;mos 管m13的漏极连接电容c8的一端,电容c8的另一端作为outp端连接到外置晶振。mos 管m14的漏极连接电容c9的一端,电容c9的另一端作为outp端连接到外置晶振。mos 管m15的漏极连接电容c10的一端,电容c10的另一端作为outn端连接到外置晶振。mos 管m16的漏极连接电容c11的一端,电容c11的另一端作为outn端连接到外置晶振。

42.mos管m13、mos管m14、mos管m15、mos管m16的源极皆作为gnda端接地, mos管m13、mos管m14、mos管m15、mos管m16的栅极皆作为csp端,接入自动频率控制信号,给mos管m13、mos管m14、mos管m15、mos管m16高电位,mos 管m13、mos管m14、mos管m15、mos管m16导通。

43.电压转电流buffer电路包括mos管m21,mos管m21的漏极连接到mos管m21的栅极、mos管m26的栅极,mos管m21的漏极作为iref端输出基准电流。mos管m21的源极连接到mos管m26的源极、电阻r5的一端、mos管m29的源极、mos管30的源极。 mos管m26的漏极连接到mos管m24的源极、mos管m25的源极;mos管m24的栅极连接到电阻r5的另一端,电容c12的一端、mos管m27的漏极。mos管m24的漏极连接到mos管m22的漏极、mos管m22的栅极、mos管m23的栅极。mos管m22的源极连接到mos管m23的源极、mos管m27的源极、mos管m28的源极。mos管m23的漏极连接到mos管m25的漏极、mos管m27的栅极、mos管m28的栅极、电阻r4的一端。电阻r4的另一端与电容c12的另一端连接。mos管m25的栅极作为vref端输入基准电压。

44.mos管m28的漏极连接mos管m29的漏极、mos管m29的栅极、mos管m30的栅极。mos管m30的漏极作为输出端连接到mos管m12的漏极、mos管m12的栅极、mos 管m5的栅极、mos管m7的漏极。mos管m7的栅极作为pdn端,接收主控芯片的powerdown信号,当芯片正常工作时,mos管m7关闭。当芯片不工作时,mos管m7导通。

45.本实施例的工作原理为:振荡管m0、mos管m1、mos管m2、mos管m3、电阻r1、电容c1、电容c2构成晶体振荡核心电路,c1,c2为晶体的负载电容,其值通常由生产晶体的厂家提供,电容值越大,频率牵引因子越小,振荡频率的精度越高稳定性越好,但负载电容越大,起振时间越长,起振所需要的起振跨导也越大,相应的功耗也越大;电阻r1为振荡管m0提供直

流偏置,所以其取值要大,同时大的电阻取值也可以避免晶体两端的品质因素的减小(outp,outn两端用来接外置晶体);晶体振荡器起振时m0所需要的跨导值可根据经验值设定,也可以参考相关论文提供的公式。

46.mos管m4,mos管m5,mos管m12,电阻r3,电容c3,电容c4,电容c5,电容 c6构成限幅放大电路,随着outp端输出电压信号的不断增大,电容c3,电容c4构成交流分压电路,从而outp输出电压信号的幅值变化被mos管m4管的栅极检测到,mos管m4管的漏级电流随之越来越大,直到大于mos管m5的漏极电流;电容c5、电容c6开始放电使mos管m4的漏级电压不断减小。进而mos管m3,mos管m2,mos管m1管的漏级电流也在不断减小直至最终达到一个动态平衡,限幅放大电路的目的是用来稳定晶振输出的振荡幅度,从而减小晶振稳定输出后的平均功耗,同时提供一个比较大的起振电流,使得晶振能够快速起振。

47.mos管m10,mos管m11,mos管m18,mos管m19,mos管m6,mos管m20,电阻r2,电容c7构成了晶振buffer电路,完成对晶振输出信号的缓冲和整形,产生方波信号用于驱动后级的参考频率分频电路和pfd电路,该buffer电路采用反相器级联来实现,在 mos管m10和mos管m11组成的第一级反相器输入输出之间串联极大的电阻r2(大于 100k)以提供直流偏置点,使其工作在类似推挽放大的状态。由于mos管m10和mos管 m11尺寸对参考缓冲电路近端相位噪声恶化较为明显,在实际电路设计过程中应选取较大沟道长度和较宽晶体管长度,同时也要兼顾功耗。后级级联反相器对波形进行整形,使其输出为方波信号。

48.开关电容阵列电路,电容阵列位数为13位,afc频率调节范围

±

70ppm。

49.电压转电流buffer电路如图2所示,ibias_10u偏置电流为低温度系数电流,低温漂系数的基准电压vref(通常由带隙基准电压产生)通过v

‑

ibuffer(电压转电流buffer电路电阻 r5为低温度系数电阻)产生低温度系数的电流ibias_10u,用来减小温度变化对振荡频率的影响。iref给一个基准电流过来,经过mos管m22~m27,r5构成的运算放大电路,增益比较高的情况下,vref为同相端,m24作为反相端,增益比较高时,同相端和反相端电位差不多,说明电阻r5上电位和vref端相等,电压一致,得到偏置电流通过输出端输出给限幅放大电路。

50.按照上述实施例,便可很好地实现本实用新型。值得说明的是,基于上述结构设计的前提下,为解决同样的技术问题,即使在本实用新型上做出的一些无实质性的改动或润色,所采用的技术方案的实质仍然与本实用新型一样,故其也应当在本实用新型的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1