延迟电路的制作方法

1.本实用新型涉及存储器技术领域,具体涉及一种延迟电路。

背景技术:

2.当存储器连接至控制器,为了确保控制器可以正常访问存储器,需要对控制器的时钟信号进行校准,否则所述存储器则无法接收到所述控制器发送的正确的数据,所述控制器也无法从所述存储器读取到正确的数据。请参阅图1,存储器输出读数据(dq信号)的时间校准由参数twck2ck和twck2dqo来决定,twck2ck和twck2dqo是gddr6说明书上定义的两个参数,其中,twck2ck表示控制器的时钟信号wck和存储器的时钟信号ck的偏差,twck2dqo表示控制器的时钟信号wck到dq输出的延迟,在对控制器的时钟信号进行校准过程中,需对控制器的时钟信号进行延迟,然而,现有延迟电路一般容易出现延迟偏差。

技术实现要素:

3.本实用新型的目的是提供一种校准方法及装置,本实用新型的目的是提供一种延迟电路,不容易出现延迟偏差。

4.本实用新型实施例提供一种所述延迟电路,所述延迟电路包括:

5.选择单元,所述选择单元包括4路选择器,每路选择器接收1路4相位的分频时钟信号及选择控制信号,所述分频时钟信号的时钟周期为t0,所述每个选择器根据所述选择控制信号分别选择输出其中1路的分频时钟信号;以及

6.延迟单元,所述延迟单元包括4路延迟器,每个所述延迟器接收所述选择单元的输出的2路不同的分频时钟信号及延迟控制信号,每个所述延迟器根据所述延迟控制信号分别选择输入1路4相位的分频时钟信号,使得所述延迟单元输出所述延迟信号,所述延迟信号与所述时钟信号之间的延迟为(n*a*t0)/4q,其中,n为选择单元的延迟参数,1≤n≤4,且n为自然数,a由所述延迟控制信号确定,q由所述延迟器确定,且1<a<q,a、q为自然数。

7.可选的,每个延迟器包括结构相同的第一延迟子单元、第二延迟子单元及反相器,所述第一延迟子单元及所述第二延迟子单元用于根据延迟信号选择1路分频时钟信号,通过所述反相器输出,每个第一延迟子单元或者每个第二延迟子单元包括q个开关组合。

8.可选的,每个第一延迟子单元及每个第二延迟子单元分别包括32个开关组合,所述延迟信号与所述时钟信号之间的延迟为(n*a*t0)/128。

9.可选的,每个开关组合包括第一开关元件、第二开关元件、第三开关元件及第四开关元件,所述第一开关元件的第一端连接第一工作电压,第二端连接第二开关元件的第一端,第三端输入所述分频时钟信号;所述第二开关的第二端输入所述延迟信号,所述第二开关的第三端连接所述反相器的输入端;所述第三开关元件的第一端连接第二工作电压,第二端连接第四开关元件的第一端,第三端输入所述分频时钟信号;所述第四开关的第二端输入所述延迟信号,所述第四开关的第三端连接所述反相器的输入端。

10.可选的,所述第一开关元件及所述第二开关元件为pmos管,所述第三开关元件及

所述第四开关元件为nmos管。

11.本实用新型与现有技术相比,具有如下的优点和有益效果:

12.本实用新型实施例所述延迟电路的输出时钟是由输入时钟clk_000/clk_090/clk_180/clk_270插值产生的,可减少输入时钟clk_000/clk_090/clk_180/clk_270之间的延迟偏差,且延迟电路的延迟时间是基于时钟周期的,因此,不容易随电压、温度和工艺变化而变化,另外,所述延迟单元的最小精度为128分之一的时钟周期,且和电压、温度及工艺无关。

附图说明

13.为了更清楚地说明本说明书实施例或现有技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本说明书的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

14.图1是现有技术中存储器输出读数据的时序图。

15.图2是本实用新型实施例提供的一种校准方法的流程图。

16.图3是本实用新型实施例提供的一种计数电路的电路图。

17.图4是本实用新型另一个实施例提供的一种校准方法中周期校准的流程图。

18.图5及图6是本实用新型另一个实施例提供的一种校准方法中粗校准及细校准的流程图。

19.图7是本实用新型实施例提供的一种存储器的时序校准装置的模块图。

20.图8是本实用新型实施例提供的一种延迟电路的电路图。

21.图9是图7所示的延迟电路的延迟器的电路图。

22.图10是图8所示的延迟器的等效电路图。

23.图11是图8所示的延迟器的开关单元的电路图。

24.图12至图15是图8所示的延迟电路的输出的时钟信号的时序图。

具体实施方式

25.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整的描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例,基于本实用新型实施例,本领域普通技术人员所获得的所有其他实施例,都属于本实用新型实施例保护的范围。

26.请参阅图2,图2为本实用新型实施例提供的一种校准方法的流程图。所述校准方法用于对连接至存储器的控制器进行时序校准,使得控制器可以正常访问所述存储器。在本实施例中,以所述存储器为gddr6 dram(graphics double data rate version6,第六代版图形用双倍数据传输率存储器)为例,加以说明。

27.dram包括多个dq引脚。每个引脚可输出不同的数据,在本实施例中,所述dram包括16个dq引脚。预设数据例如,“0123456789abcdef”通过命令预先写入至存储器内,则在读数据校准时,所述dram可输出对应的读数据。所述dq信号包括延迟段l1及数据段l2。所述延迟段l1输出非有效数据,在本实施例中,为全1(高电平)。所述数据段l2输出有效数据,数据段

l2包括多个数据,数据段l2为输出的预设数据,具体地,gddr6 dram进行读校准时,每次输出16个连续的数据,每个数据宽度理论上都为一个ui,预设数据必须不能为全1,可为多个连续的0数据。在本实施例中,为“0123456789abcdef”,其中,单个数据宽度10为数据眼(dataeye),包括左边界11及右边界12。在本实施例中,所述数据宽度10为一个ui,ui为数据的单位间隔,通常为控制器的时钟信号wck的时钟周期的1/2或1/4。理论上,每个数据宽度10相等。所述时钟信号wck用于采样存储器输出的读数据或者是释放存储器的写入数据。

28.对所述dram的读数据进行采样时,需要进行16次采样,dram在每个读校准命令会输出16个连续的数据,每个数据的宽度理论上为一个ui。控制器对这16个数据依次进行采样,每次采样理论上也间隔一个ui的宽度。如果采样点全部落在延迟段l1,例如,a位置,则采样到数据为全1,即16个1,则需要对时钟信号进行延迟,直至当某些采样点落在数据段l2上时,例如,b位置,则采样到部分预设数据,数据为非全1,包括0。当数据非全1时,表明16个采样点已经可以采样到数据,此时,需要进行粗校准,防止采样点超过数据的右边界。如果采样点在数据段,且在单个数据的左边界与右边界之间,且采样到的数据较为准确,如果采样点在单个数据的左边界与右边界的中间位置时,可以减少时钟抖动或者电源抖动对数据输出的影响,采样到的数据更为准确,其中,如果采样的数据与预设数据一致时,则确定采样到的数据正确,例如,采样到的数据为0123456789abcdef,如果采样的数据与预设数据不一致,则确定采样到的数据不正确。可以理解,所述采样的数据与预设数据一致包括数据顺序及内容均一致。例如,如果采样的数据为012345*****ab****,或者0123456789fabcde,则确定采样到的数据不正确。

29.请参阅图2,本实用新型提供的校准方法包括以下步骤:

30.步骤s1,基于预设的周期校准参数,对所述控制器的时钟信号进行周期校准(cycle校准),使得所述控制器对所述存储器的读数据进行采样的采样点位于所述读数据的数据段。具体地,所述周期校准参数包括校准周期t

n

,所述校准周期t

n

=2mui,ui为所述存储器的读数据中的单个数据宽度,m为自然数,在本实施例中,m=1,ui通常为时钟信号wck的时钟周期的1/2或者1/4,所述对所述控制器的时钟信号进行周期校准,包括:

31.步骤s11,接收到校准控制指令。所述校准控制指令可由存储器的上级控制器发出,所述上级控制器相对于存储器独立设置在存储器的外部,或者,是和存储器一起设置在芯片内部的控制器。

32.步骤s12,对所述读数据进行采样,得到采样数据。

33.步骤s13,确定所述采样数据为非有效数据,则对所述时钟信号以所述校准周期t

n

为单位进行延迟,直至所述采样数据为有效数据,则所述周期校准结束。

34.步骤s2,基于预设的粗校准参数,对所述时钟信号进行粗校准(coarse校准),使得所述采样点位于所述数据段中单个数据宽度内。当所述采样点位于所述数据段中单个数据宽度可以节省延迟段的校准时间,因此,也可以到达加快校准速度的效果。

35.在一个具体的实施例中,通过计数电路2对控制器的时钟信号延迟的时钟周期次数进行计数。

36.具体地,所述计数电路2包括多个的d触发器21及选择模块23,每个d触发器21的数据输出端q与另一个d触发器21的数据输入端d相连而相互串联,串联后的第一个d触发器的输入端d输入控制信号rdgate,每个d触发器21的时钟信号端输入时钟信号ck,每个d触发器

21的数据输出端q与所述选择模块23的输入端相连,所述选择模块23的输入端还输入周期校准信号cycle_code,所述时钟信号ck每延迟一次,所述计数电路2计数一次。

37.具体地,所述粗校准参数包括t

x

=ui/2

n

,n为自然数,在本实施例中,n=2,t

x

=ui/4,所述对所述控制器的时钟信号进行粗校准,包括:

38.步骤s21,对所述读数据进行采样,得到采样数据。

39.步骤s22,确定所述采样数据与预设数据不一致,则对所述时钟信号以所述粗校准周期t

x

为单位进行延迟,直至所述采样数据与预设数据一致。

40.步骤s22,确定所述采样数据与预设数据一致,则所述粗校准结束。

41.步骤s3,基于预设的细校准参数,对所述时钟信号进行细校准(fine校准),使得所述采样点位于所述单个数据宽度的第一边界与第二边界的中心值。

42.在本实施例中,所述第一边界及所述第二边界分别为所述单个数据宽度的左(起始)边界及右(结束)边界。所述细校准参数包括细校准周期t

y

=t

x

/2

l

,l为自然数,在本实施例中,l=3,t

y

=ui/32,所述对所述控制器的时钟信号进行细校准,包括:

43.步骤s31,对所述时钟信号提前一个所述粗校准周期t

x

。

44.步骤s32,对所述时钟信号延迟一个所述细校准周期t

y

。

45.步骤s33,对所述存储器的读数据进行采样,得到采样数据。

46.步骤s34,确定所述采样数据与所述预设数据不一致,则对所述时钟信号以所述细校准周期t

y

为单位进行延迟,直至所述采样数据与所述预设数据一致。

47.步骤s35,确定所述采样数据与所述预设数据一致,则确定当前采样点为所述单个数据宽度的第一边界。

48.步骤s36,对所述时钟信号延迟一个所述粗校准周期t

x

,数据的有效宽度为一个ui,t

x

的周期为ui/n,从左边界延迟一个t

x

可以减少校准右边界的时间,也可以保证延迟不超过右边界。

49.步骤s37,对所述读数据进行采样,得到采样数据。

50.步骤s38,确定所述采样数据与所述预设数据一致,则对所述时钟信号以所述细校准周期t

y

为单位进行延迟,直至所述采样数据与所述预设数据不一致。

51.步骤s39,确定所述采样数据与所述预设数据不一致,对所述时钟信号提前一个所述细校准周期t

y

,并确定当前采样点为所述数据宽度的第二边界。

52.在实际校准过程中,仅确定所述数据宽度的第一边界或者第二边界,也可以到达加快校准速度的效果。

53.在另一个实施例中,所述周期校准参数还包括周期校准次数n

i

及周期校准最大次数nmax,n

i

初始值为零,所述时钟信号每延迟一个所述校准周期t

n

时,所述周期校准次数n

i

加一,所述时钟信号每提前一个所述校准周期t

n

时,所述周期校准次数n

i

减一,所述对控制器的时钟信号进行周期校准,还包括:

54.步骤a,确定所述采样数据为非有效数据,还判断所述周期校准次数n

i

是否等于nmax。

55.步骤b,确定所述周期校准次数n

i

等于nmax,则发出错误提示。

56.步骤c,确定所述周期校准次数n

i

不等于nmax,还将所述周期校准次数n

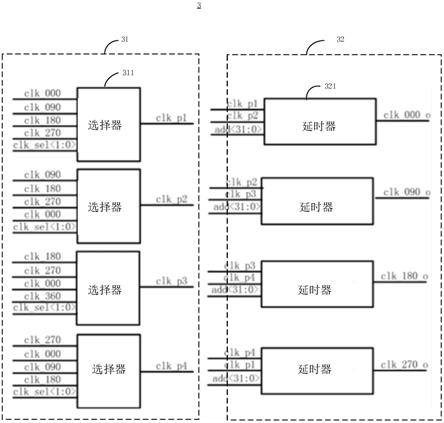

i

加一。

57.另外,所述粗校准参数还包括粗校准次数x

i

及粗校准最大次数xmax,x

i

初始值为

零,所述时钟信号每延迟一个所述粗校准周期t

x

时,所述粗校准次数x

i

加一,所述时钟信号每提前一个所述粗校准周期t

x

时,所述粗校准次数x

i

减一,所述细校准参数还包括细校准次数y

i

及细校准最大次数ymax,y

i

初始值为零,所述时钟信号每延迟一个所述细校准周期t

y

时,所述细校准次数y

i

加一,所述时钟信号每提前一个所述细校准周期t

y

时,所述细校准次数y

i

减一,所述方法还包括:

58.步骤d,在每次对所述时钟信号延迟一个所述细校准周期y

i

之前,还判断所述细校准次数y

i

是否等于所述细校准最大次数ymax。

59.步骤e,确定所述细校准次数y

i

小于所述细校准最大次数ymax,则直接将所述时钟信号延迟一个所述细校准周期y

i

,且将所述细校准次数y

i

加一。

60.步骤f,确定所述细校准次数y

i

等于所述细校准最大次数ymax,通过细校准不能完成校准,需再次通过粗校准对时钟信号进行延迟,因此,则还判断所述粗校准次数x

i

是否等于所述粗校准最大次数xmax。

61.步骤g,确定所述粗校准次数x

i

等于所述粗校准最大次数xmax;则将所述时钟信号延迟一个所述粗校准周期x

i

,且所述粗校准次数x

i

加一后,再将所述时钟信号延迟一个所述细校准周期y

i

,且将所述细校准次数y

i

加一。

62.步骤h,确定所述细校准次数y

i

等于所述细校准最大次数ymax,且所述粗校准次数x

i

等于所述粗校准最大次数xmax,则发出增加所述周期校准次数n

i

的请求,所述请求表明,通过粗校准及细校准不能完成校准,需再次通过周期校准对时钟信号进行延迟。

63.步骤i,接收到增加所述周期校准次数n

i

的请求时,则判断所述周期校准次数n

i

是否等于nmax,以响应所述请求。

64.步骤j,确定所述周期校准次数n

i

等于nmax,则发出错误提示。

65.步骤k,确定所述周期校准次数n

i

不等于nmax,则将所述周期校准次数n

i

加1。

66.可以理解,所述细校准参数还包括细校准最小次数ymin,在将所述时钟信号每提前一个所述时钟周期t

y

之前,所述方法还包括:

67.步骤a,判断所述细校准次数y

i

是否等于所述细校准最小次数ymin,确定所述细校准次数y

i

小于所述细校准最小次数ymin,则直接将所述时钟信号提前一个所述细校准周期t

y

,且将所述细校准次数y

i

减一。

68.步骤b,确定所述细校准次数y

i

等于所述细校准最小次数ymin,则将所述时钟信号提前一个所述粗校准周期t

x

,且将所述细校准次数x

i

减一后,再将所述时钟信号提前一个所述细校准周期t

y

,且将所述细校准次数y

i

减一。

69.请参阅图3、图4及图5,在具体实施例中,所述校准方法包括以下步骤:

70.步骤s101,接收到校准控制指令,周期校准开始。

71.步骤s102,对读数据进行采样,得到采样数据。

72.步骤s103,判断所述采样数据是否包括“0”,如果采样数据不包括“0”,则进入步骤s104,如果采样数据包括“0”,则进入步骤s106。

73.步骤s104,判断n

i

是否等于nmax,如果n

i

不等于nmax,则进入步骤s105。如果n

i

等于nmax,则进入步骤s107。

74.步骤s105,将时钟信号延迟一个校准周期t

n

,同时,将周期校准次数n

i

加一,即n

i

=n

i

‑1+1,其中,n

i

‑1表示上一次dram的时钟信号延迟时钟周期t0的次数,返回至步骤s102,重

复步骤s104、s105,直至判断采样读数据中包括“0”,则进入步骤s106。

75.步骤s106,周期校准结束。

76.步骤s107,发出错误提示。

77.步骤s201,对时钟信号进行粗校准。

78.步骤s400,在粗校准过程中,通过粗校准及细校准不能完成校准,需再次通过周期校准对时钟信号进行延迟,此时,控制器发送增加周期校准次数的请求cycle_inc,如果接收到控制器发送的增加周期校准次数的请求cycle_inc,则进入步骤s203。

79.步骤s500,在粗校准过程中,校准完成,则直接退出。

80.步骤s203,判断n

i

是否等于nmax,如果n

i

不等于nmax,则进入步骤s204。如果n

i

等于nmax,则进入步骤s107。

81.步骤s204,将时钟信号延迟一个校准周期t

n

,同时,将周期校准次数n

i

加一,即n

i

=n

i

‑1+1,然后,返回至步骤s201,重新开始粗校准。

82.在步骤s201,对时钟信号进行粗校准之后,进入步骤s205。

83.步骤s205,对读数据进行采样。

84.步骤s206,将所述采样数据与预设数据进行比较,如果二者不一致,则进入步骤s207,如果二者一致,则进入步骤s211。

85.步骤s207,将时钟信号延迟一个粗周期t

x

,同时,将粗校准次数x

i

加一,即x

i

=x

i

‑1+1,其中,x

i

‑1表示上一次时钟信号延迟粗校准周期t

x

的次数。

86.步骤s208,对读数据进行采样。

87.步骤s209,将采样数据与预设数据进行比较,如果二者不一致,则进入步骤s210,如果二者一致,则进入步骤s211。

88.步骤s210,判断x

i

是否等于xmax,如果x

i

不等于xmax,则返回至步骤s207,继续将时钟信号以粗校准周期t

x

为单位进行延迟,如果n

i

等于nmax,则进入步骤s400。

89.步骤s211,对所述时钟信号提前一个所述粗校准周期t

x

,同时,将粗校准次数x

i

减一,即x

i

=x

i

‑1‑

1。

90.步骤s212,对所述时钟信号延迟一个所述细校准周期t

y

,同时,将细校准次数y

i

加一,即y

i

=y

i

‑1+1。

91.步骤s213,对读数据进行采样。

92.步骤s214,将所述采样数据与预设数据进行比较,如果二者不一致,则进入步骤s215,如果二者一致,则进入步骤s219。

93.步骤s215,判断y

i

是否等于ymax,如果y

i

不等于ymax,则进入步骤s216,如果y

i

等于ymax,则进入步骤s217。

94.步骤s216,对所述时钟信号延迟一个所述细校准周期t

y

,同时,将细校准次数y

i

加一,即y

i

=y

i

‑1+1,并返回至步骤s213。

95.步骤s217,判断x

i

是否等于xmax,如果x

i

不等于xmax,则进入步骤s218,如果n

i

等于nmax,则进入步骤s400。

96.步骤s218,将时钟信号延迟一个粗周期t

x

,同时,将粗校准次数x

i

加一,即x

i

=x

i

‑1+1,并返回至步骤s216。

97.步骤s219,判断x

i

是否等于xmax,如果x

i

不等于xmax,则进入步骤s400,如果n

i

等于

nmax,则进入步骤s300。

98.步骤s300,确定采样点的左边界。

99.步骤301,将时钟信号延迟一个粗周期t

x

,同时,将粗校准次数x

i

加一,即x

i

=x

i

‑1+1。

100.步骤s302,对读数据进行采样。

101.步骤s303,将所述采样数据与预设数据进行比较,如果二者不一致,则进入步骤s304,如果二者一致,则进入步骤s308。

102.步骤s304,判断y

i

是否等于ymin,如果y

i

等于ymin,则进入步骤s305,如果y

i

不等于ymin,则进入步骤s306。

103.步骤s305,将时钟信号提前一个粗周期t

x

,同时,将粗校准次数x

i

减一,即x

i

=x

i

‑1‑

1。

104.步骤s306,将时钟信号提前一个细周期t

y

,同时,将粗校准次数y

i

加一,即y

i

=y

i

‑1+1。

105.步骤s307,确定采样点的右边界。

106.步骤s308,判断y

i

是否等于ymax,如果y

i

不等于ymax,则进入步骤s309,如果y

i

等于ymax,则进入步骤s310。

107.步骤s309,对所述时钟信号延迟一个所述细校准周期t

y

,同时,将细校准次数y

i

加一,即y

i

=y

i

‑1+1,并返回至步骤s302。

108.步骤s310,判断x

i

是否等于xmax,如果x

i

不等于xmax,则进入步骤s311,如果x

i

等于xmax,则进入步骤s312。

109.步骤s311,将时钟信号延迟一个粗周期t

x

,同时,将粗校准次数x

i

加一,即x

i

=x

i

‑1+1,并返回至步骤s301。

110.步骤s312,判断n

i

是否等于nmax,如果n

i

不等于nmax,则进入步骤s400,如果n

i

等于nmax,则进入步骤s307。

111.步骤s313,根据步骤s300中确定的左边界及及步骤s307中确定的右边界,确定中心值。

112.步骤s500,校准完成。

113.基于与方法同样的实用新型构思,本实用新型实施例还提供了一种校准装置,用于对连接至存储器的控制器进行时序校准,如图5所示为所述装置100实施例的结构示意图,所述装置100包括:

114.第一校准模块10,用于基于预设的周期校准参数,对所述控制器的时钟信号进行周期校准,使得所述控制器对所述存储器的读数据进行采样的采样点位于所述读数据的数据段。

115.第二校准模块20,用于基于预设的粗校准参数,对所述控制器的时钟信号进行粗校准,使得所述采样点位于所述数据段中单个数据宽度内。

116.在另一实施例中,所述装置100还包括:

117.第三校准模块30,用于基于预设的细校准参数,对所述控制器的时钟信号进行细校准,使得所述采样点位于所述单个数据宽度的第一边界与第二边界的中心值。

118.基于与前述实施例中同样的实用新型构思,本实用新型实施例还提供一种存储器

的时序校准设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,所述处理器执行所述程序时实现前文任一所述方法的步骤。

119.基于与前述实施例中同样的实用新型构思,本实用新型实施例还提供一种计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行时实现前文任一所述方法的步骤。

120.请参阅图8,基于与前述实施例中同样的实用新型构思,本实用新型实施例还提供一种延迟电路3用于在校准过程中对时钟信号进行延迟。所述延迟电路3包括选择单元31及延迟单元32。

121.所述选择单元31包括4路选择器311,每个选择器311接收4路4相位的分频时钟信号及选择控制信号,所述分频时钟信号的时钟周期为t0,所述每个选择器311根据所述选择信号分别选择输出其中1路的分频时钟信号。

122.所述延迟单元32包括4路延迟器321,每个所述延迟器321接收所述选择单元31的输出的2路不同的分频时钟信号及延迟控制信号,每个所述延迟单元32根据所述延迟控制信号分别选择输入1路分频时钟信号,使得所述延迟单元32输出所述延迟信号,所述延迟信号与所述时钟信号之间的延迟为(n*a*t0)/4*q,其中,n为选择单元31的延迟参数,在本实施例,1≤n≤4,且为自然数,a由所述延迟控制信号确定,q由所述延迟器32确定,且1<a<q,a、q为自然数。

123.请参阅图9,每个延迟器321包括结构相同的第一延迟子单元a、第二延迟子单元b及反相器321a,所述第一延迟子单元a及所述第延迟子单元b用于根据延迟控制信号选择1路分频时钟信号,通过所述反相器321输出。请参阅图11,每个第一延迟子单元或者每个二延迟子单元包括q个开关组合。在本实施例中,q=32,1<a<32,且a为自然数,所述延迟信号与所述时钟信号之间的延迟为(n*a*t0)/128。

124.请参阅图11,每个开关组合包括第一开关元件、第二开关元件、第三开关元件及第四开关元件,所述第一开关元件的第一端连接第一工作电压,第二端连接第二开关元件的第一端,第三端输入所述分频时钟信号;所述第二开关的第二端输入所述延迟信号,所述第二开关的第三端连接所述反相器的输入端;所述第三开关元件的第一端连接第二工作电压,第二端连接第四开关元件的第一端,第三端输入所述分频时钟信号;所述第四开关的第二端输入所述延迟信号,所述第四开关的第三端连接所述反相器的输入端。

125.在本实施例中,所述第一开关元件及所述第二开关元件为pmos管,所述第三开关元件及所述第四开关元件为nmos管。

126.在一个具体的实施例中,在本实施例中,以p=1为例,加以说明。

127.每个选择器311接收4路4相位的分频时钟信号clk_000/clk_090/clk_180/clk_270及选择信号clk_sel。

128.具体地,请参阅表1,选择信号clk_sel<1:0>选择clk_000/clk_090/clk_180/clk_270中一个作为clk_p1的输出。例如,n=1,clk_sel<1:0>的值为00时,clk_p1输出clk_000,clk_p2输出clk_090,clk_p3输出clk_180,clk_p4输出clk_270,所述延迟信号与所述时钟信号之间的延迟为a*t0/128。

129.表1

[0130][0131][0132]

其中,当clk_sel=00时,clk_000输出到clk_p1,clk_090输出到clk_p2,clk_180输出到clk_p3,clk_270输出到clk_p4。clk_p1和clk_p2经对应的延迟器321插值输出clk_000_o;clk_p2和clk_p3经对应的延迟器321插值输出clk_090_o;clk_p3和clk_p4经对应的延迟器321插值输出clk_180_o;clk_p4和clk_p1经对应的延迟器321插值输出clk_270_o;clk_000_o/clk_090_o/clk_180_o/clk_270_o的延迟由add<31:0>确定。

[0133]

当clk_sel=01、10、11时,延迟单元32的输出情况与clk_sel=00大致相同,因此,在此不再赘述。具体输出clk_000_o/clk_090_o/clk_180_o/clk_270_o的时序可参阅图12、图13、图14及图15。

[0134]

请参阅图10,所示为每个延迟电路32的等效电路图,每个第一延迟子单元a包括第一开关单元tr

‑

inv_p1,每个第二延迟子单元b包括第二开关单元tr

‑

inv_p2,第一开关单元tr

‑

inv_p1导通时,第二开关单元tr

‑

inv_p2关闭。

[0135]

延迟信号add<31:0>包括多个延迟信号add

‑

n(0)、add

‑

n(1)、...、add

‑

n(32)。多个延迟信号add

‑

n(0)、add

‑

n(1)、...、add

‑

n(32)通过控制每个开关组合中第一开关单元tr

‑

inv_p1及第二开关单元tr

‑

inv_p2,确定clk_p1和clk_p2的作用比例,从而确定输出的延迟。其中,add<31:0>的值都为0时,输出的clk_n完全由clk_p2确定;add<31:0>的值都为1时,输出的clk_n完全由clk_p1确定。

[0136]

每个延迟器321的固定延迟为t1,32相位的延迟为t0/128,add<31:0>的值为a,0≤a≤31,则clk_000_o的延迟为:td_000=t1+(a*t0)/128;td_090=t1+(a*t0)/128;因此,clk_000_o和clk_090_o之间的延迟为t0/4。当clk_000和clk_090之间的延迟不是标准的t0/4,有一个偏差δ,即clk_000和clk_090之间的延迟为t0/4+δ。clk_000_o的延迟为:td_000=t1+a

·

(t0/4+δ)/32;td_090=t1+a

·

(t0/4

‑

δ)/32;clk_000_o和clk_090_o之间的延迟为t0/4

‑

δ≤t0/4+(1

‑

a/16)δ≤t0/4+δ。

[0137]

本实用新型实施例中提供的技术方案,至少具有如下技术效果或优点:

[0138]

本实用新型实施例校准方法通过采用不同精度的校准步骤(例如,周期校准、粗校准、细校准)对存储器的时序进行校准,可快速、且准确地确定可以采样到存储器的读数的采样点。

[0139]

本实用新型实施例延迟电路的输出时钟是由输入时钟clk_000/clk_090/clk_180/clk_270插值产生的,可减少输入时钟clk_000/clk_090/clk_180/clk_270之间的延迟偏差,且延迟电路的延迟时间是基于时钟周期的,故不随电压,温度和工艺变化而变化。本实用新型中,延迟单元的最小精度为128分之一的时钟周期,和电压、温度及工艺没有关系。

[0140]

尽管已描述了本实用新型的优选实施例,但本领域内的技术人员一旦得知了基本创造概念,则可对这些实施例作出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本实用新型范围的所有变更和修改。

[0141]

显然,本领域的技术人员可以对本实用新型进行各种改动和变型而不脱离本实用新型的精神和范围。这样,倘若本实用新型的这些修改和变型属于本实用新型权利要求及其等同技术的范围之内,则本实用新型也意图包括这些改动和变型在内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1