以静态模拟校准电路实现的钟控数据采样器的动态积分时间调节的制作方法

以静态模拟校准电路实现的钟控数据采样器的动态积分时间调节

1.相关申请的交叉引用

2.本技术要求申请号为16/378,467,申请日为2019年4月8日,名称为“以静态模拟校准电路对钟控数据采样器进行的动态积分时间调节”,发明人为kiarash gharibdoust的美国申请的优先权,并将其全部内容援引于此,以供所有目的之用。

3.参考文献

4.以下在先申请通过引用整体并入本文,以供所有目的之用:

5.申请号为15/494,435,申请日为2017年4月21日,公开号为us20170309346a1,发明人为armin tajalli,名称为“以可调高频增益对采样器进行校准的装置和方法”的美国专利申请,下称【tajalli i】;

6.申请号为15/792,696,申请日为2017年10月24日,专利号为10,200,218,发明人为armin tajalli,名称为“具有高宽带增益的级联采样器”的美国专利,下称【tajalli ii】。

技术领域

7.本发明总体涉及通信系统电路,尤其涉及对相对于给定参考信号电平和时钟瞬时获得输入信号幅度测量值的电路进行的调节和控制。

背景技术:

8.在当今数字系统中,数字信息必须得到高效可靠的处理。在这一背景下,须将数字信息理解为含于离散值(即非连续值)内的信息。数字信息不但可由比特和比特集合表示,而且还可由有限集合内的数字表示。

9.为了提高总带宽,大多数芯片间或装置间通信系统采用多条线路进行通信。这些线路当中的每一条或每一对均可称为信道或链路,而且多条信道组成电子器件之间的通信总线。在物理电路层级上,芯片间通信系统内的总线通常由芯片与主板之间的封装电导体、印刷电路板(pcb)上的封装电导体、或pcb间线缆和连接器内的封装电导体构成。此外,在高频应用中,还可采用微带或带状pcb迹线。

10.常用总线线路信号传输方法包括单端信令法和差分信令法。在需要高速通信的应用中,这些方法还可以在功耗和引脚利用率方面(尤其高速通信中的这些方面)进一步优化。最近提出的向量信令法可在芯片间通信系统的功耗、引脚利用率及噪声稳健性方面实现更加优化的权衡取舍。此类向量信令系统将发送器的数字信息转换为向量码字这一不同表示空间,并且根据传输信道的特性和通信系统的设计约束选择不同的向量码字,以在功耗、引脚利用率及速度之间做出更优的权衡取舍。这一过程在本技术中称为“编码”。编码后的码字以一组信号的形式从发射器发送至一个或多个接收器。接收器将所接收的与码字对应的信号反转为最初的数字信息表示空间。这一过程在本技术中称为“解码”。

11.无论采取何种编码方法,均须对接收装置所接收的信号进行间隔采样(或者以其他方式记录其信号值),而且无论传输信道的延迟、干扰及噪声条件如何,该采样间隔均须

使得采样值能够以最佳方式表示最初的发送值。该采样操作可通过钟控比较器或采样器在时域(例如,以采样保持电路在模拟域,或者以钟控锁存器在数字域)和幅域(例如,以比较器或切片器)中独立进行,或者作为组合式时域/幅域采样操作进行。该采样或切片操作的时间由决定了正确采样时间的关联时钟与数据对齐(cda)定时系统控制。

技术实现要素:

12.在本技术描述的方法和系统中:由参考分支电路根据经带隙发生器和共模电压输入获得的参考电流,生成工艺/电压/温度(pvt)相关参考电压;由静态模拟校准电路的输出端响应于所述共模电压输入和可调节电流,生成pvt相关输出电压;由所述静态模拟校准电路根据应响应于所述pvt相关输出电压与所述pvt相关参考电压之间的比较结果所生成的控制信号,调节所述可调节电流;以及通过将所述控制信号提供给钟控数据采样器而实现以pvt校准后电流对所述钟控数据采样器的设置。

13.本领域已知存在用于进行定时信号幅度测量的电路,一般称为“采样器”。此类采样器为数据通信接收器的一种常见元件,其将模拟采样保持电路或数字锁存器的时间采样功能与数字比较器或切片器的幅度比较功能相结合,一般作为前端模拟信号处理与后端数字数据处理之间的接口。

14.目前已存在衍生自模拟信号比较器、钟控数字锁存器及其他混合式模拟/数字电路架构的采样器电路,每种此类架构的变形形式的益处和限制已为人所知。其中的一种架构,尤其钟控动态积分器/采样器架构已确认具有在实现高速操作的同时消耗较小电源电流的能力。该采样器衍生自如【tajalli i】中所述的经典模拟差分比较器,并以动态方式操作,以先在时钟信号的控制下对内部电路节点进行充电,然后通过比较电路对该节点进行放电,从而在时钟信号跃迁的时刻实现有效输入信号与参考输入信号之间的定时比较。一种钟控动态采样器实施方式见【tajalli ii】一文的描述。

15.虽然具有上述高速和低功耗优点,但是此类电路的动态本质可在制造环境中导致漂移和稳定性问题。虽然给定集成电路内的各个mos晶体管可制造成彼此密切匹配,但是不同晶片之间的绝对操作参数,尤其栅极阈值电压、增益及信道电阻可迥然不同,而且同一晶片内的此类参数可随温度和电源电压的波动而大幅变化。此类波动可导致器件之间的数据检测精度存在差异,并且可导致同一器件的数据检测功能随操作条件的不同而下降。

16.本技术所述实施方式用于作为闭环控制系统的一环,对采样器的操作特性进行测量,以减轻上述波动变化的影响。其中,为了最大程度减小对制造后数据检测路径的影响,将独立的静态模拟校准电路用作制造后动态电路操作特性的测量代替电路。

附图说明

17.图1所示为钟控动态积分器/采样器电路的一种实施方式。

18.图2所示为静态模拟校准电路的一种实施方式,该电路可用作图1所示等动态电路的测量代替电路。

19.图3所示为提供待与作为控制信号发生器判定输入的测量值比较的已知参考信号的参考分支电路的一种实施方式。

20.图4为根据一种实施方式的一种方法的流程图。

具体实施方式

21.为了对经通信系统发送的数据值进行可靠检测,通信接收器须在精心选择的时间点上精确测量接收信号值的幅度,此类时间点一般选择于接收信号跃迁之间稳定时间段的中心或其附近(即每个接收单位间隔(ui)检测一次)。根据单条线路内的信号,或者多条线路内信号(例如,由用于检测向量信令码的多输入比较器或混频器(mic)提供)的加权线性组合结果,可以推导出接收信号的来源。

22.在一些实施方式中,首先以采样保持或跟踪保持电路在选择的时间点上采集接收信号的值,然后以已知电压比较器电路,相对于一个或多个参考值测量结果值。作为替代方案,可先以比较器或“切片器”相对于参考电压测量接收信号的模拟电平,然后由钟控数字锁存器采集数字结果。

23.接收信号的最佳测量点一般称为“眼图中心”(参考众所周知的表示信号幅度与时钟间隔关系的“眼图”)。在时间维度上,采样点一般通过设置为在所需采样时间点出现的本地“接收时钟”确定。此类接收时钟时间的生成和持续控制方式在本领域中已为人所熟知——时钟数据对齐(cda,也称时钟数据恢复(cdr))系统相对于接收信号稳定时间,对采样时间进行测量和步进式调节,以实现采样时间的优化。

24.类似地,用于接收信号幅度比较的最佳参考电平可以以动态方式生成。判定反馈均衡(dfe)为其中一种用于提高串行通信系统信号检测能力的技术。该技术中假设,发送器与接收器间通信信道的通信线路特性存在瑕疵,因此与先前发送比特相关联的能量可能会残留于信道之内(例如,作为阻抗扰动导致的反射波的形式),从而对后续比特的接收造成负面影响。接收器的dfe系统通过通信信道的模拟而对先前单位间隔(ui)内检测出的每一比特进行处理,以获得该比特对后续单位间隔的影响估计值。该估计值在本技术中称为“dfe校正量”,通过从接收信号中减去该dfe校正量,可实现对符号间干扰预测量的补偿。在替代实施方式中,可以通过在从dfe校正信号推导出的参考电压电平下对接收信号进行测量(例如,以差分比较器进行测量),实现与所述减法操作在功能上等效的操作。在实际使用中,dfe系统在数据比特检测之前,将从多个先前单位间隔推导出dfe校正量(在本技术中分别称为“dee因子”)施加至接收信号。

25.本领域中,已知还存在进行组合式幅度/时间测量的电路,该电路一般称为“采样器”。此类采样器为数据通信接收器的一种常见元件,其将模拟采样保持电路或数字锁存器的时间采样功能与数字比较器或切片器的幅度比较功能相结合,一般作为前端模拟信号处理与后端数字数据处理之间的接口。目前已存在衍生自模拟信号比较器、钟控数字锁存器及其他混合式模拟/数字电路架构的采样器电路,每种此类架构的变形形式的益处和限制已为人所知。

26.其中的一种采样器架构,尤其钟控动态积分器/采样器架构已确认具有在实现高速操作的同时消耗较小电源电流的能力。该采样器衍生自如【tajalli i】中所述的经典模拟差分比较器,并以动态方式操作,以先在时钟信号的控制下对内部电路节点进行充电,然后通过比较电路对该节点进行放电,从而在时钟信号跃迁的时刻实现有效输入信号与参考输入信号之间的定时比较。一种钟控动态采样器实施方式见【tajalli ii】一文的描述。

27.虽然具有上述高速和低功耗优点,但是此类电路的动态本质可在制造环境中导致漂移和稳定性问题。虽然给定集成电路内的各个mos晶体管可制造成彼此密切匹配,但是不

同晶片之间的绝对操作参数,尤其栅极阈值电压、增益及信道电阻可迥然不同,而且同一晶片内的此类参数可随温度和电源电压的波动而大幅变化。此类波动可导致器件之间的数据检测精度存在差异,并且可导致同一器件的数据检测功能随操作条件的不同而下降。

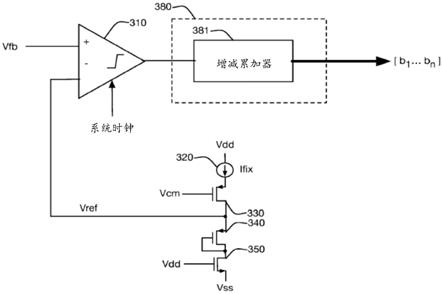

28.本技术所述实施方式用于作为闭环控制系统的一环,对采样器的操作特性进行测量,以减轻上述波动变化的影响。其中,为了最大程度减小对制造后数据检测路径的影响,将独立的静态模拟校准电路用作制造后动态电路操作特性的测量代替电路。

29.图1所示为钟控动态积分器/采样器电路的一种实施方式,该电路在一种具体实施方式中为dfe计算子系统的部件。动态电路一般操作于输入时钟信号控制的多个活动阶段。对于图1电路,晶体管111,112,...119在输入时钟clk为低电平时提供充电路径,以使得来自vdd的电流能够对内部电路节点125的分布式电容进行充电。其中,可通过以控制信号[b1,b2,...b

n

]启用多于一个的充电晶体管,进行充电速度的设置。如图中虚线所示,还可通过纳入更多个与充电路径晶体管111,112

……

并联的220而支持更多控制比特。对于给定的时钟信号低电位充电间隔时间长度和节点电容,可以通过提高节点225的接线端电压来获得更大的控制信号[b1,b2,...b

n

]值(即启用更多个晶体管)。在充电路径启用后,电流流过差分输入晶体管130和131,大小与输入信号vin+和vin

‑

之间的差值成正比。如此,vout

‑

和vout+的输出电压首先为低值(放电),并自clk的下降沿开始以分别由晶体管130和131的输入信号vin+和vin

‑

决定的速度向vdd增大。因此,该充电过程(也称积分器/采样器的积分时间)自时钟下降沿开始,并持续至其中一个输出节点的输出电压升高至使得晶体管140或141的栅漏电压使其不再继续保持导通为止。

[0030]

当输入时钟clk升至高电平时,充电路径断开,而放电路径经两个分支电路启用,以在下一个采样间隔之前将所述一对输出节点重置。如图1所示,放电路径可分别包括晶体管130,140,150和晶体管131,141,151。此外,控制信号en用于这些放电路径的启用和禁用,出于本说明书的描述目的,可以假设,en设置为放电路径可因晶体管140和141的导通而由时钟信号clk启用。

[0031]

在一些实施方式中,钟控数据采样器的可采用相反结构,其中,所述一对输出节点先根据采样时钟预充电,然后根据输入信号vin+和vin

‑

以各种速度放电。与差分输出节点vout+和vout

‑

连接的锁存器可用于将积分信号转换为锁存数字输出,以供以上两种实施方式中的任何一种使用。

[0032]

所得差分结果vout不但取决于输入信号,而且还在一定程度上取决于输入晶体管130/131的增益和晶体管140,141,150,151的信道特性,而此类增益和特性已知随集成电路工艺、电流、时间推移及温度而变化。因此,关联控制信号发生器一般通过改动控制信号[b1,b2,...b

n

]来调节对所述一对输出节点vout+和vout

‑

进行充电的电流幅度,从而获得恒定一致的差分结果。

[0033]

在一些情形中,采样器可通过如下方式校准:先根据共模值调节电流,然后测量采样器性能,以确保电流能够提供正确的采样间隔。此类情形可实现对图1所示动态采样器的复制,但其需要以与主采样器相同的频率进行钟控,而且此类电路复制无法消除对快速输出测量的需求。

[0034]

作为替代方案,如本技术中所述,将静态模拟校准电路用作如图1所示等动态电路的测量代替物。需要注意的是,使图1特性产生随工艺和环境波动的晶体管固有特性为晶体

管增益,晶体管阈值电压,以及“接通”电阻等晶体管信道特性,所有此类元素均有益于静态或稳态测量。

[0035]

图2所示为复制图1动态电路的结构但省去钟控操作的静态模拟校准电路的一种实施方式。与图1等效装置一致,图2电路中的每一个晶体管均具有完全相同的尺寸和设计特性。因此,举例而言,在控制信号[b1,b2,...b

n

]值相同的情况下,图2静态电流i1,i2,...i

n

与图1初始(即峰值)充电电流i1,i2,...i

n

基本完全相同。出于描述的方便性,在本技术中,总电流称为在图2静态实施方式中,两个信号输入均与对应于有效输入vin+和vin

‑

的共模电压输入vcm连接。对于对输入信号进行电容式耦合的系统,所述电压等效于电容器下游的偏置电压。所述静态模拟校准电路根据所述共模电压输入以及经晶体管211,212,...,219提供的可调节电流生成工艺/电压/温度(pvt)相关输出电压vfb。

[0036]

图3所示为提供待与作为控制信号发生器判定输入的测量值比较的已知参考信号的参考分支电路的一种实施方式。该参考分支电路包括电流源320以及晶体管330,340,350,这些晶体管分别与上述电路分支中具有类似尺寸和设计特性的晶体管(如130,140,150)具有相同拓扑结构。然而,参考电流源320所提供的电流源自标准带隙基准电路,不随工艺波动以及器件电压与温度变化。因此,vref表示通过根据共模电压输入vcm向晶体管330,340,350施加获得自带隙发生器的已知标准化参考电流而生成的pvt相关参考电压。

[0037]

比较器310将得自图2的pvt相关输出电压vfb与pvt相关参考电压vref相比较,以为控制信号发生器380生成误差指示内容,该指示内容含有控制信号[b1,b2,...b

n

]的校正量,以对可调节电流i

tot

进行调节。出于描述的简单性目的,380示为包括增减累加器381,该增减累加器根据310的结果进行上数或下数,以使控制[b1,b2,...b

n

]以及所提供的电流i

tot

发生变化,从而使得图2静态模拟校准电路和图3参考分支电路生成基本相等的结果。随后,可将相同控制信号值[b1,b2,...b

n

]施加至如图1所示钟控动态积分器/采样器电路,该施加可通过静态电路的代替测量功能完成,从而实现向有效动态电路提供更新后的控制值。

[0038]

图4为根据一些实施方式的方法400的流程图。如图所示,方法400包括:由参考分支电路根据经带隙发生器和共模电压输入获得的参考电流,生成工艺/电压/温度(pvt)相关参考电压(410);由静态模拟校准电路的输出端响应于所述共模电压输入及可调节电流,生成pvt相关性输出电压(420);由静态模拟校准电路根据响应于所述pvt相关输出电压与pvt相关参考电压之间的比较结果而生成的控制信号,调节所述可调节电流(430);以及通过将所述控制信号提供给所述钟控数据采样器,实现以pvt校准后电流对钟控数据采样器进行配置(440)。

[0039]

在一些实施方式中,所述可调节电流一直调节至所述pvt相关输出电压与所述pvt相关参考电压相等或者处于某个预设阈值以内为止。在一些实施方式中,所述参考分支电路对应于所述静态模拟校准电路内的分支电路的复制电路。在部分此类实施方式中,所述可调节电流分割于所述静态模拟校准电路的两个分支电路之间,而且大小为所述参考电流大小的两倍。

[0040]

在一些实施方式中,所述方法进一步包括通过启用晶体管来启用所述静态模拟校准电路和参考分支电路。在部分此类实施方式中,通过启用所述静态模拟校准电路和参考分支电路来实现所述pvt校准后电流的校准。在一些实施方式中,所述静态模拟校准电路和

参考分支电路响应于温度变化而启用。在一些实施方式中,所述静态模拟校准电路和参考分支电路在系统启动时启用。在一些实施方式中,所述静态模拟校准电路和参考分支电路响应于共模输入电压的变化而启用。

[0041]

在一些实施方式中,所述控制信号包含多个比特。在一些实施方式中,可利用二进制码控制信号启用所述钟控数据采样器中具有不同大小且彼此并联的相应电流源。在替代实施方式中,可利用温度计码控制信号启用所述钟控数据采样器中具有相同大小且彼此并联的相应电流源。

[0042]

在一些实施方式中,由累加器电路对所述pvt相关输出电压与pvt相关参考电压之间的比较结果进行累计。此类累加器电路可以为用于对获得自比较器310最低有效比特(lsb)部分的比较结果进行累计的数字累加器,而最高有效比特部分提供所述多比特控制信号。此处之外,可以使用其他累计装置。在一些实施方式中,如图3所示,所述pvt相关输出电压与所述pvt相关参考电压之间的比较结果由斩波放大器310生成。此类放大器可由具有50mhz等合适频率的系统时钟钟控。

[0043]

在一些实施方式中,所述方法进一步包括:经与可变增益放大器(vga)输出端连接的电阻器

‑

电容器(rc)网络,获得所述共模电压输入,所述电阻器

‑

电容器网络对由所述钟控数据采样器处理的信息信号进行操作。此类rc网络可对应于低通滤波器。

[0044]

为了实施所述生成、测量、调节及配置操作,控制信号发生器380的其他实施方式可包括执行于嵌入式处理器内的有限状态机、软件或固件,或者包括专用硬件。在一些实施方式中,控制信号的操作周期性地进行。在一些实施方式中,为了减小总功耗,可在测量操作的间隙将所述静态模拟校准电路和参考分支电路的部分或全部断电或禁用。一些实施方式在系统初始启动时运行,以对工艺相关电路差异进行测量和补偿。其他实施方式在系统正常操作的某一部分过程中操作,以对pvt相关波动进行测量和补偿。控制信号和/或其相应调节可表示编码于温度计码中的大小相等的变化量,表示于二进制码或格雷码中的二进制加权调节量,和/或其他功能编码。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1