一种自调节模数转换器级间运放增益的数字反馈校准电路的制作方法

1.本发明涉及集成电路设计技术领域,具体涉及到一种自调节模数转换器级间运放增益的数字反馈校准电路。

背景技术:

2.模数转换器即adc(analog to digital converter)为模数混合信号芯片,其内部同时存在数字电路和模拟电路,在adc芯片设计时常因pipeline adc结构的优越性被广泛采纳,但因流水线结构中每一级都对运放有较高的要求,在工作环境恶劣的情况,运放如处于较低差工作状态下,将对adc下一级的量化产生较大影响,这种现象在很大程度上决定了芯片的性能。如一个16bit的adc芯片,第一级为3.5的ad进行量化时,当第一级的运算放大器的开环增益达到95db则,第一级因运放增益导致的误差将低于0.5lsb,但当运算放大器的开环增益较低时,pipeline adc的后几级的量化将会达到上百lsb。目前高速adc芯片被广泛应用在高速通信、雷达及自动化设备等电子系统中,由于工作在高频下、工艺偏差以及环境温度变化,运算放大器的高增益工作点将频繁发生变化,如何能保证运算放大器的最佳工作区间,直接影响到芯片的性能。因此,迫切的需要一种新的方案解决上述技术问题。

技术实现要素:

3.发明目的:本发明的目的是针对目前技术中的不足,提供了一种自调节模数转换器级间运放增益的数字反馈校准电路,有效解决了现有技术中adc芯片因级间运放的有限增益带来的量化信号增益误差。

4.技术方案:为实现上述目的,本发明提供了一种自调节模数转换器级间运放增益的数字反馈校准电路,其特征在于:包括有数字域电路和模拟域电路,所述模拟域电路和数字域电路组成一个闭合环路系统,所述模拟域电路包括有主adc、辅助adc电路以及dac,所述辅助adc工作频率为主adc工作频率的二十分之一,所述数字域电路包括有运放增益反馈控制模块,所述模拟域电路中的主adc和辅助adc电路输出模拟信号到运放增益反馈控制模块,所述运放增益反馈控制模块对运放增益进行收敛。

5.作为本方案的一种改进,所述辅助adc电路用于量化主adc第一级与第二级级间运算放大器前的节点电压,当工作在较低时钟域下且量化精度较低时,进行求级间增益,将主adc和辅助adc不同量化值输入到数字域电路中。

6.作为本方案的一种改进,所述运放增益反馈控制模块包括有运放增益收敛模块,所述运放增益收敛模块通过分别量化运放前后2个点来求运算放大器增益大小,将第一级的余量值和辅助adc的结点值,送入最小梯度下降算法电路中进行收敛运放增益。

7.作为本方案的一种改进,所述数字域电路还包括有增长趋势因子收敛模块,所述增长趋势因子收敛模块将当前增益值作为期望值,该值前几个周期的增益值作为样本值,通过样本值来预测期望值,引入增益增长趋势因子,即gcur=gpre*k,其中gcur为当前增益值,gpre为该值前几个周期的增益值,k为增益增长趋势因子。

8.作为本方案的一种改进,所述数字域电路还包括有增长趋势因子判断模块,所述增长趋势因子判断模块带入k(i+1)=k(i)

‑

pre*(k(i)*gpre

‑

gcur)收敛算法中,其中同时k(i)为当前增益增长趋势因子,k(i+1)为下一周期增益增长趋势因子;令gcur=gpre+gpre*k,所以k+1=cur/pre,即k=k+1。

9.作为本方案的一种改进,所述数字域电路还包括有自校准反馈模块,所述自校准反馈模块将数字反馈输出v_gain作为调节值,送入算法v(i+1)=v(i)

‑

/+dig_sns*dig_res*u对反馈值进行收敛,其中v(i)为当前的反馈值,v(i+1)为下一时刻的反馈值,dig_sns为辅助adc对节点量化输出,dig_res为主adc的量化值输出,u为步长。

10.作为本方案的一种改进,所述v_gain在模拟域调节的电压范围为0v~~1.8v,采用9数据来进行量化,最小精度为3.51mv。

11.作为本方案的一种改进,所述模拟域电路还包括有反馈信号控制运放正反馈电路,所述反馈信号控制运放正反馈电路包括一个子dac和一个控制运放正反馈电路,所述子adc将数字反馈信号转为模拟信号,将9bit的数字信号转化为一个0v到1.8v的模拟信号;所述控制运放正反馈电路将转化后的模拟信号引入到运算放大器电路中,通过改变运算放大器内部的正反馈强弱来改变运算放大器的工作点。

12.与现有技术相比本发明具有的有益效果:

13.1、自动调节功能,本校准电路的整体结构设计巧妙,通过对数字域电路和模拟域电路加入控制和收敛电路使其整个系统形成一个反馈系统,加入了收敛增益和判断增益增长趋势因子电路,芯片可以自动调整运算放大器工作点,使模数转换器级间运放可以保持在较高增益下;

14.2、减少额外的数字补偿电路,因可以持续工作在高增益下,所以在数字电路中不需要额外加入数字补偿电路对模拟出现的误差进行校准补偿;

15.3、处于较高增益下,又可以间接地减少因寄生电容,电容失配及反馈电容带来的误差。

附图说明

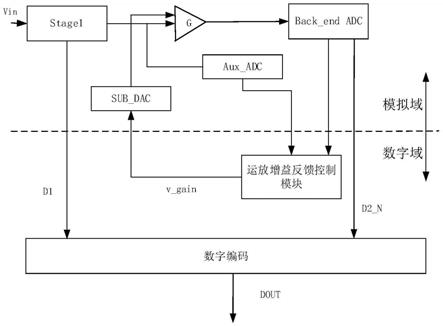

16.图1为数字域与模拟域电路结构图;

17.图2为模拟域加入辅助adc电路结构图;

18.图3为模拟域加入反馈电路结构图;

19.图4为整个系统反馈校准框图;

20.图5为数字域运放增益收敛算法结构;

21.图6为模拟域运算放大器增益变化曲线;

22.图7为数字域数字自校准反馈模块。

具体实施方式

23.下面结合附图和具体实施方式,进一步阐明本发明,应理解下述具体实施方式仅用于说明本发明而不用于限制本发明的范围。需要说明的是,下面描述中使用的词语“前”、“后”、“左”、“右”、“上”和“下”指的是附图中的方向,词语“内”和“外”分别指的是朝向或远离特定部件几何中心的方向。

24.本发明提出了一种自调节模数转换器级间运放增益的数字反馈校准电路,通过在模拟域加入了辅助adc电路,该辅助adc电路用于量化主adc第一级与第二级级间运算放大器前的节点电压,工作在较低时钟域下,同时量化精度较低,这样可以在不增加较多模拟域资源开销前提下,进行求级间增益,随后会将主adc和辅助adc不同量化值输入到数字域电路中,在数字域电路求得运放增益值。

25.数字域电路中加入了运放增益收敛模块,该模块作用是通过分别量化运放前后2个点来求运算放大器增益大小,将第一级的余量值和辅助adc的结点值,送入最小梯度下降算法电路中进行收敛运放增益。

26.在数字域中还加入了增长趋势因子收敛模块及增长趋势因子判断模块,对求得的增益值来判断增益的趋势,通过当前增益值与该值前几个周期的增益值来求增长趋势因子,将当前增益值作为期望值,该值前几个周期的增益值作为样本值,通过样本值来预测期望值,引入增益增长趋势因子,即gcur=gpre*k,其中gcur为当前增益值,gpre为该值前几个周期的增益值,k为增益增长趋势因子;带入k(i+1)=k(i)

‑

pre*(k(i)*gpre

‑

gcur)收敛算法中,其中同时k(i)为当前增益增长趋势因子,k(i+1)为下一周期增益增长趋势因子;令gcur=gpre+gpre*k,所以k+1=cur/pre,即k=k+1。

27.cur=pre k=0增益没有增长,

28.cur>pre k>0增益正向增长,

29.cur<pre k<0增益负向增长;

30.可以通过k值的正负判断增益是上升还是下降。

31.在数字域电路中加入了自校准反馈模块,将整个系统模拟域电路和数字域电路组成一个闭合环路系统,将数字反馈输出v_gain作为调节值,送入算法v(i+1)=v(i)

‑

/+dig_sns*dig_res*u对反馈值进行收敛,其中v(i)为当前的反馈值,v(i+1)为下一时刻的反馈值,dig_sns为辅助adc对节点量化输出,dig_res为主adc的量化值输出,u为步长,,关于收敛方向选择

‑

/+选择,可通过[0006]中k值进行判断,这样就可以使数字反馈v_gain调节模拟域的级间增益朝增长的方向变化,即使增益随v_gain的变化曲线发生变化,也可以使其一直处于一个最大增益区间波动。其中鉴于v_gain在模拟域调节的电压范围为0v~~1.8v,采用9数据来进行量化,最小精度为3.51mv。

[0032]

在模拟域电路中加入了反馈信号控制运放正反馈电路,运放内正反馈强弱与增益呈现为类开口向下的抛物线关系是这种方法能够实现的基础,必然可以找到一个较好的工作区域使其工作在最高增益下。该电路包括一个子dac和一个控制运放正反馈电路,子adc的作用是将数字反馈信号转为模拟信号,将9的数字信号转化为一个0v到1.8v的模拟信号;控制运放正反馈电路作用是将转化后的模拟信号引入到运算放大器电路中,通过改变运算放大器内部的正反馈强弱来改变运算放大器的工作点。

[0033]

本发明通过以上几个模块电路将模拟域和数字域电路闭合成环路,通过最小梯度下降算法,对整个环路收敛,调节运算放大器内部的正反馈强弱,使其工作在较高增益下,从而减少级间增益因有限增益问题带来的误差,同时因处于较高增益下,又可以间接地减少因寄生电容,电容失配及反馈电容带来的误差。

[0034]

如图1所示,为adc芯片的数字域与模拟域电路结构图,图中在模拟域adc结构采用了pipeline型adc设计,此外加入了一个结构相同级数较少的辅助adc设计aux_adc,工作频

率为主adc的二十分之一,目的是量化主adc第一级节点电压;还加入了一个子dac(sub_dac),目的是将数字反馈信号转化为模拟信号来影响运放增益;在数字域,加入了算法电路,来自动调节反馈信号v_gain。

[0035]

如图2所示,为模拟域加入辅助adc电路结构图,输入信号通过采样电容后,在sub_adc进行量化,然后经过sub_dac再将量化信号转为模拟信号,将原信号除去第一级的量化信号,转为第一级的余量信号,将余量信号经过级间运放后送入后级进入量化,同时也将节点信号经过运算放大器gs送入辅助adc进行量化,其中运算放大器gs为2个简单的8倍运算放大器级联而成,辅助adc工作在主频率二十分之一频率下。

[0036]

如图3所示,为在模拟域加入反馈电路结构图,所示电路左上侧为di为该级输出,通过di控制量化开关输出余量输出值,图左下侧为dither信号的注入结构电路,然后两者结果之和送入运算放大器中进行信号放大,在结构右下侧加入了一个9bit的子dac(sub_dac),作用是将数字计算出来的收敛信号转化为模拟信号来控制模拟域运算,该信号通过改变运算放大器内部的正反馈的大小来进行间接控制运算放大器的增益大小,图中结构位置则无具体标准根据实际设计变化。

[0037]

如图4所示,为数字域反馈校准的框图,主要部分为虚线框部分是整个反馈校准的核心,在送入之前需要对主adc的量化结果和辅助adc的量化结果进行处理,因为工作在不同频率下,首先需要将同一个节点的量化值进行对齐,然后将结果通入高通滤波器,滤去直流分量,防止直流分量的导致的不可收敛问题,将处理过的数据送入反馈校准的模块,进行计算处理返回收敛值。

[0038]

如图5所示,为运放增益收敛算法实现结构图,目的为实现当前运算放大器增益的收敛,整个结构图为算法的实现,同时设置了可变步长,可相应调节精度及收敛速度。

[0039]

如图6所示,为模拟域运算放大器增益变化曲线,根据实际测量运算放大器的曲线变化大致为如图所示,但因电压、温度等工作环境的变化曲线也会发生左右上下移动,这个规律就是整个设计发明的基础,图中假设初始为a点,v_gain值为变大的方向收敛,到达b点,此时通过a,b两点进行比较可以看出是增益在变大的方向变化,则保持v_gain的变化方向不变,如果设初始为c点,v_gain值为变大的方向,到达d点,此时通过c,d两点进行比较可以看出增益在变小的方向变化,则需要改变v_gain的变化方向,让其从d点返回c点,此为设计的基本原理,通过最小梯度下降法,引入增长趋势因子,通过最小梯度下降算法收敛这个趋势因子,当趋势因子大于一,则v_gain收敛方向不变,否则,收敛方向改变。

[0040]

如图7所示,为数字域自校准反馈模块,自校准反馈模块包括有反馈控制器,模拟域为数字域电路提供adc输出和辅助adc输出,adc输出和辅助adc输出经高通滤波器滤波,输入到模拟反馈器内进行运放增益收敛,求增益斜率,模拟反馈之后,经dac转换为模拟信号输送到运算放大器内进行运算,放大之后的模拟信号输入到模拟域中的主adc内,该模块是将整个系统进行最小梯度下降算法进行收敛,v(i+1)=v(i)

‑

/+dig_sns*dig_res*u,其中dig_res为主adc的余量量化值输出,dig_sns为辅助adc的节点量化值输出,通过判断[0024]进入的增长趋势因子来判断反馈值v的变化方向。

[0041]

以上具体实施方式仅为本发明的示例性实施方式,不能用于限定本发明,本发明的保护范围由权利要求书限定。本领域工程师可以在本发明的实质和保护范围内,对发明做出各种修改和等同替换,这些修改和等同替换也应视为在本发明的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1