时钟数据恢复器的制作方法

1.本发明涉及一种转换检测器和包括该转换检测器的时钟数据恢复器。

背景技术:

2.在发送器与接收器通过单个信道(single channel)连接的收发系统中,导致信号质量劣化(degradation)的主要噪声是符号间干扰(isi:inter

‑

symbol interference)。

3.在发送器与接收器通过多个信道连接的高速并行链路系统(high

‑

speed parallel link system)中,除了符号间干扰之外,还会发生串扰引起的抖动(cij:crosstalk

‑

induced jitter)。

4.由于在接收器侧使用分别与多个信道对应的多个时钟数据恢复器(clock data recovery units),因此时钟数据恢复器所需要的芯片面积(chip area)较宽,并且存在功耗及构成成本上升的问题。

5.时钟数据恢复器为了恢复时钟信号而需要转换检测器,现有的转换检测器为了进行转换检测而利用数字数据。因此,由于现有的转换检测器仅能够检测特定单位间隔(ui:unit interval)而不是发生转换的特定时间点,因此在恢复对符号间干扰及串扰引起的抖动具有鲁棒性的时钟信号方面存在限制。

技术实现要素:

6.所要解决的技术问题在于提供一种能够恢复对符号间干扰及串扰引起的抖动具有鲁棒性的时钟信号的转换检测器和包括该转换检测器的时钟数据恢复器。

7.根据本发明的一实施例的一种时钟数据恢复器包括:相位校正器,基于外部时钟信号生成第一补偿时钟信号及第二补偿时钟信号;以及转换检测器,其中,所述转换检测器包括:第一积分器,根据所述第一补偿时钟信号对第一训练样式信号进行积分而提供第一积分信号;以及第二积分器,根据所述第二补偿时钟信号对所述第一训练样式信号进行积分而提供第二积分信号,其中,当所述第一积分信号大于第一基准电压且所述第二积分信号小于所述第一基准电压时,所述转换检测器检测所述第一训练样式信号的转换的发生。

8.所述第二补偿时钟信号的相位可以比所述第一补偿时钟信号的相位延迟。

9.所述转换检测器还可以包括:第一比较器,在所述第一积分信号大于所述第一基准电压的情况下输出逻辑值1,而在所述第一积分信号小于所述第一基准电压的情况下输出逻辑值0;以及第二比较器,在所述第二积分信号大于所述第一基准电压的情况下输出逻辑值1,而在所述第二积分信号小于所述第一基准电压的情况下输出逻辑值0。

10.所述转换检测器还可以包括:第一反相器,接收所述第二比较器的输出值。

11.所述转换检测器还可以包括:第一与非门,基于所述第一比较器及所述第一反相器的输出值输出第一检测信号。

12.所述转换检测器还可以包括:第一模式信号保持部,对应于导通电平的初始化信号提供训练模式的第一模式信号,其中,所述第一模式信号保持部对应于在接收导通电平

的所述初始化信号之后的第一个导通电平的所述第一检测信号来提供正常模式的所述第一模式信号,并且之后与所述第一检测信号的电平变动无关地保持所述正常模式的所述第一模式信号。

13.所述第一模式信号保持部可以包括:第一晶体管,栅极电极接收所述第一检测信号,一电极连接到第一电源,另一电极连接到第一感测节点;第二晶体管,一电极连接到所述第一电源,另一电极连接到所述第一感测节点;第三晶体管,栅极电极接收所述初始化信号,一电极连接到所述第一感测节点,另一电极连接到第二电源;以及第二反相器,输入端连接到所述第一感测节点,输出端连接到所述第二晶体管的栅极电极。

14.所述第一模式信号保持部还可以包括:第三反相器,输入端连接到所述第一感测节点;以及第四反相器,输入端与所述第三反相器的输出端连接,并且输出所述第一模式信号。

15.所述转换检测器还可以包括:第三积分器,根据第三补偿时钟信号对第二训练样式信号进行积分而提供第三积分信号;以及第四积分器,根据第四补偿时钟信号对所述第二训练样式信号进行积分而提供第四积分信号,其中,当所述第三积分信号小于第二基准电压且所述第四积分信号大于所述第二基准电压时,检测所述第二训练样式信号的转换的发生。

16.所述转换检测器还可以包括:第三比较器,在所述第三积分信号大于所述第二基准电压的情况下输出逻辑值1,而在所述第三积分信号小于所述第二基准电压的情况下输出逻辑值0;以及第四比较器,在所述第四积分信号大于所述第二基准电压的情况下输出逻辑值1,而在所述第四积分信号小于所述第二基准电压的情况下输出逻辑值0。

17.所述转换检测器还可以包括:第五反相器,接收所述第三比较器的输出值;以及第二与非门,基于所述第五反相器及所述第四比较器的输出值输出第二检测信号。

18.所述转换检测器还可以包括:第二模式信号保持部,对应于导通电平的所述初始化信号提供训练模式的第二模式信号,其中,所述第二模式信号保持部对应于在接收导通电平的所述初始化信号之后的第一个导通电平的所述第二检测信号来提供正常模式的所述第二模式信号,并且之后与所述第二检测信号的电平变动无关地保持所述正常模式的所述第二模式信号。

19.所述第二模式信号保持部可以包括:第四晶体管,栅极电极接收所述第二检测信号,一电极连接到所述第一电源,另一电极连接到第二感测节点;第五晶体管,一电极连接到所述第一电源,另一电极连接到所述第二感测节点;第六晶体管,栅极电极接收所述初始化信号,一电极连接到所述第二感测节点,另一电极连接到所述第二电源;以及第六反相器,输入端连接到所述第二感测节点,输出端连接到所述第五晶体管的栅极电极。

20.所述第二模式信号保持部还可以包括:第七反相器,输入端连接到所述第二感测节点;以及第八反相器,输入端与所述第七反相器的输出端连接,并且输出所述第二模式信号。

21.所述第一训练样式信号可以在1周期中的1单位间隔期间包括下降脉冲,所述第二训练样式信号在1周期中的1单位间隔期间包括上升脉冲。

22.所述第一训练样式信号可以在1周期中的除了1单位间隔之外的剩余单位间隔期间保持高电平,所述第二训练样式信号在1周期中的除了1单位间隔之外的剩余单位间隔期

间保持低电平。

23.根据本发明的一实施例的一种时钟数据恢复器包括:相位校正器,基于外部时钟信号生成第一补偿时钟信号及第二补偿时钟信号;以及转换检测器,其中,所述转换检测器包括:第一积分器,根据所述第一补偿时钟信号对第一训练样式信号进行积分而提供第一积分信号;以及第二积分器,根据所述第二补偿时钟信号对所述第一训练样式信号进行积分而提供第二积分信号,其中,当所述第一积分信号小于第一基准电压且所述第二积分信号大于所述第一基准电压时,所述转换检测器检测所述第一训练样式信号的转换的发生。

24.根据本发明的一实施例的一种时钟数据恢复器包括:相位校正器,基于外部时钟信号生成第一补偿时钟信号及第二补偿时钟信号;以及转换检测器,其中,所述转换检测器包括:第一积分器,根据所述第一补偿时钟信号对第一训练样式信号进行积分而提供第一积分信号;以及第二积分器,根据相位比所述第一补偿时钟信号延迟的所述第二补偿时钟信号对所述第一训练样式信号进行积分而提供第二积分信号,其中,当所述第一积分信号大于第一基准电压且所述第二积分信号小于所述第一基准电压时,将所述第二补偿时钟信号的相位存储为第一相位。

25.所述转换检测器还可以包括:第三积分器,根据第三补偿时钟信号对第二训练样式信号进行积分而提供第三积分信号;以及第四积分器,根据所述第四补偿时钟信号对所述第二训练样式信号进行积分而提供第四积分信号,其中,当所述第三积分信号小于第二基准电压且所述第四积分信号大于所述第二基准电压时,将所述第四补偿时钟信号的相位存储为第二相位。

26.所述时钟数据恢复器可以在所述第一相位相比于所述第二相位延迟的情况下提供所述第二补偿时钟信号作为采样时钟信号,而在所述第二相位相比于所述第一相位延迟的情况下提供所述第四补偿时钟信号作为所述采样时钟信号。

27.所述第一训练样式信号可以在1周期中的1单位间隔期间包括下降脉冲并且在1周期中的剩余单位间隔期间保持高电平,所述第二训练样式信号在1周期中的1单位间隔期间包括上升脉冲并且在1周期中的剩余单位间隔期间保持低电平。

28.根据本发明的转换检测器和包括该转换检测器的时钟数据恢复器能够恢复对符号间干扰及串扰引起的抖动具有鲁棒性的时钟信号。

附图说明

29.图1是用于说明根据本发明的一实施例的接收器以及包括该接收器的收发器的图。

30.图2是用于说明针对一发送信号的接收信号的图。

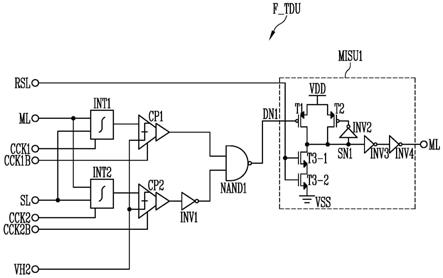

31.图3是用于说明针对另一发送信号的接收信号的图。

32.图4是用于说明根据本发明一实施例的接收单元的图。

33.图5是用于说明根据相邻信道的相邻接收信号与对象信道的接收信号的关系的模式的图。

34.图6是用于说明由相邻接收信号导致的串扰引起的抖动的图。

35.图7是用于说明由相邻接收信号导致的串扰引起的抖动的另一示例的图。

36.图8是用于说明根据两个相邻信道的相邻接收信号与对象信道的接收信号的关系

的串扰引起的抖动的图。

37.图9是用于说明在训练模式下通过信道接收具有相同的第一转换方向的第一训练样式信号的理由的图。

38.图10是用于说明在训练模式下通过信道接收具有相同的第二转换方向的第二训练样式信号的理由的图。

39.图11及图12是用于说明利用信道的第一训练样式信号中的感测信道的第一训练样式信号来恢复时钟信号的理由的图。

40.图13及图14是用于说明利用信道的第二训练样式信号中的感测信道的第二训练样式信号来恢复时钟信号的理由的图。

41.图15是用于说明根据本发明的一实施例的时钟数据恢复器的图。

42.图16是用于说明根据本发明的一实施例的转换检测器的图。

43.图17是用于说明可用于图16的转换检测器的示例性的第一训练样式信号的图。

44.图18至图20是用于说明基于第一训练样式信号的图16的转换检测器的操作的图。

45.图21是用于说明根据本发明的另一实施例的转换检测器的图。

46.图22是用于说明可用于图21的转换检测器的示例性的第二训练样式信号的图。

具体实施方式

47.以下,参考附图对本发明的多个实施例进行详细说明,以使在本发明所属技术领域中具有基本知识的人可以容易地实施。本发明可以实现为多种不同的形态,且不限于在此说明的实施例。

48.为了明确说明本发明,省略了与说明无关的部分,并且贯穿整个说明书,对相同或者相似的构成要素赋予了相同的附图标记。因此,上文所述的附图标记也可以用于不同的附图。

49.并且,为了便于说明,任意地示出了附图中示出的各个构成的大小以及厚度,因此本发明并不局限于图示的内容。附图中为了明确表达多个层以及区域,放大示出了厚度。

50.图1是用于说明根据本发明的一实施例的接收器以及包括该接收器的收发器的图。

51.参照图1,根据本发明的一实施例的收发器tcs包括发送器dv1及接收器dv2。

52.发送器dv1包括与对应的信道ch1~ch(2n

‑

1)连接的发送单元tx1~tx(2n

‑

1)。

53.接收器dv2包括与对应的信道ch1~ch(2n

‑

1)连接的接收单元rx1~rx(2n

‑

1)。

54.并且,接收器dv2包括时钟数据恢复器cdr。时钟数据恢复器cdr可以通过感测线sl与信道ch1~ch(2n

‑

1)中的感测信道chn连接,并且通过时钟线cl与接收单元rx1~rx(2n

‑

1)连接。根据实施例,时钟数据恢复器cdr可以通过模式线ml与发送单元tx1~tx(2n

‑

1)连接。

55.收发器tcs可以在训练模式(training mode)及正常模式(normal mode)中的一种模式下操作。训练模式是用于时钟数据恢复器cdr生成采样时钟信号的模式,正常模式是用于利用生成的采样时钟信号对数据信号进行采样的模式。在训练模式期间,可以通过信道ch1~ch(2n

‑

1)发送训练样式信号,而在正常模式期间,可以通过信道ch1~ch(2n

‑

1)发送数据信号。

56.首先,对训练模式进行说明。

57.在一实施例中,接收单元rx1~rx(2n

‑

1)可以在训练模式下通过信道ch1~ch(2n

‑

1)接收具有彼此相同的转换方向(transition direction)的训练样式信号(training pattern signals)。

58.此时,时钟数据恢复器cdr可以在训练模式下生成相位得到调节的采样时钟信号,使得感测信道chn的训练样式信号的转换时间点与采样时间点对应。根据实施例,在生成采样时钟信号的情况下,时钟数据恢复器cdr可以通过模式线ml提供与正常模式对应的模式信号。

59.在另一实施例中,接收单元rx1~rx(2n

‑

1)可以在训练模式下通过信道ch1~ch(2n

‑

1)接收具有彼此相同的第一转换方向的第一训练样式信号以及具有彼此相同的第二转换方向的第二训练样式信号。此时,第一转换方向与第二转换方向可以彼此不同。

60.此时,时钟数据恢复器cdr可以在训练模式下生成采样时钟信号,使得生成的采样时钟信号对应于与感测信道chn的第一训练样式信号的第一转换时间点对应的第一采样时间点和与第二训练样式信号的第二转换时间点对应的第二采样时间点中更延迟的相位。

61.以下,对正常模式进行说明。

62.发送单元tx1~tx(2n

‑

1)可以在接收到与正常模式对应的模式信号的情况下通过对应的信道ch1~ch(2n

‑

1)提供各个数据信号。

63.时钟数据恢复器cdr可以在正常模式下通过时钟线cl将采样时钟信号供应给接收单元rx1~rx(2n

‑

1)。

64.接收单元rx1~rx(2n

‑

1)可以在正常模式下利用采样时钟信号对通过对应的信道ch1~ch(2n

‑

1)接收到的各个数据信号进行采样。

65.根据本实施例,对于多个信道ch1~ch(2n

‑

1)中的每一个不需要时钟数据恢复器,仅需要针对感测信道chn的一个时钟数据恢复器cdr,因此可以减少芯片所需面积并降低功耗。

66.后文将参照图11至图14说明如下内容:即使基于一个感测信道chn生成关于多个信道ch1~ch(2n

‑

1)的采样时钟信号,在数据采样中也不存在问题。

67.此时,重要的是确定多个信道ch1~ch(2n

‑

1)中的感测信道chn。根据一实施例,感测信道chn可以是信道ch1~ch(2n

‑

1)中针对相同发送信号而言接收具有最慢相位的接收信号的信道。根据另一实施例,感测信道chn可以是信道ch1~ch(2n

‑

1)中位于最中间的信道。

68.在此,n可以是2以上的正整数。但是,在图1中,最后一个信道ch(2n

‑

1)被图示为第(2n

‑

1)个信道,即,奇数信道,但是本实施例也可以应用于最后一个信道为第偶数个信道的情况。例如,最后一个信道也可以是第2n个信道。例如,在感测信道chn为第四个信道的情况下,最后一个信道可以是第八个信道。并且,在最后一个信道为第八个信道的情况下,感测信道chn也可以是第五个信道。

69.即,对于本实施例中确定感测信道chn而言,重要的并不是感测信道chn为第几个信道,重要的是将信道ch1~ch(2n

‑

1)中针对相同的发送信号而言接收具有最慢相位的接收信号的信道确定为感测信道chn。

70.在信道ch1~ch(2n

‑

1)的物理结构在平面上平行地简单布置的情况下,感测信道

chn可以是信道ch1~ch(2n

‑

1)中位于最中间的信道。但是,在信道ch1~ch(2n

‑

1)被提供为立体结构的情况下(例如,在多个信道成束存在于配线护套内部的情况下),制造商(manufacturer)可以以预先传送样本训练信号的方式找出接收具有最慢相位的接收信号的信道,并将该信道确定为感测信道chn。即,可以针对每个产品不同地确定感测信道chn。

71.并且,后文将参照图6至图14说明在根据本实施例的情况下能够有效地解决串扰引起的抖动问题,并且后文将参照图17及图22说明能够有效地解决符号间干扰问题。

72.图2是用于说明针对一发送信号的接收信号的图,图3是用于说明针对另一发送信号的接收信号的图。

73.在图2及图3中,假设为不存在串扰引起的抖动的情况。在图2及图3中,相邻采样时间点之间的间隔为1个单位间隔(ui:unit interval)。

74.在图2及图3中,接收信号的可变电平可以为最低电平ll1以上、最高电平hl1以下中的一个。在最低电平ll1与最高电平hl1之间存在中间电平il1。此时,假设接收信号通过的信道是理想的。关于理想信道和实际信道之间的差异,参照与图17及图22相关的说明。

75.参照图2,示例性地图示了当从发送器dv1通过任意一个信道发送二进制电平(binary level)为0、1、0的发送信号时通过信道的接收器dv2的接收信号fr_a。假设图2中未图示的发送信号的剩余数据为二进制电平0。

76.可以在信道被设计为低通滤波器(low pass filter)的情况下获取如图2所示的接收信号fr_a的形态。因此,根据一实施例,连接发送器dv1与接收器dv2的多个信道ch1~ch(2n

‑

1)中的每一个可以被设计为低通滤波器。

77.遵循如图2所示的响应形态的接收信号可以被称为双二进制信号(duo

‑

binary signal)。除了信道被设计为低通滤波器的情况之外,在发送器dv1具有用于双二进制信令的编码器的情况下,也可以出现如图2所示的响应形态。

78.虽然存在多种双二进制信令方法,但是在图2的接收信号fr_a的情况下,通常,采样时间点sp1_a的标记为前标记(pre

‑

cursor),采样时间点sp2_a的标记为主标记(main

‑

cursor),采样时间点sp3_a的标记为第一后标记(1st post

‑

cursor),采样时间点sp4_a的标记为第二后标记(2st post

‑

cursor)。为了适当地应用双二进制信令,可以使用使主标记和第一后标记的电平(大小)能够相同的已知的多种方法。

79.参照图3,示例性地图示了当从发送器dv1通过任意一个信道发送二进制电平(binary level)为0、1、1、0的发送信号时通过信道的接收器dv2的接收信号spr_b。假设图3中未图示的发送信号的剩余数据为二进制电平0。

80.在图3中,接收信号spr_b可以被视为与第一个二进制电平1对应的响应信号fr_b和与第二个二进制电平1对应的响应信号sr_b的重叠信号。在响应信号fr_b的情况下,通常,采样时间点sp1_b的标记为前标记,采样时间点sp2_b的标记为主标记,采样时间点sp3_b的标记为第一后标记,采样时间点sp4_b的标记为第二后标记。在响应信号sr_b的情况下,通常,采样时间点sp2_b的标记为前标记,采样时间点sp3_b的标记为主标记,采样时间点sp4_b的标记为第一后标记,采样时间点sp5_b的标记为第二后标记。

81.以下,参照图2及图3对针对双二进制信号的解码方法进行说明。

82.当执行针对双二进制信号的解码时,可能需要1ui先前数据的确定值。在1ui先前数据的确定值为1的情况下,当确定当前数据时可以使用第一基准电压vh1。并且,在1ui先

前数据的确定值为0的情况下,当确定当前数据时可以使用第二基准电压vl1。第一基准电压vh1可以具有接收信号的可变电平中的最高电平hl1与中间电平il1之间的中间值。第二基准电压vl1可以具有接收信号的可变电平中的最低电平ll1与中间电平il1之间的中间值。

83.例如,参照图2,在采样时间点sp2_a,1ui先前数据的确定值为0,因此可以以第二基准电压vl1为基准来确定当前数据的二进制电平。由于在采样时间点sp2_a处采样的接收信号的电平为中间电平il1且其高于第二基准电压vl1,因此二进制电平可以被确定为1。

84.接下来,参考图2,在采样时间点sp3_a,1ui先前数据的确定值为1,因此可以以第一基准电压vh1为基准来确定当前数据的二进制电平。由于在采样时间点sp3_a处采样的接收信号的电平为中间电平il1且其低于第一基准电压vh1,因此二进制电平可以被确定为0。

85.又例如,参照图3,在采样时间点sp2_b,1ui先前数据的确定值为0,因此可以以第二基准电压vl1为基准来确定当前数据的二进制电平。由于在采样时间点sp2_b处采样的接收信号的电平为中间电平il1且其高于第二基准电压vl1,因此二进制电平可以被确定为1。

86.接下来,参考图3,在采样时间点sp3_b,1ui先前数据的确定值为1,因此可以以第一基准电压vh1为基准来确定当前数据的二进制电平。由于在采样时间点sp3_b处采样的接收信号的电平为最高电平hl1且其高于第一基准电压vh1,因此二进制电平可以被确定为1。

87.接下来,参考图3,在采样时间点sp4_b,1ui先前数据的确定值为1,因此可以以第一基准电压vh1为基准来确定当前数据的二进制电平。由于在采样时间点sp4_b处采样的接收信号的电平为中间电平il1且其低于第一基准电压vh1,因此二进制电平可以被确定为0。

88.将上述确定方法具体化的是根据图4的接收单元rxi。

89.图4是用于说明根据本发明一实施例的接收单元的图。

90.虽然图4以第i个信道chi为基准图示了接收单元rxi,但是相同的内容也可以应用于其他信道及接收单元。i可以为正整数。若第i个信道chi为感测信道chn,则接收单元rxi还可以与感测线sl连接。

91.参考图4,接收单元rxi可以包括第一比较器cmp1、第二比较器cmp2及复用器mux。

92.第一比较器(comparator)cmp1可以根据通过时钟线cl供应的采样时钟信号对接收信号及第一基准电压vh1进行比较而提供逻辑值。接收信号可以通过信道chi接收。第一比较器cmp1可以根据采样时钟信号的上升转换(rising transition)或下降转换(falling transition)进行操作,对该采样时间点处的接收信号的大小进行采样并将其与第一基准电压vh1进行比较。在另一实施例中,第一比较器cmp1可以利用在采样时钟信号的高电平时段(high level period)或低电平时段(low level period)积分的接收信号的大小而与第一基准电压vh1进行比较。若接收信号大于第一基准电压vh1,则第一比较器cmp1可以提供高电平的逻辑值,而若接收信号小于第一基准电压vh1,则第一比较器cmp1可以提供低电平的逻辑值。

93.第二比较器cmp2可以根据采样时钟信号对接收信号及第二基准电压vl1进行比较而提供逻辑值。接收信号可以通过信道chi接收。第二比较器cmp2可以根据采样时钟信号的上升转换或下降转换进行操作,对该采样时间点处的接收信号的大小进行采样并将其与第二基准电压vl1进行比较。在另一实施例中,第二比较器cmp2可以利用在采样时钟信号的高电平时段或低电平时段积分的接收信号的大小而与第二基准电压vl1进行比较。若接收信

号大于第二基准电压vl1,则第二比较器cmp2可以提供高电平的逻辑值,而若接收信号小于第二基准电压vl1,则第二比较器cmp2可以提供低电平的逻辑值。

94.复用器(multiplexer)mux可以输出第一比较器cmp1及第二比较器cmp2的输出值中的一个作为当前数据d[m]。复用器mux可以以1ui之前的过去数据d[m

‑

1]为基准选择第一比较器cmp1及第二比较器cmp2的输出值中的一个作为当前数据d[m]而输出。具体而言,在过去数据d[m

‑

1]为二进制电平1的情况下,可以输出第一比较器cmp1的输出值作为当前数据d[m]。相反,在过去数据d[m

‑

1]为二进制电平0的情况下,可以输出第二比较器cmp2的输出值作为当前数据d[m]。在复用器mux的输出值为高电平的逻辑值的情况下,当前数据d[m]的二进制电平可以为1,而在复用器mux的输出值为低电平的逻辑值的情况下,当前数据d[m]的二进制电平可以为0。

[0095]

图5是用于说明根据相邻信道的相邻接收信号与对象信道的接收信号的关系的模式的图。

[0096]

当对串扰引起的抖动进行说明时,对象信道被称为牺牲信道(victim),并且对牺牲信道造成不利影响的相邻信道被称为加害信道(aggressor)。在本说明中,假设作为牺牲信道的对象信道为信道ch2,加害信道为信道ch1。

[0097]

另一方面,在信道ch2中引起的串扰引起的抖动对信道ch1产生不利影响,该不利影响可能会再次返回到信道ch2,但在这种情况下,影响比较微弱并且说明会变得过于复杂,因此省略对此的说明。

[0098]

将牺牲信道ch2与加害信道ch1的转换方向彼此不同的情况称为奇数模式(odd mode)。如图5所示,可能存在两种情况。

[0099]

将牺牲信道ch2与加害信道ch1的转换方向彼此相同的情况称为偶数模式(even mode)。如图5所示,可能存在两种情况。

[0100]

相反,将在信道中不存在转换的情况称为静态模式(static mode)。在图5中,与牺牲信道ch2的转换方向无关,在加害信道ch1中都没有转换。在这种情况下,如图5所示,可能存在两种情况。

[0101]

图6是用于说明由相邻接收信号导致的串扰引起的抖动的图,图7是用于说明由相邻接收信号导致的串扰引起的抖动的另一示例的图。

[0102]

参考图6,图示了牺牲信道ch2和加害信道ch1全部上升转换的偶数模式的情形。

[0103]

若在加害信道ch1中发生上升转换,则两个信道ch1、ch2之间的互感(mutual

‑

inductance)导致在牺牲信道ch2中发生沿作为其相反方向的下方的电压下降。

[0104]

因此,为了使牺牲信道ch2的电压重新上升,还需要一定时间,这样发生的延迟(delay)成为在偶数模式下的串扰引起的抖动。

[0105]

参考图7,图示了牺牲信道ch2和加害信道ch1全部下降转换的偶数模式的情形。

[0106]

若在加害信道ch1中发生下降转换,则两个信道ch1、ch2之间的互感(mutual

‑

inductance)导致在牺牲信道ch2中发生沿作为其相反方向的上方的电压上升。

[0107]

因此,为了使牺牲信道ch2的电压重新下降,还需要一定时间,这样发生的延迟(delay)成为在偶数模式下的串扰引起的抖动。

[0108]

结果,在偶数模式下,与该转换方向无关,发生牺牲信道ch2的接收信号延迟的串扰引起的抖动。

[0109]

在奇数模式的情况下,可能发生与偶数模式相反方向的串扰引起的抖动,省略其说明。作为参考,在静态模式下,可能不会发生串扰引起的抖动。

[0110]

图8是用于说明根据两个相邻信道的相邻接收信号与对象信道的接收信号的关系的串扰引起的抖动的图。

[0111]

在本说明中,假设作为牺牲信道的对象信道为信道ch2,加害信道为信道ch1、ch3。

[0112]

另一方面,在信道ch2中引起的串扰引起的抖动对信道ch1、ch3产生不利影响,该不利影响可能会再次返回到信道ch2,但在这种情况下,影响比较微弱并且说明会变得过于复杂,因此省略对此的说明。

[0113]

将牺牲信道ch2与两个加害信道ch1、ch3的转换方向彼此相同的情况称为2

‑

偶数模式(2

‑

even mode)。如图8所示,可能存在信道ch1、ch2、ch3的信号全部具有上升转换的情形2em_a和信道ch1、ch2、ch3的信号全部具有下降转换的情形2em_b这两种。

[0114]

参照图8所示,可以确认如下内容:在两个加害信道ch1、ch3沿相同方向发生转换的情况下,发生最大的串扰引起的抖动,仅在一个加害信道发生转换的情况下,发生较小的串扰引起的抖动,在两个加害信道ch1、ch3沿彼此相反的方向发生转换的情况下,彼此抵消而不会发生串扰引起的抖动。

[0115]

将相邻的两个加害信道ch1、ch3的转换方向彼此相同但与牺牲信道ch2的转换方向相反的情况称为2

‑

奇数模式(2

‑

odd mode)。参照图8,图示了两种情况(2om_a、2om_b)。在这种情况下,串扰引起的抖动的方向与2

‑

偶数模式的方向相反。

[0116]

在相邻的两个加害信道ch1、ch3未发生转换的情况为静态模式。

[0117]

图9是用于说明在训练模式下通过信道接收具有相同的第一转换方向的第一训练样式信号的理由的图。

[0118]

以下,第一转换方向可以表示下降转换方向。并且,第二转换方向可以表示上升转换方向。

[0119]

为了对此进行说明,再次参照图2及图3,可知如下的双二进制信令的特征。在二进制电平从0转换到1的上升转换的情况下以及二进制电平从1转换到0的下降转换的情况下,采样的接收信号的电平全部为中间电平il1。

[0120]

例如,参照图2的发送信号,二进制电平从0上升转换为1,然后立即从1下降转换为0。此时,参照图2的接收信号fr_a,在与各个转换对应的采样时间点sp2_a、sp3_a处采样的接收信号的电平全部为中间电平il1。

[0121]

并且,例如,参照图3的发送信号,二进制电平从0上升转换为1,然后在1ui期间保持1,之后下降转换为0。此时,参照图3的接收信号spr_b,在与各个转换对应的采样时间点sp2_b、sp4_b处采样的接收信号的电平全部为中间电平il1。

[0122]

在本实施例中,可以基于双二进制信令的这样的特性来执行对串扰引起的抖动的补偿。

[0123]

再次参照图9,概念性地图示了1ui先前信号为二进制电平1且当前信号为二进制电平0的情形。即,下降转换的情形。图9所示的并非实际信号,且为了容易理解,概念性地分离了对各个二进制数据的响应并对其进行夸张图示。例如,图9的采样时间点sp_fs可以对应于图2的采样时间点sp3_a,图9的先前信号prv_s_a与当前信号curr_s_a重叠的信号可以是图2的在采样时间点sp3_a处的接收信号fr_a。

[0124]

图9的先前信号prv_o_a、prv_s_a、prv_e_a分别为在奇数模式、静态模式、偶数模式的情况下对二进制电平1的单比特响应(single bit response),为了明确地示出信号,假设为前后的二进制数据为电平0的情况。

[0125]

图9的当前信号curr_o_a、curr_s_a、curr_e_a分别为在奇数模式、静态模式、偶数模式的情况下对二进制电平0的单比特响应,并且假设为前后的二进制数据为电平1的情况。

[0126]

采样时间点sp_fs是以静态模式为基准相位被调节的采样时钟信号clk_fs的采样时间点,采样时间点sp_fe是以偶数模式为基准相位被调节的采样时钟信号clk_fe的采样时间点。

[0127]

在接收信号为静态模式并利用采样时钟信号clk_fs在采样时间点sp_fs进行采样的情况下,1ui先前信号prv_s_a的第一后标记与当前信号curr_s_a的主标记之和为中间电平il1。由于先前信号prv_s_a的二进制电平为1,因此当判断当前信号curr_s_a时使用第一基准电压vh1。由于1ui先前信号prv_s_a的第一后标记与当前信号curr_s_a的主标记之和为中间电平il1且低于第一基准电压vh1,因此可以将当前信号curr_s_a确定为二进制电平0。

[0128]

相反,在接收信号为偶数模式并利用采样时钟信号clk_fs在采样时间点sp_fs进行采样的情况下,1ui先前信号prv_e_a的第一后标记与当前信号curr_e_a的主标记之和高于中间电平il1。由于先前信号prv_e_a的二进制电平为1,因此在判断当前信号curr_e_a时使用第一基准电压vh1。由于1ui先前信号prv_e_a的第一后标记与当前信号curr_e_a的主标记之和低于第一基准电压vh1,因此当前信号curr_e_a应该被确定为二进制电平0,但是存在裕度fm1太小的问题。根据通信环境,在1ui先前信号prv_e_a的第一后标记与当前信号curr_e_a的主标记之和超过第一基准电压vh1的情况下,在解码中发生错误。

[0129]

在接收信号为奇数模式并利用采样时钟信号clk_fs在采样时间点sp_fs进行采样的情况下,1ui先前信号prv_o_a的第一后标记与当前信号curr_o_a的主标记之和低于中间电平il1。由于先前信号prv_o_a的二进制电平为1,因此在判断当前信号curr_o_a时使用第一基准电压vh1。由于1ui先前信号prv_o_a的第一后标记与当前信号curr_o_a的主标记之和充分低于第一基准电压vh1,因此将当前信号curr_o_a的二进制电平确定为0是没有问题的。在这种情况下,反而比静态模式具有更大的裕度。

[0130]

如上文所述,在下降转换的情况下,需要实施补偿的最坏的情况(worst case)为偶数模式的情况。

[0131]

根据本实施例,在训练模式下通过信道ch1~ch(2n

‑

1)可以接收“具有相同的第一转换方向的第一训练样式信号”,即,“偶数模式的具有下降转换方向的第一训练样式信号”。

[0132]

根据本实施例,可以生成相位调节的采样时钟信号clk_fe使得该第一训练样式信号的转换时间点与采样时间点sp_fe对应。可以确认如下内容:在相位调节的采样时间点sp_fe处,在偶数模式的情况下具有充分的裕度fm2。在静态模式和奇数模式的情况下具有更大的裕度,因此没有问题。据此,在遵循采样时钟信号clk_fe的情况下,在所有模式中发生由于串扰引起的抖动而导致的解码错误的概率减小。

[0133]

图10是用于说明在训练模式下通过信道接收具有相同的第二转换方向的第二训

练样式信号的理由的图。

[0134]

参照图10,概念性地图示了1ui先前信号为二进制电平0且当前信号为二进制电平1的情形。即,上升转换的情形。图10所示的并非实际信号,且为了容易理解,概念性地分离了对各个二进制数据的响应并对其进行夸张图示。例如,图10的采样时间点sp_rs可以对应于图2的采样时间点sp2_a,图10的先前信号prv_s_b与当前信号curr_s_b重叠的信号可以是图2的在采样时间点sp2_a处的接收信号fr_a。

[0135]

图10的先前信号prv_o_b、prv_s_b、prv_e_b分别为在奇数模式、静态模式、偶数模式的情况下对二进制电平0的单比特响应,为了明确地示出信号,假设为前后的二进制数据为电平1的情况。

[0136]

图10的当前信号curr_o_b、curr_s_b、curr_e_b分别为在奇数模式、静态模式、偶数模式的情况下对二进制电平1的单比特响应,并且为了明确地示出信号,假设为前后的二进制数据为电平0的情况。

[0137]

采样时间点sp_rs是以静态模式为基准相位被调节的采样时钟信号clk_rs的采样时间点,采样时间点sp_re是以偶数模式为基准相位被调节的采样时钟信号clk_re的采样时间点。

[0138]

在接收信号为静态模式并利用采样时钟信号clk_rs在采样时间点sp_rs进行采样的情况下,1ui先前信号prv_s_b的第一后标记与当前信号curr_s_b的主标记之和为中间电平il1。由于先前信号prv_s_b的二进制电平为0,因此当判断当前信号curr_s_b时使用第二基准电压vl1。由于1ui先前信号prv_s_b的第一后标记与当前信号curr_s_b的主标记之和为中间电平il1且高于第二基准电压vl1,因此可以将当前信号curr_s_b确定为二进制电平1。

[0139]

相反,在接收信号为偶数模式并利用采样时钟信号clk_rs在采样时间点sp_rs进行采样的情况下,1ui先前信号prv_e_b的第一后标记与当前信号curr_e_b的主标记之和低于中间电平il1。由于先前信号prv_e_b的二进制电平为0,因此在判断当前信号curr_e_b时使用第二基准电压vl1。由于1ui先前信号prv_e_b的第一后标记与当前信号curr_e_b的主标记之和高于第二基准电压vl1,因此当前信号curr_e_b应该被确定为二进制电平1,但是存在裕度rm1太小的问题。根据通信环境,在1ui先前信号prv_e_b的第一后标记与当前信号curr_e_b的主标记之和小于第二基准电压vl1的情况下,在解码中发生错误。

[0140]

在接收信号为奇数模式并利用采样时钟信号clk_rs在采样时间点sp_rs进行采样的情况下,1ui先前信号prv_o_b的第一后标记与当前信号curr_o_b的主标记之和高于中间电平il1。由于先前信号prv_o_b的二进制电平为0,因此在判断当前信号curr_o_b时使用第二基准电压vl1。由于1ui先前信号prv_o_b的第一后标记与当前信号curr_o_b的主标记之和充分高于第二基准电压vl1,因此将当前信号curr_o_b的二进制电平确定为1是没有问题的。在这种情况下,反而比静态模式具有更大的裕度。

[0141]

如上文所述,在上升转换的情况下,需要实施补偿的最坏的情况为奇数模式的情况。

[0142]

根据本实施例,在训练模式下通过信道ch1~ch(2n

‑

1)可以接收“具有相同的第二转换方向的第二训练样式信号”,即,“奇数模式的具有上升转换方向的第二训练样式信号”。

[0143]

根据本实施例,可以生成相位被调节的采样时钟信号clk_re使得该第二训练样式信号的转换时间点与采样时间点sp_re对应。可以确认如下内容:在相位被调节的采样时间点sp_re处,在偶数模式的情况下具有充分的裕度rm2。在静态模式和奇数模式的情况下具有更大的裕度,因此没有问题。据此,在遵循采样时钟信号clk_re的情况下,在所有模式中发生由于串扰引起的抖动而造成的解码错误的概率减小。

[0144]

在图9的下降转换的情况和图10的上升转换的情况全部,以偶数模式为基准设定的采样时钟信号clk_fe、clk_re的相位比以静态模式为基准设定的采样时钟信号clk_fs、clk_rs的相位延迟。

[0145]

因此,根据本发明的一实施例,即使在训练模式下仅对第一训练样式信号及第二训练样式信号中的一个实行训练,也可以确保裕度fm2、rm2。

[0146]

根据本发明的另一实施例,可以在训练模式下对第一训练样式信号及第二训练样式信号两者实行训练。在这种情况下,时钟数据恢复器cdr可以将采样时钟信号生成为对应于与第一训练样式信号的第一转换时间点对应的第一采样时间点sp_fe和与第二训练样式信号的第二转换时间点对应的第二采样时间点sp_re中更延迟的相位。这种情况下,在与更快的相位对应的转换的情况下,由于从对应的基准电压进一步确保裕度,因此在解决解码错误问题方面没有问题。

[0147]

虽然图9及图10中记载了根据采样时钟信号的上升转换来执行采样的情形,但是根据产品也可以根据采样时钟信号的下降转换来执行采样。并且,根据产品,在应用电流积分(current integral)方式的采样的情况下,为了确保捕获时间(acquisition time),时钟信号clk_fs、clk_fe、clk_rs、clk_re的转换时间点可以在采样时间点sp_fs、sp_fe、sp_rs、sp_re之前。以下,为了便于说明,将对在采样时钟信号的上升转换处执行采样的情形进行说明。

[0148]

图11及图12是用于说明利用信道的第一训练样式信号中的感测信道的第一训练样式信号来恢复时钟信号的理由的图。

[0149]

以下,假设为以偶数模式提供训练样式信号的情形。

[0150]

即使发送单元tx1~tx(2n

‑

1)发送相同的第一训练样式信号,由于位于中间的感测信道chn受到串扰引起的抖动的影响最大,因此第一训练样式信号chns的相位可能被最大延迟。采样时钟信号clk_f3可以是相位被调节使得第一训练样式信号chns的转换时间点与采样时间点sp_f3对应的信号。

[0151]

通过信道ch(n

‑

1)、ch(n+1)接收的第一训练样式信号ch(n

‑

1)s、ch(n+1)s的相位可以比其他第一训练样式信号的相位延迟并比第一训练样式信号chns的相位快。采样时钟信号clk_f2可以是相位被调节使得第一训练样式信号ch(n

‑

1)s、ch(n+1)s的转换时间点与采样时间点sp_f2对应的信号。

[0152]

位于最外侧的信道ch1、ch(2n

‑

1)受到串扰引起的抖动的影响最小,因此通过信道ch1、ch(2n

‑

1)接收的第一训练样式信号ch1s、ch(2n

‑

1)s的相位可以比其他第一训练样式信号的相位快。采样时钟信号clk_f1可以是相位被调节使得第一训练样式信号ch1s、ch(2n

‑

1)s的转换时间点与采样时间点sp_f1对应的信号。

[0153]

在利用采样时钟信号clk_f1在采样时间点sp_f1进行采样的情况下,信道ch1、ch(2n

‑

1)的先前信号prv_ch1s、prv_ch(2n

‑

1)s的第一后标记与当前信号curr_ch1s、curr_ch

(2n

‑

1)s的主标记之和分别为中间电平il1,与第一基准电压vh1的裕度充分,因此解码为二进制电平0是没有问题的。

[0154]

但是,信道ch(n

‑

1)、ch(n+1)的先前信号prv_ch(n

‑

1)s、prv_ch(n+1)s的第一后标记与当前信号curr_ch(n

‑

1)s、curr_ch(n+1)s的主标记之和以及感测信道chn的先前信号prv_chns的第一后标记与当前信号curr_chns的主标记之和分别超过第一基准电压vh1,因此错误地解码为二进制电平1而发生错误。

[0155]

在利用采样时钟信号clk_f2在采样时间点sp_f2进行采样的情况下,信道ch(n

‑

1)、ch(n+1)的先前信号prv_ch(n

‑

1)s、prv_ch(n+1)s的第一后标记与当前信号curr_ch(n

‑

1)s、curr_ch(n+1)s的主标记之和分别为中间电平il1,与第一基准电压vh1的裕度充分,因此解码为二进制电平0是没有问题的。

[0156]

并且,信道ch1、ch(2n

‑

1)的先前信号prv_ch1s、prv_ch(2n

‑

1)s的第一后标记与当前信号curr_ch1s、curr_ch(2n

‑

1)s的主标记之和分别为中间电平il1以下,因此与第一基准电压vh1的裕度充分,从而解码为二进制电平0是没有问题的。

[0157]

但是,感测信道chn的先前信号prv_chns的第一后标记与当前信号curr_chns的主标记之和与第一基准电压vh1的裕度f2m不足,因此存在错误地解码为二进制电平1的可能性。

[0158]

在利用采样时钟信号clk_f3在采样时间点sp_f3进行采样的情况下,感测信道chn的先前信号prv_chns的第一后标记与当前信号curr_chns的主标记之和分别为中间电平il1,与第一基准电压vh1的裕度f3m充分,因此解码为二进制电平0是没有问题的。对于其他信道ch1、ch(n

‑

1)、ch(n+1)、ch(2n

‑

1)而言,具有与第一基准电压vh1更大的裕度,因此解码为二进制电平0是没有问题的。

[0159]

因此,可以确认如下内容:即使利用串扰引起的抖动最强作用的感测信道chn的第一训练样式信号生成采样时钟信号clk_f3,准确地对其他信道ch1、ch(n

‑

1)、ch(n+1)、ch(2n

‑

1)的数据信号进行采样也是没有问题的。

[0160]

图13及图14是用于说明利用信道的第二训练样式信号中的感测信道的第二训练样式信号来恢复时钟信号的理由的图。

[0161]

以下,假设为以偶数模式提供训练样式信号的情形。

[0162]

即使发送单元tx1~tx(2n

‑

1)发送相同的第二训练样式信号,由于位于中间的感测信道chn受到串扰引起的抖动的影响最大,因此第二训练样式信号chns'的相位可能被最大延迟。采样时钟信号clk_r3可以是相位被调节使得第二训练样式信号chns'的转换时间点与采样时间点sp_r3对应的信号。

[0163]

通过信道ch(n

‑

1)、ch(n+1)接收的第二训练样式信号ch(n

‑

1)s'、ch(n+1)s'的相位可以比其他第二训练样式信号的相位延迟并比第二训练样式信号chns'的相位快。采样时钟信号clk_r2可以是相位被调节使得第二训练样式信号ch(n

‑

1)s'、ch(n+1)s'的转换时间点与采样时间点sp_r2对应的信号。

[0164]

位于最外侧的信道ch1、ch(2n

‑

1)受到串扰引起的抖动的影响最小,因此通过信道ch1、ch(2n

‑

1)接收的第二训练样式信号ch1s'、ch(2n

‑

1)s'的相位可以比其他第二训练样式信号的相位快。采样时钟信号clk_r1可以是相位被调节使得第二训练样式信号ch1s'、ch(2n

‑

1)s'的转换时间点与采样时间点sp_r1对应的信号。

[0165]

在利用采样时钟信号clk_r1在采样时间点sp_r1进行采样的情况下,信道ch1、ch(2n

‑

1)的先前信号prv_ch1s'、prv_ch(2n

‑

1)s'的第一后标记与当前信号curr_ch1s'、curr_ch(2n

‑

1)s'的主标记之和分别为中间电平il1,与第二基准电压vl1的裕度充分,因此解码为二进制电平1没有问题。

[0166]

但是,信道ch(n

‑

1)、ch(n+1)的先前信号prv_ch(n

‑

1)s'、prv_ch(n+1)s'的第一后标记与当前信号curr_ch(n

‑

1)s'、curr_ch(n+1)s'的主标记之和分别与第二基准电压vl1的裕度不足,从而也可能错误地解码为二进制电平0。并且,信道chn的先前信号prv_chns'的第一后标记与当前信号curr_chns'的主标记之和小于第二基准电压vl1,因此错误地解码为二进制电平0而发生错误。

[0167]

在利用采样时钟信号clk_r2在采样时间点sp_r2进行采样的情况下,信道ch(n

‑

1)、ch(n+1)的先前信号prv_ch(n

‑

1)s'、prv_ch(n+1)s'的第一后标记与当前信号curr_ch(n

‑

1)s'、curr_ch(n+1)s'的主标记之和分别为中间电平il1,与第二基准电压vl1的裕度充分,因此解码为二进制电平1是没有问题的。

[0168]

并且,信道ch1、ch(2n

‑

1)的先前信号prv_ch1s'、prv_ch(2n

‑

1)s'的第一后标记与当前信号curr_ch1s'、curr_ch(2n

‑

1)s'的主标记之和分别为中间电平il1以上,与第二基准电压vl1的裕度更充分,因此第二基准电压vl1和裕度更加充分,从而解码为二进制电平1是没有问题的。

[0169]

但是,感测信道chn的先前信号prv_chns'的第一后标记与当前信号curr_chns'的主标记之和与第二基准电压vl1的裕度r2m不足,因此存在错误地解码为二进制电平0的可能性。

[0170]

在利用采样时钟信号clk_r3在采样时间点sp_r3进行采样的情况下,感测信道chn的先前信号prv_chns'的第一后标记与当前信号curr_chns'的主标记之和为中间电平il1,与第二基准电压vl1的裕度r3m充分,因此解码为二进制电平1是没有问题的。其他信道ch1、ch(n

‑

1)、ch(n+1)、ch(2n

‑

1)具有与第二基准电压vl1更大的裕度,因此解码为二进制电平1是没有问题的。

[0171]

因此,可以确认如下内容:即使利用串扰引起的抖动作用最强的感测信道chn的第二训练样式信号生成采样时钟信号clk_r3,准确地对其他信道ch1、ch(n

‑

1)、ch(n+1)、ch(2n

‑

1)的数据信号进行采样也是没有问题的。

[0172]

图15是用于说明根据本发明的一实施例的时钟数据恢复器的图。

[0173]

参照图15,时钟数据恢复器cdr可以包括转换检测器tdu及相位校正器pcu。

[0174]

转换检测器tdu可以基于训练样式信号及补偿时钟信号comp_clk来提供与训练模式或正常模式对应的模式信号。训练样式信号可以是第一训练样式信号或第二训练样式信号,并且可以通过感测线sl接收。模式信号可以通过模式线ml提供。

[0175]

相位校正器pcu可以基于模式信号及外部时钟信号ext_clk生成补偿时钟信号comp_clk及采样时钟信号中的至少一个。相位校正器pcu可以基于外部时钟信号ext_clk生成第一补偿时钟信号及第二补偿时钟信号。补偿时钟信号comp_clk可以提供至转换检测器tdu,采样时钟信号可以提供至时钟线cl。

[0176]

首先,转换检测器tdu在被输入训练样式信号的情况下提供与训练模式对应的模式信号,相位校正器pcu在被输入与训练模式对应的模式信号的情况下对外部时钟信号

ext_clk的相位进行校正而生成补偿时钟信号comp_clk。

[0177]

接下来,当在训练模式下基于补偿时钟信号comp_clk而检测训练样式信号的转换时间点成功时,转换检测器tdu可以提供与正常模式对应的模式信号。相反,当在训练模式下基于补偿时钟信号comp_clk而检测训练样式信号的转换时间点失败时,转换检测器tdu可以持续提供与训练模式对应的模式信号。

[0178]

此时,在训练模式被保持的情况下,相位校正器pcu可以对外部时钟信号ext_clk的相位进行再次校正,从而再次生成补偿时钟信号comp_clk。并且,当训练模式结束且正常模式开始时,相位校正器pcu可以生成具有与当前的补偿时钟信号comp_clk相同的相位的采样时钟信号。

[0179]

图16是用于说明根据本发明的一实施例的转换检测器的图。

[0180]

参照图16,根据本发明一实施例的转换检测器f_tdu可以包括积分器int1、int2、比较器cp1、cp2、第一与非门nand1、第一反相器inv1及第一模式信号保持部misu1。

[0181]

转换检测器f_tdu可以接收作为上述补偿时钟信号comp_clk的第一补偿时钟信号cck1及第二补偿时钟信号cck2。第二补偿时钟信号cck2的相位可以比第一补偿时钟信号cck1的相位延迟。

[0182]

并且,转换检测器f_tdu可以通过感测线sl接收第一训练样式信号。

[0183]

第一积分器int1可以根据第一补偿时钟信号cck1对第一训练样式信号进行积分而提供第一积分信号。例如,在第一补偿时钟信号cck1为高电平的时段期间,第一积分器int1可以对第一训练样式信号进行积分而提供第一积分信号。

[0184]

第二积分器int2可以根据第二补偿时钟信号cck2对第一训练样式信号进行积分而提供第二积分信号。例如,在第二补偿时钟信号cck2为高电平的时段期间,第二积分器int2可对第一训练样式信号进行积分而提供第二积分信号。

[0185]

根据实施例,积分器int1、int2可以通过模式线ml接收第一模式信号,并且可以在训练模式的第一模式信号下操作,并且在正常模式的第一模式信号下停止操作。

[0186]

第一比较器cp1可以在第一积分信号大于第一基准电压vh2的情况下输出逻辑值1,而在第一积分信号小于第一基准电压vh2的情况下输出逻辑值0。例如,第一比较器cp1可以在第一补偿时钟信号cck1的反相信号cck1b为高电平时操作而将第一积分信号与第一基准电压vh2进行比较。

[0187]

第二比较器cp2可以在第二积分信号大于第一基准电压vh2的情况下输出逻辑值1,而在第二积分信号小于第一基准电压vh2的情况下输出逻辑值0。例如,第二比较器cp2可以在第二补偿时钟信号cck2的反相信号cck2b为高电平时操作而将第二积分信号与第一基准电压vh2进行比较。

[0188]

根据实施例,第一比较器cp1及第二比较器cp2中的每一个可以在后端包括锁存器(latch),并且在一定时段期间保持各个输出值。

[0189]

第一反相器inv1可以接收第二比较器cp2的输出值。第一反相器inv1可以输出将第二比较器cp2的输出值反相的逻辑值。

[0190]

第一与非门nand1可以基于第一比较器cp1及第一反相器inv1的输出值而输出第一检测信号。例如,第一与非门nand1可以仅当第一比较器cp1及第一反相器inv1的输出值均为逻辑值1时输出逻辑值0作为第一检测信号,而在其他情况下输出逻辑值1作为第一检

测信号。第一检测信号可以施加到第一检测节点dn1。

[0191]

第一模式信号保持部misu1可以对应于导通电平的初始化信号而提供训练模式的第一模式信号。第一模式信号保持部misu1可以通过初始化线rsl接收初始化信号,并且通过模式线ml提供第一模式信号。

[0192]

根据实施例,第一模式信号保持部misu1可以对应于在接收导通电平的初始化信号之后的第一个导通电平的第一检测信号而提供正常模式的第一模式信号,之后与第一检测信号的电平变化无关地保持正常模式的第一模式信号。

[0193]

即,若第一模式信号保持部misu1基于第一检测信号开始提供正常模式的第一模式信号,则之后可以与第一检测信号的电平变动无关地持续提供正常模式的第一模式信号。在本实施例中,为了使第一模式信号保持部misu1提供训练模式的第一模式信号,需要通过初始化线rsl接收导通电平的初始化信号。

[0194]

在此,“导通电平”表示可以使施加有该相应信号的晶体管导通的信号的电平。例如,由于第一检测信号施加于栅极电极的第一晶体管t1是p型晶体管(例如,pmos),因此第一检测信号的导通电平可以是低电平。并且,由于初始化信号施加于栅极电极的第三晶体管t3

‑

1、t3

‑

2是n型晶体管(例如,nmos),因此初始化信号的导通电平可以是高电平。

[0195]

根据实施例,第一模式信号保持部misu1可以包括晶体管t1、t2、t3

‑

1、t3

‑

2以及反相器inv2、inv3、inv4。

[0196]

对于第一晶体管t1而言,栅极电极可以接收第一检测信号,一电极连接到第一电源vdd,另一电极连接到第一感测节点sn1。第一晶体管t1可以是p型晶体管。第一晶体管t1的栅极电极可以连接到第一检测节点dn1。

[0197]

对于第二晶体管t2而言,栅极电极可以与第二反相器inv2的输出端连接,一电极连接到第一电源vdd,另一电极连接到第一感测节点sn1。第二晶体管t2可以是p型晶体管。

[0198]

对于第三晶体管t3

‑

1、t3

‑

2而言,栅极电极可以接收初始化信号,一电极连接到第一感测节点sn1,另一电极连接到第二电源vss。第三晶体管t3

‑

1、t3

‑

2可以是n型晶体管。第三晶体管t3

‑

1、t3

‑

2的栅极电极可以连接到初始化线rsl。如图16所示,第三晶体管t3

‑

1、t3

‑

2可以包括两个子晶体管t3

‑

1、t3

‑

2。第二电源vss的电压电平可以比第一电源vdd的电压电平低。

[0199]

对于第二反相器inv2而言,输入端可以连接到第一感测节点sn1,输出端连接到第二晶体管t2的栅极电极。

[0200]

第三反相器inv3的输入端可以连接到第一感测节点sn1。

[0201]

对于第四反相器inv4而言,输入端可以与第三反相器inv3的输出端连接,并且输出第一模式信号。例如,第四反相器inv4的输出端可以与模式线ml连接。

[0202]

图17是用于说明可用于图16的转换检测器的示例性的第一训练样式信号的图。

[0203]

图17的虚线波形表示通过理想信道情况下的第一训练样式信号f_trp的波形,图17的实线波形表示通过实际信道情况下的第一训练样式信号f_trp的波形。

[0204]

第一训练样式信号f_trp的1周期(1period)可以为(j+k)

‑

ui,并且j

‑

ui期间的二进制电平与k

‑

ui期间的二进制电平可以彼此不同。此时,j及k可以是大于0的整数。

[0205]

根据一实施例,k可以为1。例如,第一训练样式信号f_trp可以在1周期中的1ui期间包括下降脉冲,并且在1周期中的剩余ui期间保持高电平。

[0206]

在这种情况下,由于在j

‑

ui期间不发生转换且电压被充电至信道,因此在短的k

‑

ui期间可能不能充分地发生第一转换(下降转换)。即,图17的第一训练样式信号f_trp可能是下降转换时的符号间干扰问题中最坏的情况。

[0207]

因此,在同时向所有信道发送作为最坏的情况的第一训练样式信号f_trp(偶数模式),并且以可以在感测信道检测第一转换的方式确定采样时钟信号的相位的情况下,可以获得对串扰引起的抖动及符号间干扰两者具有鲁棒性的采样时钟信号的相位。

[0208]

根据本实施例,由于不需要在发送单元tx1~tx(2n

‑

1)应用预加强(pre

‑

emphasis)技术,因此可以节约构成成本。

[0209]

图18至图20是用于说明基于第一训练样式信号的图16的转换检测器的操作的图。

[0210]

具体而言,图18是用于说明图17的时段t1f~t2f中转换检测器f_tdu的操作的图,图19及图20是用于说明图17的时段t2f~t3f中转换检测器f_tdu的操作的图。

[0211]

第一基准电压vh2可以具有积分信号int1s、int2s的可变电平中的最高电平hl2与中间电平il2之间的中间值。第二基准电压vl2可以具有积分信号int1s、int2s的可变电平中的最低电平ll2与中间电平il2之间的中间值。电压hl2、vh2、il2、vl2、ll2可以与参考图2及图3所述的电压hl1、vh1、il1、vl1、ll1相同,也可以不同。

[0212]

当第一积分信号int1s大于第一基准电压vh2且第二积分信号int2s小于第一基准电压vh2时,转换检测器f_tdu可以检测第一训练样式信号f_trp的转换的发生。

[0213]

例如,第一积分器int1可以在第一补偿时钟信号cck1为高电平的时段期间对第一训练样式信号f_trp进行积分而生成第一积分信号int1s。并且,第二积分器int2可以在第二补偿时钟信号cck2为高电平的时段期间对第一训练样式信号f_trp进行积分而生成第二积分信号int2s。

[0214]

根据实施例,当对应的补偿时钟信号cck1、cck2为低电平时,积分器int1、int2可以被初始化,从而输出值被初始化为中间电平il2。

[0215]

对于图18的情况而言,在不发生转换的时段t1f~t2f中,第一积分信号int1s及第二积分信号int2s的大小可以彼此相同。

[0216]

在图18的情况下,第一积分信号int1s及第二积分信号int2s大于第一基准电压vh2,因此第一比较器cp1及第二比较器cp2全部输出逻辑值1。据此,第一反相器inv1输出逻辑值0,第一与非门nand1输出逻辑值1。第一检测信号具有逻辑值1,并且第一晶体管t1保持截止状态。因此,在图18的情况下,可以持续输出训练模式的第一模式信号,并且通过相位校正器pcu而变更调整第一补偿时钟信号cck1及第二补偿时钟信号cck2的相位。

[0217]

对于图19及图20的情况而言,在发生转换的时段t2f~t3f中,第一积分信号int1s及第二积分信号int2s的大小可以彼此不同。例如,第二积分信号int2s可以小于第一积分信号int1s。

[0218]

尽管如此,在图19的情况下,由于第一积分信号int1s及第二积分信号int2s大于第一基准电压vh2,因此第一检测信号具有逻辑值1。因此,在图19的情况下,可以持续输出训练模式的第一模式信号,并且通过相位校正器pcu而变更调整第一补偿时钟信号cck1及第二补偿时钟信号cck2的相位。

[0219]

在图20的情况下,第一积分信号int1s大于第一基准电压vh2,第二积分信号int2s小于第一基准电压vh2。因此,第一比较器cp1输出逻辑值1,第二比较器cp2输出逻辑值0。因

此,第一反相器inv1输出逻辑值1,第一与非门nand1输出逻辑值0。第一检测信号具有逻辑值0,并且第一晶体管t1导通。

[0220]

因此,第一电源vdd的电压被充电到第一感测节点sn1,逻辑值1通过第三反相器inv3和第四反相器inv4作为第一模式信号而输出。第一模式信号的逻辑值1可以表示正常模式,逻辑值0表示训练模式。因此,相位校正器pcu可以生成与第二补偿时钟信号cck2具有相同相位的采样时钟信号。

[0221]

之后,即使第一检测信号的逻辑值变动而第一晶体管t1导通或截止,第二晶体管t2也通过第二反相器inv2保持导通状态,因此第一感测节点sn1的电压被保持。据此,与第一检测信号的逻辑值的变动无关,正常模式的第一模式信号持续输出。

[0222]

图21是用于说明根据本发明的另一实施例的转换检测器的图。

[0223]

参照图21,根据本发明一实施例的转换检测器r_tdu可以包括积分器int3、int4、比较器cp3、cp4、第五反相器inv5、第二与非门nand2及第二模式信号保持部misu2。

[0224]

转换检测器r_tdu可以接收作为上述的补偿时钟信号comp_clk的第三补偿时钟信号cck3及第四补偿时钟信号cck4。第四补偿时钟信号cck4的相位可以比第三补偿时钟信号cck3的相位延迟。

[0225]

并且,转换检测器r_tdu可以通过感测线sl接收第二训练样式信号。

[0226]

第三积分器int3可以根据第三补偿时钟信号cck3对第二训练样式信号进行积分而提供第三积分信号。例如,在第三补偿时钟信号cck3为高电平的时段期间,第三积分器int3可以对第二训练样式信号进行积分而提供第三积分信号。

[0227]

第四积分器int4可以根据第四补偿时钟信号cck4对第二训练样式信号进行积分而提供第四积分信号。例如,在第四补偿时钟信号cck4为高电平的时段期间,第四积分器int4可通过对第二训练样式信号进行积分而提供第四积分信号。

[0228]

根据实施例,积分器int3、int4可以通过模式线ml接收第二模式信号,并且可以在训练模式的第二模式信号下操作,并且在正常模式的第二模式信号下停止操作。

[0229]

第三比较器cp3可以在第三积分信号大于第二基准电压vl2的情况下输出逻辑值1,而在第三积分信号小于第二基准电压vl2的情况下输出逻辑值0。例如,第三比较器cp3可以在第三补偿时钟信号cck3的反相信号cck3b为高电平时操作而将第三积分信号与第二基准电压vl2进行比较。

[0230]

第四比较器cp4可以在第四积分信号大于第二基准电压vl2的情况下输出逻辑值1,而在第四积分信号小于第二基准电压vl2的情况下输出逻辑值0。例如,第四比较器cp4可以在第四补偿时钟信号cck4的反相信号cck4b为高电平时操作而对第四积分信号与第二基准电压vl2进行比较。

[0231]

根据实施例,第三比较器cp3及第四比较器cp4中的每一个可以在后端包括锁存器,并且在一定时段期间保持各个输出值。

[0232]

第五反相器inv5可以接收第三比较器cp3的输出值。第五反相器inv5可以输出将第三比较器cp3的输出值反相的逻辑值。

[0233]

第二与非门nand2可以基于第五反相器inv5及第四比较器cp4的输出值而输出第二检测信号。例如,第二与非门nand2可以仅当第五反相器inv5及第四比较器cp4的输出值均为逻辑值1时输出逻辑值0作为第二检测信号,而在其他情况下输出逻辑值1作为第二检

测信号。第二检测信号可以施加到第二检测节点dn2。

[0234]

第二模式信号保持部misu2可以对应于导通电平的初始化信号而提供训练模式的第二模式信号。第二模式信号保持部misu2可以通过初始化线rsl接收初始化信号,并且通过模式线ml提供第二模式信号。

[0235]

根据实施例,第二模式信号保持部misu2可以对应于在接收导通电平的初始化信号之后的第一个导通电平的第二检测信号而提供正常模式的第二模式信号,之后与第二检测信号的电平变化无关地保持正常模式的第二模式信号。

[0236]

即,若第二模式信号保持部misu2基于第二检测信号开始提供正常模式的第二模式信号,则之后可以与第二检测信号的电平变动无关地持续提供正常模式的第二模式信号。在本实施例中,为了使第二模式信号保持部misu2提供训练模式的第二模式信号,需要通过初始化线rsl接收导通电平的初始化信号。

[0237]

根据实施例,第二模式信号保持部misu2可以包括晶体管t4、t5、t6

‑

1、t6

‑

2以及反相器inv6、inv7、inv8。

[0238]

对于第四晶体管t4而言,栅极电极可以接收第二检测信号,一电极连接到第一电源vdd,另一电极连接到第二感测节点sn2。第四晶体管t4可以是p型晶体管。第四晶体管t4的栅极电极可以连接到第二检测节点dn2。

[0239]

对于第五晶体管t5而言,栅极电极可以与第六反相器inv6的输出端连接,一电极连接到第一电源vdd,另一电极连接到第二感测节点sn2。第五晶体管t5可以是p型晶体管。

[0240]

对于第六晶体管t6

‑

1、t6

‑

2而言,栅极电极可以接收初始化信号,一电极连接到第二感测节点sn2,另一电极连接到第二电源vss。第六晶体管t6

‑

1、t6

‑

2可以是n型晶体管。第六晶体管t6

‑

1、t6

‑

2的栅极电极可以连接到初始化线rsl。如图21所示,第六晶体管t6

‑

1、t6

‑

2可以包括两个子晶体管t6

‑

1、t6

‑

2。

[0241]

第六反相器inv6的输入端可以连接到第二感测节点sn2,输出端连接到第五晶体管t5的栅极电极。

[0242]

第七反相器inv7的输入端可以连接到第二感测节点sn2。

[0243]

对于第八反相器inv8而言,输入端可以与第七反相器inv7的输出端连接,并且输出第二模式信号。例如,第八反相器inv8的输出端可以与模式线ml连接。

[0244]

图22是用于说明可用于图21的转换检测器的示例性的第二训练样式信号的图。

[0245]

图22的虚线波形表示通过理想信道情况下的第二训练样式信号r_trp的波形,图22的实线波形表示通过实际信道情况下的第二训练样式信号r_trp的波形。

[0246]

第二训练样式信号r_trp的1周期可以为(j+k)

‑

ui,并且j

‑

ui期间的二进制电平与k

‑

ui期间的二进制电平可以彼此不同。此时,j及k可以是大于0的整数。

[0247]

根据一实施例,k可以为1。例如,第二训练样式信号r_trp可以在1周期中的1ui期间包括上升脉冲,并且在1周期中的剩余ui期间保持低电平。

[0248]

在这种情况下,由于在j

‑

ui期间不发生转换且电压被充电至信道,因此在短的k

‑

ui期间可能不能充分地发生第二转换(上升转换)。即,图22的第二训练样式信号r_trp可能是上升转换时的符号间干扰问题中最坏的情况。

[0249]

因此,在同时向所有信道发送作为最坏的情况的第二训练样式信号r_trp(偶数模式),并且以可以在感测信道检测第二转换的方式确定采样时钟信号的相位的情况下,可以

获得对串扰引起的抖动及符号间干扰两者具有鲁棒性的采样时钟信号的相位。

[0250]

根据本实施例,由于不需要在发送单元tx1~tx(2n

‑

1)应用预加强技术,因此可以节约构成成本。

[0251]

对于图21的转换检测器r_tdu而言,当第三积分信号小于第二基准电压vl2且第四积分信号大于第二基准电压vl2时,可以检测第二训练样式信号r_trp的转换的发生。转换检测器r_tdu的详细操作与图16的转换检测器f_tdu的详细操作相似,因此将省略重复说明。作为参考,由于第一训练样式信号f_trp相对较长地保持高电平,因此转换检测器f_tdu可以以第一基准电压vh2为基准进行操作,而由于第二训练样式信号r_trp相对较长地保持低电平,因此转换检测器r_tdu可以以第二基准电压vl2为基准进行操作。

[0252]

根据以上所述,图15的转换检测器tdu可以被构成为图16的转换检测器f_tdu及图22的转换检测器r_tdu中的一个。

[0253]

例如,在转换检测器tdu仅包括图16的转换检测器f_tdu的情况下,时钟数据恢复器dr可以提供具有当检测到转换时的相位的第二补偿时钟信号cck2作为采样时钟信号。例如,在转换检测器tdu仅包括图22的转换检测器r_tdu的情况下,时钟数据恢复器cdr可以提供具有当检测到转换时的相位的第四补偿时钟信号cck4作为采样时钟信号。

[0254]

根据另一实施例,图15的转换检测器tdu可以包括全部的转换检测器f_tdu、r_tdu。

[0255]

例如,时钟数据恢复器cdr可以将训练模式的第一模式信号发送到模式线ml。发送单元tx1~tx(2n

‑

1)在接收到训练模式的第一模式信号的情况下可以发送第一训练样式信号f_trp。

[0256]

因此,时钟数据恢复器cdr可以使转换检测器f_tdu操作,并且向模式线ml输出正常模式的第一模式信号。此时,时钟数据恢复器cdr可以将第二补偿时钟信号cck2的相位存储为第一相位。

[0257]

接着,时钟数据恢复器cdr可以将训练模式的第二模式信号发送至模式线ml。发送单元tx1~tx(2n

‑

1)在接收到训练模式的第二模式信号的情况下可以发送第二训练样式信号r_trp。

[0258]

因此,时钟数据恢复器cdr可以使转换检测器r_tdu操作,并且向模式线ml输出正常模式的第二模式信号。此时,时钟数据恢复器cdr可以将第四补偿时钟信号cck4的相位存储为第二相位。

[0259]

时钟数据恢复器cdr可以提供具有第一相位及第二相位中的更延迟的相位的补偿时钟信号作为采样时钟信号。例如,在第一相位比第二相位延迟的情况下,提供第二补偿时钟信号cck2作为采样时钟信号,而在第二相位比第一相位延迟的情况下,提供第四补偿时钟信号cck4作为采样时钟信号。选择更延迟的相位的原因可以参照关于图12及图14的说明。根据本实施例,可以获得对下降转换及上升转换全部具有鲁棒性的采样时钟信号的相位。

[0260]

目前为止参照的附图和记载的发明的详细说明对于本发明仅为示例性的,这仅出于对本发明进行说明的目的而使用,并非为了限定含义或限制权利要求书中所记载的本发明的范围而使用。因此,只要是在本技术领域中具有普通知识水平的人便可以理解,可以对其进行多种变形且能够实现为等同的其他实施例。因此,本发明的真正的技术保护范围应

当根据记载的权利要求书的技术思想而被确定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1