一种逐次逼近型ADC的电容阵列和开关逻辑电路

本发明涉及逐次逼近型adc技术领域,具体而言涉及一种逐次逼近型adc的电容阵列和开关逻辑电路。

背景技术:

现代高速通信系统,比如超带宽无线电、高速串行链路以及以太网收发器等,需要用到中等分辨率以及数百兆采样率的模数转换器,常用的高速adc类型主要有全并行型(flash)adc、流水线型(pipeline)adc和逐次逼近型(sar)adc。2b/cyclesaradc是一种结合flashadc的思想,在传统1b/cyc1esaradc结构中引入多个比较器,一次并行比较出多比特的结构,因此,与1b/cycle的方式相比,它可以通过更少的比较次数来达到相同的分辨率,主要优势是提升逐次逼近型adc的速度。

但是由于传统2b/cyc1esaradc由多个dac组成,并且需要预充电的操作来产生不同的阈值电压从而完成每次比较,这会带来额外的时间与功耗上的开销,这种开销不仅会降低转换的效率和速度,而且由于额外的相位和逻辑操作会使这种架构对温度和电压因素变化更为敏感。尤其是当adc的位数更高时,需要占用的时长和功耗会更多。

技术实现要素:

本发明针对现有技术中的不足,提供一种逐次逼近型adc的电容阵列和开关逻辑电路,能够消除传统2b/cyc1e结构甚至更高位结构中,为了产生不同阈值而需要在每次比较器工作前插入一段时间作为预充电相的问题,同时可以实现简易的开关控制逻辑。

为实现上述目的,本发明采用以下技术方案:

一种逐次逼近型adc的电容阵列和开关逻辑电路,所述电容阵列和开关逻辑电路包括两组dac阵列、三个比较器和sar逻辑电路;

所述dac阵列包括2n+1个单位电容,其正负差分输入端各设置有2n个单位电容,n为adc的位数;每一步量化过程控制对应其中4个单位电容,且每一步量化过程控制对应的单位电容不重复,第j步量化对应控制的电容权重为

所述dac阵列采用下极板采样方式,每一步量化开始前将电容的下极板与输入信号连接进行采样,同时电容上极板连接比较器输入端并短接到共模电压vcm;在采样完成时断开上极板与共模电压vcm的连接,并且断开下极板与输入信号的连接,将下极板连接到预设的固定电压上,在实现将下极板电荷转移到上极板的同时产生第一步量化比较所需的阈值复位操作,使比较器开始工作,以进行第一步的2位数据量化;

所述sar逻辑电路的输入端与比较器的输出端连接,sar逻辑电路的输出端与dac阵列的下极板开关栅极连接,使dac阵列的之后每一步量化,由sar逻辑输出信号控制这一步的电容下极板电压,以产生下一步量化所需的新的阈值。

为优化上述技术方案,采取的具体措施还包括:

进一步地,设采样之后的复位相将电容阵列的下极板复位到预设的固定参考电平vrefp和vrefn;

所述三个比较器分别为第一比较器、第二比较器和第三比较器;第一比较器同相端各步电容的下极板分别连接到vrefp、vrefp、vrefn、vrefp,其反相端各步电容的下极板分别连接到vrefn、vrefn、vrefp、vrefn;第三比较器同相端各步电容的下极板分别连接到vrefn、vrefn、vrefp、vrefn,其反相端各步电容的下极板分别连接到vrefp、vrefp、vrefn、vrefp;第二比较器同相端与第一比较器同相端连接,其反相端与第三比较器反相端连接;其中,vref=vrefp-vrefn,以使第一比较器、第二比较器和第三比较器等效的阈值分别为-1/2×vref、0和1/2×vref;

所述sar逻辑电路根据三个比较器的结果判断vip-vin落在以上三个阈值间的位置,获得第一步的2-bit数据;

低4位的电容在采样时相接vin,复位相时按照3∶1的数量比例接vrefp或者vrefn,以构建2的整数次幂的总电容以及形成相应的比较器阈值电压。

进一步地,比较器两端dac中最低位的四个电容中的其中三个接vrefp,另一个接vrefn。

进一步地,最低位电容的其中两个差分电容接相同的vrefp或者vrefn,另外两个接共模电压。

进一步地,所述sar逻辑电路的输出量化结果连接到dac阵列的下极板开关栅极上,第一比较器和第三比较器的同相端电容阵列下极板电平受输出量化结果的d<i>控制,反相端电容阵列下极板电平受输出量化结果

进一步地,所述电容阵列和开关逻辑电路包括2m-1个比较器,高位电容分拆比例为(2m-1)∶1;m为大于等于2的正整数。

本发明的有益效果是:

本发明提供了一种面向2b/cycle的逐次逼近型(successive-approximation-register,sar)模数转换器(analog-to-digitalconverter,adc)的电容阵列和开关逻辑电路。电路通过两组数模转换器(digital-to-analog,dac)阵列和三个比较器在每一步量化时分别产生三个不同的阈值,以此实现每步输出2位数据的功能,为此,本发明设计了专用的电容排布方式,以消除传统2b/cycle结构甚至更高位结构中,为了产生不同阈值而需要在每次比较器工作前插入一段时间作为预充电相的问题。同时本发明还实现了极为简单的开关控制逻辑方案,电容阵列的切换由电路后端部分sar逻辑电路的输出,即每一步的量化结果d<i>或其经反相器后的

附图说明

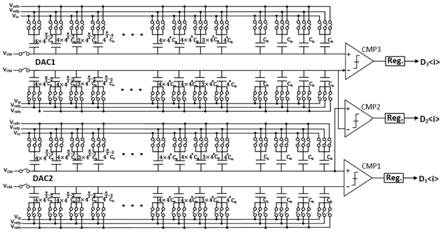

图1为逐次逼近型adc的电容阵列和开关逻辑电路示意图。

图2为电容阵列的复位相示意图。

图3为电容阵列的转换相示意图。

图4为面向2b/cycle8-bitsaradc的电容阵列示意图。

图5为2b/cycle8-bitsaradc的量化示意图。

图6为2b/cycle8-bitsaradc的工作时序示意图。

具体实施方式

现在结合附图对本发明作进一步详细的说明。

需要注意的是,发明中所引用的如“上”、“下”、“左”、“右”、“前”、“后”等的用语,亦仅为便于叙述的明了,而非用以限定本发明可实施的范围,其相对关系的改变或调整,在无实质变更技术内容下,当亦视为本发明可实施的范畴。

结合图1,本发明提及一种逐次逼近型adc的电容阵列和开关逻辑电路,所述电容阵列和开关逻辑电路包括两组dac阵列、三个比较器和sar逻辑电路。

所述dac阵列包括2n+1个单位电容,其正负差分输入端各设置有2n个单位电容,n为adc的位数;每一步量化过程控制对应其中4个单位电容,且每一步量化过程控制对应的单位电容不重复,第j步量化对应控制的电容权重为

所述dac阵列采用下极板采样方式,每一步量化开始前将电容的下极板与输入信号连接进行采样,同时电容上极板连接比较器输入端并短接到共模电压vcm;在采样完成时断开上极板与共模电压vcm的连接,并且断开下极板与输入信号的连接,将下极板连接到预设的固定电压上,在实现将下极板电荷转移到上极板的同时产生第一步量化比较所需的阈值复位操作,使比较器开始工作,以进行第一步的2位数据量化。

所述sar逻辑电路的输入端与比较器的输出端连接,sar逻辑电路的输出端与dac阵列的下极板开关栅极连接,使dac阵列的之后每一步量化,由sar逻辑输出信号控制这一步的电容下极板电压,以产生下一步量化所需的新的阈值。

对于一个n位的adc,其正负差分输入端各需要2n个单位电容,adc总共需要2n+1个单位电容,采用2b/cycle的方案需要

当第一步的量化结束后,关断复位信号对于该步四个电容的控制,转由sar逻辑输出量化信号控制该步的电容来产生新的阈值。

如上所述的一种面向2b/cycle的逐次逼近型adc的电容阵列,每一步量化都不再需要额外的预充电操作,只需要进行与传统saradc相似的操作,即由sar逻辑输出控制dac切换进行下一步操作即可实现所需的新的阈值的产生,省下了大量预充电的时间以及功耗。采样之后的复位相将电容阵列的下极板复位到预设的固定电平vrefp和vrefn,其中,将cmp1同相端各步电容的下极板分别连接到vrefp、vrefp、vrefn、vrefp,而其反相端各步电容的下极板分别连接到vrefn、vrefn、vrefp、vrefn,同时,将cmp3同相端各步电容的下极板分别连接到vrefn、vrefn、vrefp、vrefn,而其反相端各步电容的下极板分别连接到vrefp、vrefp、vrefn、vrefp。

其中,由于4∶4∶3∶1的权重分布,并假设vref=vrefp-vrefn,在第一步的比较开始时cmp1同相端的电压值为

当第一步输出量化结果后,关断复位信号对于该步四个电容的控制,转由sar逻辑输出信号控制该步的电容下极板电压,产生新的阈值。其中sar逻辑的输出量化结果连接到dac电容阵列的下极板开关栅极上,cmp1和cmp3的同相端电容阵列下极板电平受输出量化结果的d<i>控制,反相端电容阵列下极板电平受输出量化结果

图1为本实施例中专用的n-bit电容阵列示意图,此电路由两组dac阵列dac1、dac2和三个比较器cmp3、cmp2、cmp1组成,这三个比较器可以分别生成d3<i>、d2<i>、d1<i>三位量化结果,量化结果被用来控制电容下极板开关的栅极。n-bitsaradc一共需要

如图4所示,这个8-bit电容阵列的下极板已经被连接到了预设的固定电压上。用1来表示参考电平vrefp,用0表示vrefn,则cmp3同相端每一步电容接入的预设固定电压为0、0、1、0,其反相端各步电容接入的预设固定电压为1、1、0、1,同理cmp1的预设固定电压接法已经在图4中体现。由于电容4∶4∶3∶1的权重分布,并假设vref=vrefp-vrefn,则在第一步比较开始时cmp3同相端的电压值为vcm-vin+64/256×vrefp+192/256×vrefn,反相端的电压值为vcm-vip+192/256×vrefp+64/256×vrefn,因此cmp3比较的值为vip-vin-1/2×vref是否大于0,等效的阈值为1/2×vref,同样的cmp2和cmp1等效的阈值为0和-1/2vref,根据cmp3、cmp2、cmp1分别产生的1/2×vref、0、-1/2×vref这三个等效阈值,判定vip-vin落在以上三个阈值间的位置,获得量化输出结果,并用d3<i>d2<i>d1<i>来表示。一共会产生四种量化结果,即:111、011、001、000,其中011表示vip-vin落在了0到1/2×vref的区间内,其他几个量化结果同理,从而获得第一步的2-bit数据。

图5是本实施例的一个具体量化过程,假设采样到的输入信号是+201/256×vref,首先电路整体会被复位来获取第一步比较所需要的阈值,根据上述第一步量化前产生的三个阈值-1/2×vref、0、1/2×vref,可见输入信号落在1/2×vref到vref之间,并通过电路后端部分sar逻辑电路得到的输出量化结果为1、1、1,分别记为d3<1>、d2<1>、d1<1>,利用该量化结果来控制图4中电容阵列的第一步四个电容,将此量化结果di<1>(i=1、2、3)或其经过一个反相器后的

通过以上具体的量化过程描述可见,4∶4∶3∶1的电容权重分布能够产生我们所需要的三个阈值电压。预设的固定电压1101和0010实现了阈值电压的可增可减性,比如,当图4中的cmp1同相端的电容下极板接入1101的固定电压时,其电容上极板电平为vcm-vin+192/256×vrefp+64/256×vrefn,若下极板改接入1111的电平,上极板的电平就会变为vcm-vin+240/256×vrefp+16/256×vrefp,即上极板增加了48/256×vref的电平。反之,在cmp1同相端电容下极板接入0000的电平时,上极板的电平就变为vcm-vin+48/256×vrefp+208/256×vrefp,即上极板减少了144/256×vref的电平,固定电压的这些增减变化刚好可以满足每步比较所需要的阈值电压。

上述采样、阈值生成、转换的过程,在图6的工作时序下进行,当cks是高电平时,信号输入到电容阵列的下极板,电路开始采样,然后经过一定的时间等待电荷转移到上极板,接着开始第一位比较前的复位操作,复位的过程是对图1中dac阵列的整体进行充电,即图6中clk_charge的s1、s2、s3、s4高电平阶段,当复位结束之后,开始第一位的比较,比较结束之后通过一个逻辑电路来控制s1复位信号的关断,并利用输出量化结果来控制电路产生新的阈值,再依次得到比较输出结果,并依次关断当前比较完成所对应的复位信号。

以上仅是本发明的优选实施方式,本发明的保护范围并不仅局限于上述实施例,凡属于本发明思路下的技术方案均属于本发明的保护范围。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理前提下的若干改进和润饰,应视为本发明的保护范围。

- 还没有人留言评论。精彩留言会获得点赞!