压控振荡器和锁相环的制作方法

1.本发明实施例涉及半导体制造领域,尤其涉及一种压控振荡器和锁相环。

背景技术:

2.振荡器是指在没有外部信号激励下,自身就能够将直流电能转换成周期性交流信号的电路。若振荡器的工作状态、振荡回路的元件参数受输入控制电压的控制,则该振荡器就构成一个压控振荡器。

3.压控振荡器(voltage controlled oscillator,vco),是一个由输入控制电压控制的、其振荡频率可调的振荡器,其振荡频率是输入控制电压的函数,压控振荡器是锁相环电路的核心部分。压控振荡器被广泛地应用于微处理器中的时钟同步(clock synchronization)电路、无线通信收发器中的频率综合器(frequency synthesizer)、光纤通信中的时钟恢复电路(clock recovery circuit,crc)以及多相位采样(multi-phase sampling)电路中。

4.其中,压控振荡器的主要性能指标为相位噪声(phase noise,pn)。

技术实现要素:

5.本发明实施例解决的问题是提供一种压控振荡器和锁相环,改善压控振荡器的相位噪声。

6.为解决上述问题,本发明实施例提供一种压控振荡器,包括:谐振电路,所述谐振电路具有第一输出端和第二输出端;电流源;负阻电路,包括第一晶体管和第二晶体管,所述第一晶体管和第二晶体管均为nmos晶体管,所述nmos晶体管的衬底中具有p型阱区、以及包围所述p型阱区的n型阱区,所述p型阱区具有体端,所述第一晶体管的漏极和第二晶体管的栅极共接于所述第一输出端,所述第一晶体管的栅极和第二晶体管的漏极共接于所述第二输出端,所述第一晶体管的体端和源极相连并共接于所述电流源,所述第二晶体管的体端和源极相连并共接于所述电流源。

7.可选的,所述n型阱区浮接。

8.可选的,所述n型阱区包括:位于所述p型阱区底部的第一n型阱区,所述p型阱区在所述第一n型阱区中的投影位于所述第一n型阱区内部,且所述第一n型阱区为深n型阱区;环绕所述p型阱区的第二n型阱区,所述第二n型阱区与相对应的所述第一n型阱区相连,所述第二n型阱区的离子掺杂浓度小于所述第一n型阱区的离子掺杂浓度。

9.可选的,所述衬底表面露出的n型阱区中具有n型接触区,所述n型接触区用于作为相对应的所述n型阱区的外接端子。

10.可选的,所述nmos晶体管的p型阱区中还具有与所述源极相隔离的第一p型接触区,所述第一p型接触区用于作为相对应的所述p型阱区的体端。

11.可选的,所述nmos晶体管的衬底为p型衬底。

12.可选的,所述nmos晶体管的衬底中均具有与所述n型阱区相隔离的第二p型接触

区,所述第二p型接触区用于作为相对应的所述衬底的外接端子。

13.可选的,所述p型衬底接地。

14.可选的,所述谐振电路包括并联连接的电感和电容;所述电感的两端分别与所述第一输出端和第二输出端耦接;所述电容的两端分别与所述第一输出端和第二输出端耦接。

15.可选的,所述电容包括可变电容和电容矩阵中的一种或两种。

16.相应的,本发明实施例还提供一种锁相环,包括本发明实施例提供的压控振荡器。

17.与现有技术相比,本发明实施例的技术方案具有以下优点:

18.本发明实施例提供的压控振荡器中,负阻电路包括第一晶体管和第二晶体管,第一晶体管和第二晶体管均为nmos晶体管,所述nmos晶体管的衬底中具有p型阱区、以及包围所述p型阱区的n型阱区,p型阱区具有体(bulk)端,所述第一晶体管的体端和源极相连并共接于所述电流源,所述第二晶体管的体端和源极相连并共接于所述电流源;其中,通过在nmos晶体管的衬底中设置n型阱区,以隔离nmos晶体管的p型阱区和衬底,也就是说,隔离了nmos晶体管的体衬底(也即p型阱区)和外部衬底,从而能够在衬底(也即外部衬底)的电位连接方式不受影响的情况下,使得nmos晶体管的体端和源极能够相连,体端和源极的电位差(即vbs)为零,相应能够改善或消除nmos晶体管的衬偏效应,同时,通过n型阱区来隔离p型阱区和衬底,有利于隔绝外界衬底噪声的影响,上述两个方面均有利于改善压控振荡器的相位噪声。

附图说明

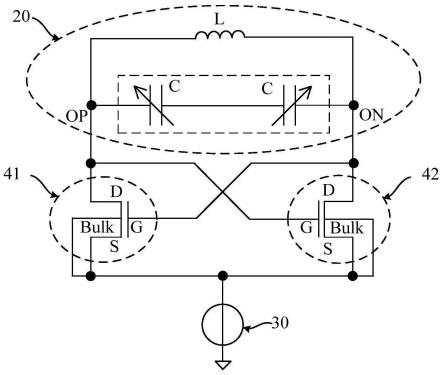

19.图1是一种压控振荡器的电路结构示意图;

20.图2是一种半导体结构的结构示意图;

21.图3是本发明压控振荡器一实施例的电路结构示意图;

22.图4是图3所示负阻电路中nmos晶体管一实施例的结构示意图;

23.图5是图3所示负阻电路中nmos晶体管在n型阱区浮接的情况下所对应的等效电路图。

具体实施方式

24.目前,压控振荡器的相位噪声仍有待改善。以下结合一种压控振荡器,分析相位噪声仍有待改善的原因。

25.图1是一种压控振荡器的电路结构示意图。

26.传统的电容电感压控振荡器(即lc压控振荡器)包括由电感和电容组成的谐振电路,以及由交叉耦合晶体管对组成的负阻电路。

27.参考图1,所述压控振荡器包括:谐振电路(未标示),所述谐振电路具有第一输出端op和第二输出端on,且所述谐振电路包括并联连接的电感l和电容c(如图1中虚线框所示);尾电流源10;负阻电路(未标示),包括第一nmos晶体管(即nm1)和第二nmos晶体管(即nm2),所述第一nmos晶体管的漏极d和第二nmos晶体管的栅极g共接于所述第一输出端op,所述第一nmos晶体管的栅极g和第二nmos晶体管的漏极d共接于所述第二输出端on,所述第一nmos晶体管的体端b接地,所述第一nmos晶体管的源极s与所述尾电流源10相连,所述第

二nmos晶体管的体端b接地,所述第二nmos晶体管的源极s与所述尾电流源10相连。

28.结合参考图2,图2是一种半导体结构的结构示意图。

29.参考图2,所述半导体结构包括:衬底20;分立于所述衬底20上的第一栅极结构25和第二栅极结构35;第一n型重掺杂(n+)区21,位于所述第一栅极结构25一侧的衬底20中;第二n型重掺杂区22,位于所述第一栅极结构25另一侧的衬底20中;第一p型重掺杂(p+)区23,位于所述第二n型重掺杂区22远离所述第一栅极结构25一侧的衬底20中;第三n型重掺杂31,位于所述第二栅极结构35一侧的衬底20中;第四n型重掺杂区32,位于所述第二栅极结构35另一侧的衬底20中;第二p型重掺杂区33,位于所述第四n型重掺杂区32远离所述第二栅极结构35一侧的衬底20中。

30.所述第一栅极结构25、第一n型重掺杂区21、第二n型重掺杂区22和第一p型重掺杂区23构成第一晶体管20;所述第二栅极结构35、第三n型重掺杂31、第四n型重掺杂区32和第二p型重掺杂区33构成第二晶体管30。

31.其中,第一n型重掺杂区21作为第一晶体管20的漏极,第二n型重掺杂区22作为第一晶体管20的源极,第一p型重掺杂区23作为第一晶体管20的体端;第三n型重掺杂31作为第二晶体管30的漏极,第四n型重掺杂区32作为第二晶体管30的源极,第二p型重掺杂区33作为第二晶体管30的体端。

32.具体地,以所述第一晶体管20为所述压控振荡器中的第一nmos晶体管或第二nmos晶体管,所述第二晶体管30为外部电路的晶体管为例,对目前压控振荡器的相位噪声有待改善的原因进行说明。

33.由于第一p型重掺杂区23和第二p型重掺杂区33位于同一衬底20中,且未通过其他掺杂区或隔离结构进行隔离,因此,第一nmos晶体管和第二nmos晶体管的体端与外部电路的晶体管的体端相连,相应的,受到目前半导体结构的限制,第一nmos晶体管和第二nmos晶体管的体端b必须接地vss。

34.因此,如图1所示,受到目前半导体结构的限制,当第一nmos晶体管的源级s和第二nmos晶体管的源极s需要与尾电流源10相连时,第一nmos晶体管的源级s和体端b处于不同电位,第二nmos晶体管的源级s和体端b也处于不同电位,从而导致负阻电路中nmos晶体管的衬偏效应明显,进而影响nmos晶体管的性能,相应恶化压控振荡器的相位噪声。

35.而且,如图2所示,第一nmos晶体管和第二nmos晶体管与外部电路的晶体管具有相同的体衬底(即衬底20),因此,衬底20的噪声抖动会直接影响第一nmos晶体管和第二nmos晶体管的性能,从而恶化压控振荡器的相位噪声。

36.为了解决所述技术问题,本发明实施例提供一种压控振荡器,包括:谐振电路,所述谐振电路具有第一输出端和第二输出端;电流源;负阻电路,包括第一晶体管和第二晶体管,所述第一晶体管和第二晶体管均为nmos晶体管,所述nmos晶体管的衬底中具有p型阱区、以及包围所述p型阱区的n型阱区,所述p型阱区具有体端,所述第一晶体管的漏极和第二晶体管的栅极共接于所述第一输出端,所述第一晶体管的栅极和第二晶体管的漏极共接于所述第二输出端,所述第一晶体管的体端和源极相连并共接于所述电流源,所述第二晶体管的体端和源极相连并共接于所述电流源。

37.本发明实施例提供的压控振荡器中,负阻电路包括第一晶体管和第二晶体管,第一晶体管和第二晶体管均为nmos晶体管,所述nmos晶体管的衬底中具有p型阱区、以及包围

所述p型阱区的n型阱区,p型阱区具有体(bulk)端,所述第一晶体管的体端和源极相连并共接于所述电流源,所述第二晶体管的体端和源极相连并共接于所述电流源;其中,通过在nmos晶体管的衬底中设置n型阱区,以隔离nmos晶体管的p型阱区和衬底,也就是说,隔离了nmos晶体管的体衬底(也即p型阱区)和外部衬底,从而能够在衬底(也即外部衬底)的电位连接方式不受影响的情况下,使得nmos晶体管的体端和源极能够相连,体端和源极的电位差(即vbs)为零,相应能够改善或消除nmos晶体管的衬偏效应,同时,通过n型阱区来隔离p型阱区和衬底,有利于隔绝外界衬底噪声的影响,上述两个方面均有利于改善压控振荡器的相位噪声。

38.为使本发明实施例的上述目的、特征和优点能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

39.图3是本发明压控振荡器一实施例的电路结构示意图,图4是图3所示负阻电路中nmos晶体管一实施例的结构示意图。

40.所述压控振荡器包括:谐振电路20,所述谐振电路20具有第一输出端op和第二输出端on;电流源30;负阻电路(未标示),包括第一晶体管41和第二晶体管42,所述第一晶体管41和第二晶体管42均为nmos晶体管,所述nmos晶体管的衬底100中具有p型阱区140、以及包围所述p型阱区140的n型阱区110,所述p型阱区140具有体端bulk,所述第一晶体管41的漏极d和第二晶体管42的栅极g共接于所述第一输出端op,所述第一晶体管41的栅极g和第二晶体管42的漏极d共接于所述第二输出端on,所述第一晶体管41的体端bulk和源极s相连并共接于所述电流源30,所述第二晶体管42的体端bulk和源极s相连并共接于所述电流源30。

41.本实施例中,通过在负阻电路的nmos晶体管的衬底100中设置n型阱区110,以隔离nmos晶体管的p型阱区140和衬底100,也就是说,n型阱区110隔离了nmos晶体管的体衬底(即p型阱区140,也即nmos晶体管的内部衬底)和外部衬底,从而能够在衬底100(也即外部衬底)的电位连接方式不受影响的情况下,使得nmos晶体管的体端bulk和源极s能够相连,体端bulk和源极s的电位差(即vbs)为零,相应能够改善或消除nmos晶体管的衬偏效应,同时,通过n型阱区110来隔离p型阱区140和衬底100,有利于隔绝外部衬底噪声的影响,上述两个方面均有利于改善压控振荡器的相位噪声。

42.压控振荡器是构成锁相环的重要组成部分,用于提供振荡频率。

43.本实施例中,所述压控振荡器为电容电感压控振荡器(即lc压控振荡器)。

44.所述谐振电路20用于产生振荡频率,从而产生压控振荡器的振荡信号。

45.本实施例中,所述谐振电路20具有第一输出端op和第二输出端on,用于与负阻电路相连。

46.本实施例中,所述谐振电路20为电感电容式谐振电路(即lc谐振电路)。

47.因此,所述谐振电路20包括并联连接的电感l和电容c(如图3中虚线框所示)。

48.振荡频率是衡量压控振荡器性能的主要参数之一。压控振荡器的振荡频率主要由谐振电路20中的电感l和电容c决定。

49.具体地,所述电感l的两端分别与所述第一输出端op和第二输出端on耦接,所述电容c的两端分别与所述第一输出端op和第二输出端on耦接。

50.本实施例中,所述电容c包括可变电容和电容矩阵中的一种或两种。电容矩阵有利

于扩大压控振荡器的频率可调范围。

51.其中,所述电容矩阵可以包括固定电容阵列(cap array)和可变电容阵列(varactor array)中的一种或两种。固定电容阵列连接在第一输出端op和第二输出端on之间。可变电容阵列耦接在第一输出端op和第二输出端on之间。

52.如图3所示,作为一种示例,示出了所述电容c为可变电容的情况。

53.所述电流源30用于产生压控振荡器的工作电流,从而使压控振荡器正常工作。

54.本实施例中,所述电流源30即为尾电流源。通过尾电流源,从而减小电源噪声对压控振荡器的影响,进而有利于使得压控振荡器的输出信号的频率更加稳定。

55.所述负阻电路包括第一晶体管41和第二晶体管42,所述负阻电路由交叉耦合晶体管构成,用于提供负阻,从而补偿所述谐振电路20中的能量损失(即抵消所述谐振电路20产生的正阻),进而保证压控振荡器可以持续地工作。

56.因此,所述第一晶体管41的漏极d和第二晶体管42的栅极g共接于所述第一输出端op,所述第一晶体管41的栅极g和第二晶体管42的漏极d共接于所述第二输出端on。

57.本实施例中,所述交叉耦合晶体管是指将两个相同尺寸、相同类型的mos晶体管以交叉耦合的连接方式组成的一种结构。因此,所述第一晶体管41和第二晶体管42的沟道导通类型相同,所述第一晶体管41和第二晶体管42均为nmos晶体管。

58.相应的,所述压控振荡器通过第一晶体管41和第二晶体管42背靠背交叉正反馈连接以提供负阻。

59.结合参考图4,图4是图3所示负阻电路中nmos晶体管所对应半导体结构一实施例的结构示意图。其中,所述第一晶体管41和第二晶体管42均为nmos晶体管,因此,图4可以表示所述第一晶体管41和第二晶体管42中任一个晶体管所对应半导体结构的结构示意图。

60.本实施例中,所述衬底100为平面衬底。

61.本实施例中,所述衬底100的材料为硅。在另一些实施例中,所述衬底的材料还可以为锗、锗化硅、碳化硅、砷化镓或镓化铟等其他材料,所述衬底还能够为绝缘体上的硅衬底或者绝缘体上的锗衬底等其他类型的衬底。

62.本实施例中,所述第一晶体管41和第二晶体管41的衬底100均为p型衬底(p-sub),也即所述nmos晶体管的衬底100为p型衬底,也就是说,所述衬底100中掺杂有p型离子。其中,p型离子包括b离子、ga离子或in离子。

63.具体地,所述p型衬底接地。

64.所述nmos晶体管的衬底100中具有p型阱(p-well)区140、以及包围所述p型阱区140的n型阱区110,所述p型阱区140具有体端bulk。

65.所述p型阱区140作为所述nmos晶体管的体衬底,用于提供所述nmos晶体管的沟道。因此,所述p型阱区140具有体端bulk,用于提供所述p型阱区140的外接端子。

66.本实施例中,所述p型阱区140中的掺杂离子为p型离子。

67.本实施例中,所述n型阱区110包围所述p型阱区140,所述n型阱区110用于为nmos晶体管提供独立的体衬底,且有利于隔绝外界衬底噪声的影响。

68.所述n型阱区110中掺杂离子的导电类型与衬底100中掺杂离子的导电类型不同,从而隔离nmos晶体管的p型阱区140和衬底100,也就是说,隔离了nmos晶体管的体衬底和外部衬底。

69.所述n型阱区110中的掺杂离子为n型离子。其中,n型离子包括p离子、as离子或sb离子。

70.本实施例中,所述n型阱区110包括:位于所述p型阱区140底部的第一n型阱区111,所述p型阱区140在所述第一n型阱区111中的投影位于所述第一n型阱区111内部,且所述第一n型阱区111为深n型阱(dnw)区;环绕所述p型阱区140的第二n型阱(n-well)区112,所述第二n型阱区112与相对应的所述第一n型阱区111相连,所述第二n型阱区112的离子掺杂浓度小于所述第一n型阱区111的离子掺杂浓度。

71.其中,所述第一n型阱区111通过深n阱(deep nwell)工艺形成。

72.具体地,所述第二n型阱区112的底部与相对应的所述第一n型阱区111相连。在另一些实施例中,也可以为:所述第二n型阱区的侧壁和所述第一n型阱区的侧壁相连。

73.所述第二n型阱区112与相对应的所述第一n型阱区111相连,从而通过第二n型阱区112和第一n型阱区111包围所述p型阱区140。

74.本实施例中,所述衬底100表面露出的n型阱区110中具有n型接触区113,所述n型接触区113用于作为相对应的所述n型阱区110的外接端子。

75.所述n型接触区113用于作为对n型阱区110施加电位的电连接位置。

76.本实施例中,所述n型接触区113为n型重掺杂(n+)区,所述n型接触区113的离子掺杂浓度大于n型阱区110的掺杂浓度,以减小所述n型接触区113的接触电阻。

77.具体地,所述n型接触区113位于第二n型阱区112中,所述n型接触区113的离子掺杂浓度大于第二n型阱区112的离子掺杂浓度。

78.本实施例中,所述n型阱区110浮接(floating)。

79.结合参考图4和图5,图5是所述负阻电路中nmos晶体管在n型阱区110浮接的情况下所对应的等效电路图。

80.由于所述衬底100中具有p型阱区140、以及包围所述p型阱区140的n型阱区110,这相应引入了p型阱区140与位于所述p型阱区140下方的n型阱区110(具体为深n型阱区)之间的反偏二极管rwdio(如图4所示)、以及所述p型阱区140下方的n型阱区110(具体为深n型阱区)与衬底100之间的反偏二极管dnwdio(如图4所示),所述反偏二极管rwdio和反偏二极管dnwdio的等效电容分别为第一寄生电容c1(如图5所示)和第二寄生电容c2(如图5所示)。

81.在理想状态下,当需要较高的振荡频率时,只需将所述压控振荡器中相关的电容调小即可,但是,压控振荡器的寄生电容容易导致所述压控振荡器的实际频率和仿真时获得的计算频率之间具有误差。其中,第一寄生电容c1和第二寄生电容c2为所述压控振荡器的冗余电容,且非线性变化,因此容易导致所述压控振荡器的实际频率和仿真时获得的计算频率之间具有误差。

82.其中,当所述n型阱区110接固定电位时,则由所述反偏二极管rwdio和反偏二极管dnwdio构成的等效电容即为第一寄生电容c1。本实施例中,通过使所述n型阱区110浮接,以获得串联的第一寄生电容c1和第二寄生电容c2,所述反偏二极管rwdio和反偏二极管dnwdio的等效串联电容值为c1*c2/(c1+c2),该等效串联电容值小于第一寄生电容c1的电容值,从而减小衬底100的寄生电容,进而减小对压控振荡器的实际频率的影响,减小所述压控振荡器的相位噪声。

83.本实施例中,所述衬底100上形成有栅极结构200,所述栅极结构200用于作为所述

nmos晶体的栅极g。

84.其中,所述栅极结构200可以为多晶硅栅极结构或金属栅极结构。

85.本实施例中,所述栅极结构200一侧的p型阱区140中形成有源掺杂区210s,所述栅极结构200另一侧的p型阱区140中形成有漏掺杂区210d。

86.所述源掺杂区210s作为所述nmos晶体管的源极s,所述漏掺杂区210d用于作为所述nmos晶体管的漏极d。

87.本实施例中,所述源掺杂区210s和漏掺杂区210d均为n型重掺杂(n+)区。

88.本实施例中,所述nmos晶体管的p型阱区140中还具有与所述源极s相隔离的第一p型接触区145,所述第一p型接触区145用于作为相对应的所述p型阱区140的体端。

89.所述第一p型接触区145用于作为对p型阱区140施加电位的电连接位置。

90.本实施例中,所述第一p型接触区145为p型重掺杂(p+)区,所述第一p型接触区145的离子掺杂浓度大于p型阱区140的掺杂浓度,以减小所述第一p型接触区145的接触电阻。

91.本实施例中,所述第一晶体管41的体端bulk和源极s相连并共接于所述电流源30,所述第二晶体管42的体端bulk和源极s相连并共接于所述电流源30。

92.由于n型阱区110隔离了nmos晶体管的体衬底和外部衬底,从而能够在衬底100(也即外部衬底)的电位连接方式不受影响的情况下,使得nmos晶体管的体端bulk和源极s能够相连,体端bulk和源极s的电位差(即vbs)为零,相应能够改善或消除nmos晶体管的衬偏效应,进而改善压控振荡器的相位噪声。

93.需要说明的是,本实施例中,所述第一晶体管41和第二晶体管42均为nmos晶体管。

94.其中,当第一晶体管和第二晶体管均为pmos晶体管时,由于pmos晶体管的衬底中通常形成有n型阱区,所述n型阱区具有体端,pmos晶体管具有独立的体衬底,因此,易于在衬底100的电位连接方式不受影响的情况下,使得pmos晶体管的体端和源极相连。

95.本实施例中,所述nmos晶体管的衬底100中还具有与所述n型阱区110相隔离的第二p型接触区130,所述第二p型接触区130用于作为相对应的所述衬底100的外接端子。

96.所述第二p型接触区130用于作为对衬底100施加电位的电连接位置。

97.本实施例中,所述衬底100接地,因此,所述第二p型接触区130接地vss。

98.由上述分析可知,在负阻电路中的nmos晶体管的体端bulk和源极s能够相连的情况下,所述衬底100仍可以接地vss。

99.本实施例中,所述第二p型接触区130为p型重掺杂(p+)区,所述第二p型接触区130的离子掺杂浓度大于衬底100的离子掺杂浓度,以减小所述第二p型接触区130的接触电阻。

100.相应的,本发明实施例还提供一种锁相环,所述锁相环包括本发明实施例提供的压控振荡器。

101.本实施例中,由于所述压控振荡器的相位噪声较小,这相应使得所述压控振荡器的输出信号的频率更加稳定、抖动更小,从而使得锁相环的相位噪声也小,有利于产生低相位噪声的高速时钟信号。

102.虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1