一种用于电容型逐次逼近模数转换器的电容排序电路

1.本发明涉及微电子学与固体电子学领域,特别是该领域中电容型逐次逼近模数转换器中的电容设置方法。

背景技术:

2.逐次逼近寄存器(sar)模数转换器(adc)具有良好的性能特征,被广泛用于传感器应用中。sar adc的典型结构主要包括采样保持电路、数模转换器(dac)、比较器和逻辑控制模块。其中,dac是sar adc中的最重要复杂的结构之一。对于电容式数模转换器(c

‑

dac),dac通过电容器内部的串行重新分配工作。但是随着对串行adc的广泛需求,c

‑

dac中的单位电容器数量将成倍增加。此外,dac的电容器失配将导致积分非线性(inl)和无杂散动态范围(sfdr)减小。因此,通常需要借助校准以满足于高精度sar adc的设计与应用。

3.然而,在sar adc的设计中,如何在有限的面积中达到最佳的精度和功耗权衡,并保证一定的速度,对设计者提出了很高的要求。特别针对高精度的sar adc的设计中,除了得益于工艺制造水平的不断提高,adc的结构也在不断改进外,高精度主要受电容的失配、比较器、噪声以及比较器的动态失调电压等非理想因素的影响。文献[tsukamoto s.a 10b 50ms/s 820μw sar adc with on

‑

chip digital calibration[j].tdx,2010,15(7):7.]提出了一种使用校准数模转换器(c

‑

dac)的直接自校准技术。但是,c

‑

dac和主dac(m

‑

dac)的分辨率、c

‑

dac的单元和寄生电容器的尺寸以及要校准的电容器值等各种参数之间的复杂关系成为优化设计和电路设计的障碍。文献[salvo a d.design of a 12

‑

bit sar adc with digital self

‑

calibration for radiation detectors front

‑

ends[c].conference on ph.d research in microelectronics and electronics,2019:125

‑

128.]提出一种基于偏移双转换(odc)方法的数字校准技术。该方法使用模拟失调注入来计算由于dac电容器之间的失配而引起的adc转换的固有误差。该方法通过找到一组权重,然后将其应用于每次转换以实现实时校正。虽然实现了有效位数(enob)从7.36提升至11.32,sfdr达到90db。但其数字校正电路会增加整体sar adc电路的功耗和面积,并增加了电路版图设计的复杂度,在实际应用中有较大的限制。文献[fan h,liu y,feng q.a reliable bubble sorting calibration method for sar adc[j].aeu

‑

international journal of electronics and communications,2020,122:153227.]中提出的一种模拟排序电路方法,该方法利用开关阵列的断开或者闭合实现记录整个排序过程中每个电容所在的位置。针对n个单位电容的排序,该方法中,需要n2根信号线将模拟模块与数字模块连接起来。

技术实现要素:

[0004]

本发明针对电荷重分配逐次逼近型模数转换器(sar adc)中的关键模块——数模转换器(dac)中电容阵列的技术缺陷,设计出一种用于电容型逐次逼近模数转换器的电容排序电路,克服了现有电容比较电路复杂不宜片上移植的缺陷。

[0005]

本发明技术方案为一种用于差分型逐次逼近模数转换器的电容排序电路,针对均

含有n个单位电容的正负电容阵列进行排序;正电容阵列的n个单位电容分别标记为c

p_0

、c

p_1

、c

p_2

……

c

p_n

‑1;负电容阵列的n个单位电容分别标记为c

n_0

、c

n_1

、c

n_2

……

c

n_n

‑1;所述电容排序电路包括:比较器、待排序电容c

p_0

~c

p_n

‑1和c

n_0

~c

n_n

‑1、开关电路、信号线line

p_0

~line

p_n

‑1和line

n_0

~line

n_n

‑1、控制输出模块;所述比较器的正负输入端均分为两路,一路通过开关连接共模电压v

cm

,另一路分别于正负电容阵列的上极板相连;待排序正电容阵列每个电容的输出端通过开关电路决定连接信号;待排序负电容阵列每个电容的输出端通过开关电路决定连接信号,正负电容阵列的开关电路分别由信号线line

p_0

~line

p_n

‑1和信号线line

n_0

~line

n_n

‑1控制;连接信号包括两种,一种为参考电压v

ref

,另一种为连接地;当信号线line

p_0

~line

p_n

‑1和信号线line

n_0

~line

n_n

‑1为高电平时,电容的输出端与参考电压v

ref

相连;当信号线line

p_0

~line

p_n

‑1和信号线line

n_0

~line

n_n

‑1为低电平时,电容的输出端与地相连;所述开关电路为每个待排序电容的输出端与每条信号线的输入端之间都设置的开关的开关群;需注意的是在差分型逐次逼近模数转换器中,将正负电容阵列相同位置的单位电容看成一个整体进行排序;组成待排序电容c0、c1、c2……

c

n

‑1;例:c

p_0

和c

n_0

看做一个整体并用标记为c0;

[0006]

对电容的排序通过分别对两个电容之间的比较实现;当比较c

x

与c

x+1

之间的电容大小时,首先关闭开关,使得正负阵列的电容上极板全部接v

cm

;其次,将c

p_x

的下极板与v

ref

相连接,正电容阵列其余电容的下极板与地相连;类似的,对应的负电容器阵列的电容c

n_x

下极板接地,负电容阵列其余电容的下极板与v

ref

相连;接着,开关k0断开,并将正负电容阵列电容的下极板的连接信号相互交换,即正电容阵列的c

p_x+1

的下极板与v

ref

相连接,正电容阵列其余电容的下极板与地相连;负电容器阵列的电容c

n_x+1

下极板接地,负电容阵列其余电容的下极板与v

ref

相连;根据电荷守恒原理,正负电容阵列上极板的电压将会发生变化,通过比较器的输出高低可以判断c

x

与c

x+1

之间的电容大小;其余电容之间的比较则重复上述操作。

[0007]

控制输出模块运用了一个大小为n

×

log2n存储器来记录整个排序过程中每个电容所在的位置,其中字0~字n分别存储一个log2n位二进制数,其中字0中存储00

…

00则代表c0,字1中存储00

…

01则代表c1,字2中存储00

…

10则代表c2…

字n中存储11

…

11则代表c

n

;n个电容排序共需要n-1轮比较;其中,第一轮需要依次比较相邻的电容,共需要n-1次直至得到最大的电容,第二轮需要依次比较相邻的电容,共需要n-2次直至得到第二大的电容,以此类推直至完成n-1轮比较,完成对n个电容由大到小的排序;本设计中,默认字n对应的电容为最大电容,字0对应的电容为最小电容;每一轮比较均从相邻的字0和字1对应的两个电容开始;例如:第一轮排序的第一次比较从相邻的字0和字1对应的两个电容开始。如果字0对应的电容大于字1对应的电容,则交换字0和字1中存储的值,如果字0对应的电容小于字1对应的电容时,则字0和字1中存储的值保持不变;按照此过程不断进行相邻的比较,直到完成第n-1次比较(字n

‑

1与字n的比较)。此时,完成了第一轮比较,字n所对应的电容为最大的电容。按照上述的过程,对于n个电容排序共需要进行n-1轮比较,即(n2-n)/2次比较。排序完成后,字0~字n中分别存储着从小到大排列的电容。

[0008]

本发明提出的排序电路与现有电路相比,排序n个电容,可以将数模连接信号线数量由n2减小至2n。因此,针对高精度sar adc,本发明排序电路可以克服模拟排序电路因连接信号线过多而无法应用于高精度sar adc的限制。

附图说明

[0009]

图1为本发明实施的8位混合电阻电容型主dac结构示意图。

[0010]

图2本发明提出的比较电容电路示意图。

[0011]

图3为本发明提出的电容排序原理流程图。

[0012]

图4为文献[fan h,liu y,feng q.a reliable bubble sorting calibration method for sar adc[j].aeu

‑

international journal of electronics and communications,2020,122:153227.]中提出的一种模拟排序电路方法示意图。

[0013]

图5为本发明提出的电容排序电路示意图。

[0014]

图6本发明实施的8位sar adc的fft频谱结果对比图(a)未校正(b)校正后。

具体实施方式

[0015]

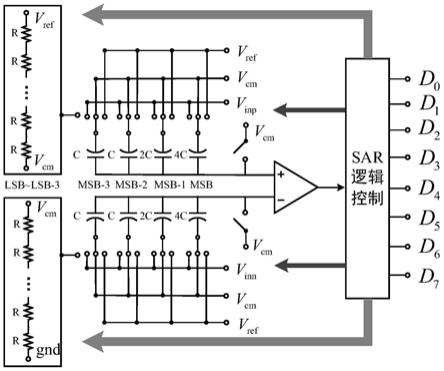

本发明针对由高4位电容dac和低4位电阻dac组成的8位电容电阻混合型逐次逼近模数转换器为例进行详述。高4位电容dac和低4位电阻dac的8位混合电容电阻型逐次逼近模数转换器结构如图1所示。

[0016]

针对高4位电容dac,需要依次通过电容之间的两两比较实现对8个电容的排序。图2详细叙述电容c0和电容c1比较过程。首先,如图2(a)所示,关闭开关k0,使得正负阵列的电容上极板全部接与v

cm

。其次,将c

p_0

底极板连接到v

ref

;正电容阵列的其余电容的底极板接地。同时,对应的负电容器阵列的电容c

n_0

底极板接地;负电容阵列的其余电容的底极板连接到v

ref

。此时,正负阵列的电荷分别为q

p

和q

n

,得到:

[0017]

q

p

=(c

p

‑0+c

p

‑1+c

p

‑2+c

p

‑3+c

p

‑4+c

p

‑5+c

p

‑6+c

p

‑7)

×

v

cm

‑

c

p

‑0×

v

ref

ꢀꢀꢀ

(1)

[0018][0019]

接着,如图2(b)所示,开关k0断开,交换电容c

p_0

和c

p_1

及c

n_0

和c

n_1

的开关连接状态,即c

p_0

的底极板接地;电容c

p_1

的底极板接v

ref

,正电容阵列的其余电容的底极板连接保持不变。同时,对应的负电容器阵列的电容c

n_0

的底极板接v

ref

;电容c

n_1

的底极板接地,负电容阵列的其余电容的的底极板连接保持不变。

[0020]

q

p

=(c

p

‑0+c

p

‑1+c

p

‑2+c

p

‑3+c

p

‑4+c

p

‑5+c

p

‑6+c

p

‑7)

×

v

p

'

‑

c

p

‑1×

v

ref

ꢀꢀꢀ

(3)

[0021]

q

n

=(c

n

‑0+c

n

‑1+c

n

‑2+c

n

‑3+c

n

‑4+c

n

‑5+c

n

‑6+c

n

‑7)

×

v’n

‑

(c

n

‑0+c

n

‑2+c

n

‑3+c

n

‑4+c

n

‑5+c

n

‑6+c

n

‑7)

×

v

ref

[0022]

(4)

[0023]

v

p

*和v

n

*分别表示正负电容器阵列顶极板的电压,根据电荷守恒原理,将式(1)与式(3),式(2)与式(4)联立,得到:

[0024][0025]

[0026]

由于正负电容器阵列的电容总量相等,即:

[0027]

c

p

‑0+c

p

‑1+c

p

‑2+c

p

‑3+c

p

‑4+c

p

‑5+c

p

‑6+c

p

‑7[0028]

=c

n

‑0+c

n

‑1+c

n

‑2+c

n

‑3+c

n

‑4+c

n

‑5+c

n

‑6+c

n

‑7[0029]

=c

tot

[0030]

(7)

[0031]

比较器两端的电压差为:

[0032][0033]

根据比较器的输出v

out

可以判断哪个电容更大,如果v

out

为高,则c0<c1;否则,c0>c1。可以重复上述方法进行其他电容器之间的比较。

[0034]

在比较电容的同时,需要一个8

×

3存储器来记录整个排序过程中每个电容所在的位置。8个电容的排序过程如图3所示。图3(a)代表排序的初始阶段,其中字0中存储000则代表c0,字1中存储001则代表c1,字2中存储010则代表c2,字3中存储011则代表c3,字4中存储100则代表c4,字5中存储101则代表c5,字6中存储110则代表c6,字7中存储111则代表c7。假定这八个电容的大小排序为:c0>c1>c3>c4>c2>c6>c7>c5。对于8个电容进行排序共需要7轮比较。其中,第一轮需要依次比较相邻的电容,共需要7次直至得到最大的电容,第二轮需要依次比较相邻的电容,共需要6次直至得到第二大的电容,以此类推直至完成7轮比较,完成对8个电容由大到小的排序。本发明中,默认字7对应的电容为最大电容,字0对应的电容为最小电容。

[0035]

排序第一轮第一次比较先从相邻的字0和字1对应的两个电容开始,即c1和c2。通过控制输出模块的信号线line

p_0

~line

p_7

和line

n_0

~line

n_7

对正负电容阵列的下极板按照上述的方法连接不同的信号以完成电容比较。如果c0>c1时,则交换字0和字1中存储的值,如果c0<c1时,则字0和字1中存储的值保持不变,过程如图3(b)所示。排序第一轮第二次接着比较相邻的字1和字2对应的两个电容,即c1和c2。如果c1>c2时,则交换字1和字2中存储的值,如果c1<c2时,则字1和字2中存储的值保持不变,过程如图3(c)所示。

[0036]

完整的排序第一轮比较需要7次比较完成,第三次比较将对字2和字3对应的电容进行比较,第四次比较将对字3和字4对应的电容进行比较,第五次比较将对字4和字5对应的电容进行比较,第六次比较将对字5和字6对应的电容进行比较,第7次比较将对字6和字7对应的电容进行比较。每次对比后,字中存储的值将按照比较结果将按照上述步骤的方法进行调整。在排序第一轮比较完成后,可确定最大的电容。

[0037]

排序的第二轮比较依次从字0与字1开始,直至字5与字6比较结束。因此,排序的第二轮比较共需进行6次比较,完成后可确定第二大的电容值。剩余的每一轮比较同第一、二轮相同,每轮所需的比较次数依次减小。第三轮比较结束后,可确定第三大的电容。第四轮比较结束后,可确定第四大的电容。第五轮比较结束后,可确定第五大的电容。第六轮比较结束后,可确定第六大的电容。第七轮比较结束后,可确定最小的和第二小的电容。排序完成后,字0~字7的状态如图3(d)所示。

[0038]

将本设计提出的电容排序电路应用于专利zl201810742310.9中提出的电容排序再重组校正方法中,并使用xfab xt018工艺和1.8v电源电压搭建8位sar adc进行了仿真。设置电容失配率为1%。图4显示了校准前后的fft结果频谱图。表1分别对未经过数字排序

校准的8位sar adc与经过数字排序校准的8位sar adc的动态性能进行对比总结。经过数字排序校准后的8位sar adc,其enob提升0.6至7.9,sfdr提高了11.9db至57db,同时,将sndr提高了3.6db至49.3db。

[0039]

表1 8位sar adc校准前后的动态性能总结

[0040][0041]

本发明提出的电容排序电路,可广泛应用于基于电容排序重构的校准方法中。相比于文献[fan h,liu y,feng q.a reliable bubble sorting calibration method for sar adc[j].aeu

‑

international journal of electronics and communications,2020,122:153227.]中提出的电容排序电路,对比图4和图5,对于8个电容的排序,可将数模连接信号线数量由64减小至16。对于n个电容的排序,可将数模连接信号线数量由n2减小至2n。因此,对于高精度sar adc,该设计方法避免了因电容数量随精度成指数性增长而造成电容排序电路过于复杂,大大降低了数模连接信号线的数量,优化了电路。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1