半导体结构和操作电路的制作方法

1.本发明有关于一种半导体结构,特别是有关于一种高压半导体装置。

背景技术:

2.高压半导体装置是利用栅极电压来产生沟道,并控制流经源极与漏极之间的电流。在传统的高压半导体装置中,为了防止源极与漏极之间的击穿效应(punch-through effect),必须延长晶体管的沟道长度。然而,如此一来会增加装置的尺寸而使晶片面积增加且会使晶体管的导通电阻(on-resistance,ron)上升。

技术实现要素:

3.本发明的一实施例提供一种半导体结构,包括一基板、一第一阱区、一第二阱区、一第一掺杂区、一第二掺杂区、一栅极电极层、一绝缘层、一场板以及一可调电路。基板具有一第一导电型。第一阱区形成于基板之上,并具有第一导电型。第二阱区形成于基板之上,并具有一第二导电型。第一掺杂区形成于第一阱区之中,并具有第二导电型。第二掺杂区形成于第二阱区之中,并具有第二导电型。栅极电极层位于基板之上。栅极电极层、第一掺杂区及第二掺杂区构成一晶体管。绝缘层位于基板之上,并重叠部分栅极电极层。场板重叠绝缘层及栅极电极层。可调电路耦接场板、栅极电极层及第一掺杂区,并在场板与栅极电极层之间提供第一短路路径,或是在场板与第一掺杂区之间提供第二短路路径。

4.本发明另提供一种操作电路,包括一第一晶体管、一第一可调电路、一第二晶体管以及一第二可调电路。第一晶体管形成于一基板的一第一区域之中,并包括一第一场板接触端、一第一栅极接触端、一第一源极接触端。第一可调电路在第一场板接触端与第一栅极接触端之间形成一第一短路路径,或是在第一场板接触端与第一源极接触端之间形成一第二短路路径。第二晶体管形成于基板的一第二区域之中,并包括一第二场板接触端、一第二栅极接触端、一第二源极接触端。第二可调电路在第二场板接触端与第二栅极接触端之间形成一第三短路路径,或是在第二场板接触端与第二源极接触端之间形成一第四短路路径。

5.本发明提供的一种半导体结构,由于该半导体结构中金属至栅极架构的晶体管具有较低的导通电阻,故该半导体结构的功耗较低。同时,由于该半导体结构中金属至源极架构的晶体管具有较低的栅极电荷值,故该半导体结构的切换速度较快。由于品质因素(figure of merit;fom)正比于导通电阻及栅极电荷值的乘积,故该半导体结构中基板具有较佳的品质因素。

附图说明

6.图1为本发明的半导体结构的示意图。

7.图2为本发明的半导体结构的等效电路示意图。

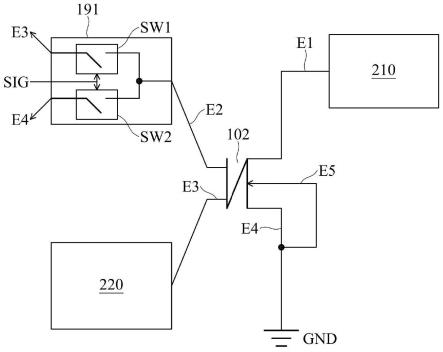

8.图3为本发明的可调电路的一可能实施例。

9.图4为本发明的半导体结构的另一示意图。

10.附图标记:

11.100、400:半导体结构

12.101、410:基板

13.111、112:阱区

14.121~123:掺杂区

15.140:栅极结构

16.150、170:绝缘层

17.160:场板

18.131、132:沟槽隔离物

19.141:栅极介电层

20.142:栅极电极层

21.gp:间隙

22.102、420、430、440、450:晶体管

23.190:线路层

24.191:可调电路

25.l1~l4:内连线

26.e1~e5:电极

27.181~185:贯孔

28.210:接触垫

29.220:控制电路

30.sig:控制信号

31.sw1、sw2:开关电路

32.gnd:接地电压

33.t1~t4:开关

34.iv1、iv2:反相器

35.sv1、sv2:反相信号

36.vp:高操作电压

37.411~414:区域

38.f1~f4:场板接触端

39.s1~s4:源极接触端

40.g1~g4:栅极接触端

41.d1~d4:漏极接触端

42.b1~b4:基极接触端

具体实施方式

43.让本发明的目的、特征和优点能更明显易懂,下文特举出实施例,并配合所附图式,做详细的说明。本发明说明书提供不同的实施例来说明本发明不同实施方式的技术特征。其中,实施例中的各元件的配置为说明之用,并非用以限制本发明。另外,实施例中图式

标号的部分重复,为了简化说明,并非意指不同实施例之间的关联性。

44.图1为本发明的半导体结构的示意图。如图所示,半导体结构100包括一基板101、阱区111、112、掺杂区121、122、一栅极结构140、一绝缘层150以及一场板160。在本实施例中,半导体结构100为一高压半导体结构,举例而言,可接收18v以上的电压。

45.基板101可为一半导体基板,例如是硅基板、外延iii-v族基板、硅锗基板、碳化硅基板或硅覆绝缘(silicon-on-insulator,soi)基板等。另外,基板101可能包括硅、锗化硅(sige)或iii-v族元素的半导体材料。在本实施例中,基板101具有一第一导电型。在其它实施例中,一埋层(buried layer:bl)120、第一阱区111以及第二阱区112设置在基板101内。

46.阱区111及112形成于基板101之中,其中,阱区111具有第一导电型。阱区112形成于阱区111之中,其中阱区112具有第二导电型。第一导电型与第二导电型相异。于一实施例中,埋层120例如具有该第二导电类型(如p型)位于阱区111与基板101之间,且其掺杂浓度较佳高于阱区112的掺杂浓度。在一可能实施例中,阱区111围绕阱区112。

47.掺杂区121形成于阱区111之中,并具有第二导电型。在本实施例中,掺杂区121的掺杂浓度高于阱区112的掺杂浓度。在一些实施例中,半导体结构100更包括一掺杂区123。掺杂区123形成于阱区111之中,并具有第一导电型。掺杂区123的掺杂浓度高于阱区111的掺杂浓度。在其它实施例中,可利用一浅沟槽隔离工艺(sti)形成一沟槽隔离物131于阱区111之中,用以分隔掺杂区121及123。然而,亦可以其它任何适合的方式分隔掺杂区121及123,例如亦可以传统的区域氧化法(locos)形成场氧化层,用以在阱区111隔离掺杂区121及123。

48.掺杂区122形成于阱区112之中,并具有第二导电型。在本实施例中,掺杂区122的掺杂浓度高于阱区112的掺杂浓度。在一些实施例中,利用浅沟槽隔离工艺形成一沟槽隔离物132于阱区112及111之中,用以分隔阱区111与掺杂区122。在其它实施例中,也可利用区域氧化法形成一场氧化层于阱区111与掺杂区123之间。

49.栅极结构140位于基板101之上,并重叠部分的阱区111及112。栅极结构140包括一栅极介电层141以及一栅极电极层142。在本实施例中,栅极介电层141形成于阱区111及112的部分表面上。栅极介电层141可包括例如氧化物(oxide)、氮化物(nitride)、氮氧化物(oxynitride)、碳氧化物(oxycarbide)、上述的组合或高介电常数(high-k,介电常数大于8)的介电材料。接着,于栅极介电层141上形成栅极电极层142。在一些实施例中,栅极电极层142包括硅或多晶硅(polysilicon)。栅极电极层142较佳为掺杂掺质以降低其片电阻(sheet resistance)。在其他实施例中,栅极电极层142包括非晶硅(amorphous silicon)。此外,栅极电极层142表面也可以具有金属氮化物或金属硅化物。在一些实施例中,栅极结构140与掺杂区122之间具有一间隙gp。换句话说,栅极结构140并未接触掺杂区122。

50.在本实施例中,栅极电极层142、掺杂区121及122构成一晶体管102。本发明并不限定晶体管102的种类。在一可能实施例中,晶体管102为一横向扩散金属氧化物半导体(lateral diffused mos;ldmos)晶体管。在此例中,栅极电极层142作为晶体管102的栅极(gate),掺杂区121作为晶体管102的源极(source),掺杂区122作为晶体管102的漏极(drain)。在其它实施例中,晶体管102更包括掺杂区123。在此例中,掺杂区123作为晶体管102的基极(bulk)。

51.绝缘层150位于基板101之上,并重叠部分的栅极结构140。在本实施例中,绝缘层

150重叠并直接接触部分的掺杂区122、部分的阱区122以及部分的栅极电极层142。绝缘层150的材料包括氧化物、氮化物、氮氧化物、低介电常数材料、其它任何适合的绝缘材料、或上述的组合,且可通过上述化学气相沉积工艺形成。在一些实施例中,绝缘层150与栅极介电层141在不同的工艺形成,但并非用以限制本发明。在其它实施例中,绝缘层150与栅极介电层141在同一工艺(如化学气相沉积工艺)形成。在本实施例中,绝缘层150的厚度大于栅极介电层141的厚度。

52.场板160位于绝缘层150之上,并重叠部分的掺杂区122及栅极介电层141。在本实施例中,场板160直接接触绝缘层150并重叠部分的绝缘层150。场板160用以均匀化电场的分布。在一可能实施例中,场板160为一导体,其材料包括金属(metal)或硅。

53.在一些实施例中,半导体结构100更包括一绝缘层170。绝缘层170覆盖阱区111、112、掺杂区121~123、沟槽隔离物131、132、栅极结构140、绝缘层150及场板160。因此,场板160与栅极介电层141位于同一绝缘层之中。在一些实施例中,绝缘层150与170在不同的工艺形成。举例而言,在形成绝缘层150后,先在绝缘层150之上形成场板160后,才形成绝缘层170。

54.在一些实施例中,半导体结构100更包括线路层190。线路层190具有一可调电路(tunable circuit)191、内连线l1~l3以及电极e1~e5。电极e1通过贯孔(through hole)181,电连接掺杂区122。在一可能实施例中,电极e1作为晶体管102的漏极接触端。电极e2通过贯孔182,电连接场板160。在一可能实施例中,电极e2作为晶体管102的场板接触端。电极e3通过贯孔183,电连接栅极电极层142。在一可能实施例中,电极e3作为晶体管102的栅极接触端。电极e4通过贯孔184,电连接掺杂区121。在一可能实施例中,电极e4作为晶体管102的源极接触端。电极e5通过贯孔185,电连接掺杂区123。在一可能实施例中,电极e5作为晶体管102的基极接触端。

55.在本实施例中,可调电路191通过内连线l1~l3,电连接电极e2~e4。在此例中,可调电路191可能在场板160与栅极电极层142之间提供一第一短路路径,或是在场板160与掺杂区121之间提供一第二短路路径。当场板160与栅极电极层142之间具有第一短路路径时,场板160的电位将相同于栅极电极层142的电位。此时,晶体管102具有第一导通电阻(ron)以及第一栅极电荷值(gate charge;qg)。当场板160与掺杂区121之间具有第二短路路径时,场板160的电位将相同于掺杂区121的电压。此时,晶体管102具有第二导通电阻以及第二栅极电荷值。在此例中,第一导通电阻小于第二导通电阻,第二栅极电荷值小于第一栅极电荷值。

56.本发明并不限定可调电路191的架构。在一可能实施例中,可调电路191根据一控制信号(未显示),导通电极e2与e3之间的第一短路路径,或是导通电极e2与e4之间的第二短路路径。当可调电路191导通电极e2与e3之间的第一短路路径时,场板160的电位等于栅极电极层142的电位。当可调电路191导通电极e2与e4之间的第二短路路径时,场板160的电位等于掺杂区121的电位。

57.在其它实施例中,线路层190更包括一内连线l4。内连线l4可能电连接电极e4及e5。在一些实施例中,内连线l1~l4的材料可包括铜、铝、钨、掺杂多晶硅、其它任何适合的导电材料、或上述的组合。

58.图2为本发明的半导体结构100的等效电路示意图。如图所示,半导体结构100包括

一晶体管102以及一可调电路191。晶体管102的掺杂区122电连接电极e1(或称漏极接触端)。在本实施例中,电极e1耦接一接触垫(pad)210。接触垫210用以接收一控制电压。在一可能实施例中,控制电压约为40v。

59.晶体管102的场板160电连接电极e2(或称场板接触端)。电极e2耦接可调电路191。晶体管102的栅极电极层142电连接电极e3(或称栅极接触端)。电极e3耦接一控制电路220。控制电路220用以提供一栅极电压予电极e3。通过控制电极e1、e3及e4的电位,便可导通或不导通晶体管102。晶体管102的掺杂区121电连接电极e4(或称源极接触端)。电极e4接收一接地电压gnd。晶体管102的掺杂区123电连接电极e5(或称基极接触端)。电极e5耦接电极e4。

60.在本实施例中,可调电路191可能根据一控制信号sig,导通电极e2与e3之间的一第一短路路径,或是导通电极e2与e4之间的一第二短路路径。本发明并不限定控制信号sig的来源。在一可能实施例中,控制信号sig可能来自一次性写入存储器(one time programmable;otp)电路或是多次写入存储器(multiple time programmable;mtp)电路。

61.另外,本发明并不限定可调电路191的架构。任何可根据一控制信号,提供两不同的短路路径的电路,均可作为可调电路191。在一可能实施例中,可调电路191包括开关电路sw1及sw2。开关电路sw1耦接于电极e2与e3之间,用以在电极e2与e3之间形成一第一短路路径。开关电路sw2耦接于电极e2与e4之间,用以在电极e2与e4之间提供一第二短路路径。在一些实施例中,可调电路191不会同时导通第一及第二短路路径。

62.举例而言,当控制信号sig等于一第一电平(如高电平)时,开关电路sw1导通,开关电路sw2不导通。在此例中,由于开关电路sw1导通,故在电极e2与e3之间具有一第一短路路径。因此,电极e2与e3具有相同的电位。此时,晶体管102具有第一导通电阻以及第一栅极电荷值。在此例中,由于开关电路sw2不导通,故开关电路sw2并未在电极e2与e4之间提供第二短路路径。

63.当控制信号sig等于一第二电平(如低电平)时,开关电路sw1不导通,开关电路sw2导通。在此例中,由于开关电路sw2导通,故电极e2与e4之间具有一第二短路路径。因此,电极e2的电位等于电极e4的电位,并且晶体管102具有第二导通电阻以及第二栅极电荷值。在一可能实施例中,第一导通电阻小于第二导通电阻,第二栅极电荷值小于第一栅极电荷值。在电极e2与e4之间具有第二短路路径时,开关电路sw1不导通。因此,开关电路sw1并未在电极e2与e3之间形成第一短路路径。

64.在本实施例中,开关电路sw1及sw2接收同一控制信号,但并非用以限制本发明。在其它实施例中,开关电路sw1及sw2接收不同的控制信号。在此例中,当开关电路sw1于电极e2及e3间提供第一短路路径时,开关电路sw2不在电极e2与e4之间提供第二短路路径。当开关电路sw2于电极e2及e4间提供第二短路路径时,开关电路sw1不在电极e2与e3之间提供第一短路路径。

65.图3为本发明的可调电路的一可能实施例。在本实施例中,开关电路sw1包括一反相器iv1、开关t1及t2。反相器iv1反相控制信号sig,用以产生一反相信号sv1。开关t1耦接于电极e2与e3之间,并接收反相信号sv1。开关t2耦接于电极e2与e3之间,并接收控制信号sig。本发明并不限定开关t1与t2的种类。在一可能实施例中,开关t1为一n型晶体管,开关t2为一p型晶体管。在此例中,开关t1的基极接收一接地电压gnd,开关t2的基极接收一高操

作电压vp。当控制信号sig等于第一电平(如高电平)时,开关t1与t2不导通。当控制信号sig等于第二电平(如低电平)时,开关t1与t2导通。因此,电极e2的电位等于电极e3的电位。

66.开关电路sw2包括一反相器iv2、开关t3及t4。反相器iv2反相控制信号sig,用以产生一反相信号sv2。开关t3耦接于电极e2与e4之间,并接收控制信号sig。开关t4耦接于电极e2与e4之间,并接收反相信号sv2。本发明并不限定开关t3与t4的种类。在一可能实施例中,开关t3为一n型晶体管,开关t4为一p型晶体管。在此例中,开关t3的基极接收接地电压gnd,开关t4的基极接收高操作电压vp。当控制信号sig等于第一电平(如高电平)时,开关t3与t4导通。因此,电极e2的电位等于电极e4的电位。当控制信号sig等于第二电平(如低电平)时,开关t3与t4不导通。

67.图4为本发明的半导体结构的另一示意图。半导体结构400包括一基板410。基板410具有区域411~414。本发明并不限定区域的数量。在其它实施例中,基板410被划分成更多或更少的区域。在本实施例中,区域411~414的每一者的结构相似于图1所示的半导体结构100。

68.区域411~414的每一者具有多个晶体管。为方便说明,图4仅显示晶体管420、430、440及450。晶体管420、430、440及450分别位于区域411~414之中。在一可能实施例中,晶体管420、430、440及450为硅晶体管(silicon mos),例如横向扩散金属氧化物半导体晶体管,或高电子迁移率晶体管(hemt),例如氮化镓高电子迁移率晶体管。在本实施例中,由于晶体管420、430、440及450的结构相同于图1的晶体管102的结构,故不再赘述。

69.晶体管420位于区域411之中,并具有一栅极接触端g1、一漏极接触端d1、一源极接触端s1、一基极接触端b1以及一场板接触端f1。晶体管420根据栅极接触端g1、漏极接触端d1以及源极接触端s1的电位而动作。在一些实施例中,基极接触端b1可能电连接源极接触端s1。在此例中,一第一可调电路(未显示)于场板接触端f1和栅极接触端g1之间设置一短路路径。因此,场板接触端f1电连接栅极接触端g1,但并非用以限制本发明。在其它实施例中,第一可调电路可能在场板接触端f1与源极接触端s1之间设置一短路路径。在一些实施例中,第一可调电路可能位于区域411之中。

70.晶体管430位于区域412之中,并具有一栅极接触端g2、一漏极接触端d2、一源极接触端s2、一基极接触端b2以及一场板接触端f2。晶体管430根据栅极接触端g2、漏极接触端d2以及源极接触端s2的电位而动作。在一些实施例中,基极接触端b2可能电连接源极接触端s2。在此例中,一第二可调电路(未显示)于场板接触端f2和源极接触端s2之间设置一短路路径。因此,场板接触端f2电连接源极接触端s2。在此例中,导通晶体管430所需的栅极电荷值小于导通晶体管420所需的栅极电荷值。因此,晶体管430具有较快的切换速度。在其它实施例中,第二可调电路可能于场板接触端f2和栅极接触端g2之间设置一短路路径。在一些实施例中,第二可调电路可能位于区域412之中。

71.晶体管440位于区域413之中,并具有一栅极接触端g3、一漏极接触端d3、一源极接触端s3、一基极接触端b3以及一场板接触端f3。晶体管440根据栅极接触端g3、漏极接触端d3以及源极接触端s3的电位而动作。在一些实施例中,基极接触端b3可能电连接源极接触端s3。在本实施例中,一第三可调电路(未显示)于场板接触端f3和栅极接触端g3之间设置一短路路径。因此,场板接触端f3电连接栅极接触端g3。在此例中,晶体管440的导通电阻及栅极电荷值相似于晶体管420的导通电阻及栅极电荷值。在一可能实施例中,晶体管440的

导通电阻小于晶体管430的导通电阻。因此,晶体管440的功耗低于晶体管430。在其它实施例中,第三可调电路可能在场板接触端f3与源极接触端s3之间设置一短路路径。在一些实施例中,第三可调电路可能位于区域413之中。

72.晶体管450位于区域414之中,并具有一栅极接触端g4、一漏极接触端d4、一源极接触端s4、一基极接触端b4以及一场板接触端f4。晶体管450根据栅极接触端g4、漏极接触端d4以及源极接触端s4的电位而动作。在一些实施例中,基极接触端b4可能电连接源极接触端s4。在本实施例中,一第四可调电路(未显示)于场板接触端f4和源极接触端s4之间设置一短路路径。因此,场板接触端f4电连接源极接触端s4。在此例中,晶体管450的导通电阻及栅极电荷值相似于晶体管430的导通电阻及栅极电荷值。另外,晶体管450的栅极电荷值小于晶体管420及440的栅极电荷值。在其它实施例中,第四可调电路可能在场板接触端f4与栅极接触端g4之间设置一短路路径。第四可调电路可能位于区域414之中。

73.在图4中,由于基板410被切分成区域411~414,并且区域411及413的晶体管的场板接触端电连接至栅极接触端,故在基板410中,大约有50%的晶体管属于金属至栅极(metal to gate;mtg)架构。另外,由于区域412及414的晶体管的场板接触端电连接至源极接触端,故在基板410中,大约有50%的晶体管属于金属至源极(metal to source;mts)架构。

74.由于金属至栅极(mtg)架构的晶体管具有较低的导通电阻,故金属至栅极架构的晶体管的功耗较低。金属至源极(mts)架构的晶体管具有较低的栅极电荷值,故金属至源极架构的晶体管的切换速度较快。由于品质因素(figure of merit;fom)正比于导通电阻及栅极电荷值的乘积,故基板410具有较佳的品质因素。

75.在其它实施例中,可能只有单一区域的晶体管的场板接触端电连接至栅极接触端。在此例中,具有mtg架构的晶体管的数量约为所有晶体管的25%。在另一可能实施例中,如果有三区域的晶体管的场板接触端电连接至栅极接触端,则具有mtg架构的晶体管的数量约为所有晶体管的75%。如果所有区域(如411~414)的晶体管的场板接触端电连接至栅极接触端,则具有mtg架构的晶体管的数量约为所有晶体管的100%。然而,如果区域411~414的晶体管的场板接触端均未电连接至栅极接触端,则具有mtg架构的晶体管的数量约为所有晶体管的0%。因此,使用者可依照实际应用,可调整mtg及mts架构的晶体管数量,进而优化品质因素,使得元件具有较高的效率。

76.本发明并不限定mtg架构的晶体管的所在区域。如果具有mtg架构的晶体管的数量被限制在50%时,则可通过调整前述的控制信号sig,使得在区域411~414的任两区域中具有mtg架构的晶体管。在本实施例中,由于区域411及413的可调电路(未显示)根据控制信号sig,导通场板接触端f1与栅极接触端g1之间的短路路径以及场板接触端f3与栅极接触端g3之间的短路路径,故区域411及413具有mtg架构的晶体管。在其它实施例中,如果区域411及412的可调电路(未显示)根据控制信号sig,导通场板接触端f1与栅极接触端g1之间的短路路径以及场板接触端f2与栅极接触端g2之间的短路路径,则区域411及412具有mtg架构的晶体管。同样地,如果区域411及414可调电路(未显示)根据控制信号sig,导通场板接触端f1与栅极接触端g1之间的短路路径以及场板接触端f4与栅极接触端g4之间的短路路径,则区域411及414具有mtg架构的晶体管。换言之,mtg架构或mts架构可随相对应的可调电路的控制信号sig不同而做动态调整。

77.在一些实施例中,每一区域里的短路路径并非固定不变。举例而言,当mtg架构的晶体管的数量被限制在50%时,则区域411及413的可调电路(未显示)根据控制信号sig,导通场板接触端f1与栅极接触端g1之间的短路路径以及场板接触端f3与栅极接触端g3之间的短路路径。然而,当mtg架构的晶体管的数量被改变限制在25%时,则区域411及413的一者的可调电路根据控制信号sig,导通场板接触端与栅极接触端之间的短路路径。在此例中,区域411及413的另一者的可调电路可能根据控制信号sig,导通场板接触端与源极接触端之间的短路路径。在一些实施例中,区域411及413的另一者的可调电路可能不导通场板接触端与源极接触端之间的短路路径以及场板接触端与栅极接触端之间的短路路径。

78.除非另作定义,在此所有词汇(包含技术与科学词汇)均属本发明所属技术领域中技术人员的一般理解。此外,除非明白表示,词汇于一般字典中的定义应解释为与其相关技术领域的文章中意义一致,而不应解释为理想状态或过分正式的语态。虽然“第一”、“第二”等术语可用于描述各种元件,但这些元件不应受这些术语的限制。这些术语只是用以区分一个元件和另一个元件。

79.虽然本发明已以较佳实施例揭露如上,然其并非用以限定本发明,任何所属技术领域中技术人员,在不脱离本发明的精神和范围内,当可作些许的更动与润饰。举例来说,本发明实施例所述的系统、装置或是方法可以硬件、软件或硬件以及软件的组合的实体实施例加以实现。因此本发明的保护范围当视权利要求范围所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1