电路板及其制造方法与流程

1.本发明涉及印刷电路板技术,尤其涉及一种电路板及其制造方法。

背景技术:

2.随着电子设备的多功能化及轻薄短小化的发展趋势,电路板的设计既要满足轻薄短小的要求,又要满足多功能化的要求。

3.然而,现有的电路板大多厚度比较厚,体积较大;由于绝缘层的存在,沿电路板的厚度方向上各线路层之间的距离较大,电路板的空间利用率低,难以满足上述要求。

技术实现要素:

4.鉴于以上内容,为了解决上述至少之一的缺陷,有必要提出一种电路板的制造方法。

5.另,本发明还提供了一种采用上述制造方法制造的电路板。

6.本发明提供一种电路板的制造方法,包括以下步骤:

7.提供一电路基板,包括基层以及设置于所述基层至少一表面的第一线路层。

8.于所述第一线路层的表面形成绝缘层和第一金属层。

9.蚀刻所述第一金属层以形成线路图形,所述线路图形设有用于暴露部分所述绝缘层的线路开口。

10.于暴露于所述线路开口的所述绝缘层中开设线路槽。

11.于所述线路槽内电镀形成第二线路层,并至少于所述线路开口内电镀,从而与所述线路图形共同形成第二金属层。

12.以及,蚀刻所述第二金属层以形成第三线路层,从而得到所述电路板。

13.本技术实施方式中,沿所述电路板的延伸方向,所述线路槽的尺寸小于或等于所述线路开口的尺寸。

14.本技术实施方式中,所述线路槽通过等离子蚀刻工艺形成。

15.本技术实施方式中,所述至少于所述线路开口内电镀具体包括:

16.于所述线路开口内和所述线路图形的表面上电镀。

17.本技术实施方式中,沿所述电路板的厚度方向上,所述第二线路层在所述第三线路层上的投影部分位于所述第三线路层的线路间隙内,且所述第二线路层与所述第三线路层电性连接;或,沿所述电路板的厚度方向上,所述第二线路层在所述第三线路层上的投影全部位于所述第三线路层的线路间隙内,且所述第二线路层与所述第三线路层不导通。

18.本技术实施方式中,所述第二线路层的线宽为10μm,线距为10μm。所述第三线路层的线宽为30μm,线距为30μm。

19.本技术实施方式中,沿所述电路板的厚度方向上,所述线路槽贯穿所述绝缘层,所述第二线路层与所述第一线路层接触并电性连接。

20.本发明还提供一种电路板,该电路板包括:电路基板、绝缘层、线路槽、第二线路层

以及第三线路层。所述电路基板包括基层以及设于所述基层至少一表面的第一线路层;所述绝缘层设于所述第一线路层的表面和所述第一线路层的线路间隙;所述线路槽开设于所述绝缘层,所述线路槽的开口位于所述绝缘层远离所述第一线路层的表面;所述第二线路层设于所述线路槽内并由所述开口露出;所述第三线路层至少设于所述绝缘层的表面。

21.本技术实施方式中,沿所述电路板的厚度方向上,所述第二线路层在所述第三线路层上的投影部分或全部位于所述第三线路层的线路间隙内。

22.本技术实施方式中,所述第二线路层的线宽为10μm,线距为10μm。所述第三线路层的线宽为30μm,线距为30μm。

23.本技术实施方式中,沿所述电路板的厚度方向上,所述线路槽贯穿所述绝缘层,所述第二线路层与所述第一线路层接触并电性连接。

24.相较于现有技术,本发明提供的电路板的制造方法在同一绝缘层制作出内埋的第二线路层和位于绝缘层表面的第三线路层这两种线路,两线路层之间避免增加另一绝缘层,制作流程更简单,提升了电路板线路制作的效率,成本更低,有利于降低电路板的整体厚度,使电路板更轻薄。

附图说明

25.图1为本发明一实施方式提供的覆铜板的示意图。

26.图2为在图1所示的覆铜板上形成第一线路层的示意图。

27.图3为在图2所示的第一线路层表面压合绝缘层和第一金属层的示意图。

28.图4为将图3所示的第一金属层内形成线路图形的示意图。

29.图5为在图4所示的绝缘层内形成线路槽的示意图。

30.图6为在图5所示的线路槽内形成第二线路层以及形成第二金属层的示意图。

31.图7为另一实施方式中在图5所示的线路槽内形成第二线路层以及形成第二金属层的示意图。

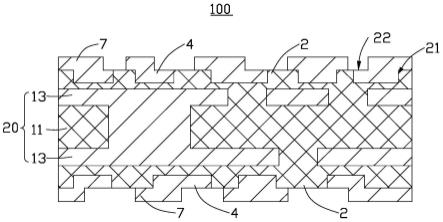

32.图8为将图6所示的第二金属层蚀刻成第三线路层的示意图。

33.主要元件符号说明

34.电路板

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

100

35.覆铜板

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

10

36.电路基板

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

20

37.基层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

11

38.铜箔层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

12

39.第一线路层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

13

40.单面覆铜板

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

30

41.绝缘层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ242.线路槽

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

21

43.开口

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

22

44.第一金属层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ345.线路图形

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

31

46.线路开口

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

32

47.第二线路层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ448.电镀层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ549.第二金属层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ650.第三线路层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ751.尺寸

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

a、b

52.如下具体实施方式将结合上述附图进一步说明本发明。

具体实施方式

53.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。

54.除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。

55.本发明一实施例提供一种电路板100的制造方法,该方法具体包括以下步骤:

56.步骤s11,请参阅图1,提供一覆铜板10,所述覆铜板10包括基层11以及设置于所述基层11至少一表面的铜箔层12。

57.本实施方式中,所述覆铜板10可以是单面覆铜板也可以是双面覆铜板,具体地,所述覆铜板10为双面覆铜板,在基层11相对的两表面均设有一层铜箔层12。

58.本实施方式中,所述基层11的材质为绝缘树脂,具体地,基层11的材质可以选自环氧树脂(epoxy resin)、半固化片(prepreg,pp)、bt树脂、聚苯醚(polyphenylene oxide,ppo)、聚酰亚胺(polyimide,pi)、聚对苯二甲酸乙二醇酯(polyethylene terephthalate,pet)以及聚萘二甲酸乙二醇酯(polyethylene naphthalate,pen)等树脂中的一种。

59.步骤s12,请参阅图2,蚀刻铜箔层12以形成第一线路层13,得到电路基板20。

60.本实施方式中,通过压膜、曝光、显影、蚀刻、去膜等制程制作所述第一线路层13。

61.步骤s13,请参阅图3,在所述第一线路层13的表面形成绝缘层2和第一金属层3。

62.本实施方式中,将一单面覆铜板30压合在第一线路层13的表面,单面覆铜板包括所述绝缘层2和所述第一金属层3,所述绝缘层2设于所述第一金属层3和所述第一线路层13之间。所述绝缘层2在压合后还填充于所述第一线路层13的线路间隙中。

63.本实施方式中,所述第一金属层3的厚度大致为3μm。

64.本实施方式中,所述绝缘层2的材质为绝缘树脂,具体地,绝缘层2的材质可以选自环氧树脂(epoxy resin)、半固化片(prepreg,pp)、bt树脂、聚苯醚(polyphenylene oxide,ppo)、聚酰亚胺(polyimide,pi)、聚对苯二甲酸乙二醇酯(polyethylene terephthalate,pet)以及聚萘二甲酸乙二醇酯(polyethylene naphthalate,pen)等树脂中的一种。

65.步骤s14,请参阅图4,蚀刻所述第一金属层3形成线路图形31,所述线路图形31设有用于暴露部分所述绝缘层2的线路开口32。

66.本实施方式中,通过化学刻蚀工艺将第一金属层3制作成所述线路图形31。

67.步骤s15,请参阅图5,于暴露于所述线路开口32的所述绝缘层2中开设线路槽21。

68.本实施方式中,沿所述电路板100的延伸方向,所述线路槽21的尺寸a等于所述线路开口32的尺寸b。在其它实施方式中,所述线路槽21的尺寸a也可以小于所述线路开口32

的尺寸b。

69.本实施方式中,通过等离子体刻蚀工艺对绝缘层2进行刻蚀形成所述线路槽21。等离子体刻蚀工艺是通过激发活性组分,使活性组分与绝缘层2的表面进行化学反应并形成挥发性的反应产物,进而对绝缘层2实现刻蚀的目的。通过活性组分的选择,可以只选择与绝缘层2进行化学反应的活性组分,这样,便能快速而精确地实现与线路开口32对应的绝缘层2的刻蚀,而且刻蚀形成的线路槽21的尺寸a较容易控制。

70.步骤s16,请参阅图6,于所述线路槽21内电镀以形成第二线路层4,并至少于所述线路开口32内电镀形成电镀层5,电镀层5与所述线路图形31共同形成第二金属层6。

71.本实施方式中,通过一次电镀形成所述第二线路层4以及所述第二金属层6。即,所述第二线路层4和所述第二金属层6为一体结构。所述第二线路层4的线宽10μm,所述第二线路层4的线距为10μm。所述第二线路层4通过埋线工艺(embedded trace process,et)制作而成。et工艺通过在线路槽21内电镀铜完成第二线路层4的埋线制程,单层线宽约8μm左右,线距约8μm左右。采用埋线工艺制作的内埋的第二线路层4,线路传导性较佳,线路无铜牙,线路接近方形,无侧蚀或残足问题。

72.请参阅图7,另一实施方式中,在线路开口32内电镀时,电镀层5延伸至所述线路图形31的表面,从而与线路图形31共同形成所述第二金属层6。因此,通过电镀的方式实现所述线路图形31的增厚,有利于提升铜层的表面平整性,也有利于电镀层5与所述线路图形31的结合强度以及一体化。

73.本实施方式中,可以根据实际需要设计所述第二线路层4与所述第一线路层13是否导通,若需要导通,则可以使所述线路槽21贯穿所述绝缘层2设置,便可使得所述第二线路层4与所述第一线路层13实现电性连接。

74.步骤s17,请参阅图8,蚀刻所述第二金属层6形成第三线路层7。

75.本实施方式中,所述第三线路层7的线宽为30μm。所述第三线路层7的线距为30μm。

76.本实施方式中,所述第三线路层7通过改良半加成工艺(modified semi-additive process,msap)制作而成,具体通过压膜、曝光、显影、蚀刻、去膜等制程制作所述第三线路层7。msap流程的优势在于:线路厚度降低,线型容易控制,整个生产板的线条顶宽与底宽几乎一致,串扰低,信噪比高,信号完整性提高。而且,msap流程可以在3μm的铜层上制作线路,因此在制作完第二线路层4后,可以直接在线路图形31的基础上镀铜,进一步实现第三线路层7的制作。因此,通过et工艺制作的第二线路层4(即et线路)和通过msap工艺制作的第三线路层7(即msap线路)能够同时制作在绝缘层2上,避免传统增层工艺中需要通过层叠另一绝缘层和铜箔层并蚀刻铜箔层的方式才能制作另一线路层(即不同线路层之间还设有一绝缘层)的繁琐制程。如此,有利于简化流程,降低成本,且由于省略了一层绝缘层,有利于降低电路板的整体厚度。

77.本实施方式中,所述第二线路层4与所述第三线路层7可以根据实际需要做成导通或不导通的结构。如果需要所述第二线路层4与所述第三线路层7电性连接,则在制作第三线路层7时,沿所述电路基板20的厚度方向上,所述第二线路层4在所述第三线路层7上的投影部分位于所述第三线路层7的线路间隙内,使部分所述第三线路层7与所述第二线路层4重叠即可实现二者的电性连接。在这种情况下,无需单独采用盲孔的方式实现导通,制作流程更简单,提升了线路制作的效率,成本更低。

78.在另一实施方式中,如果第二线路层4无需与第三线路层7导通,可以在制作第三线路层7时,将第三线路层7形成于绝缘层2的表面且不与所述第二线路层4接触。此时,沿电路基板20的厚度方向上,所述第二线路层4在第三线路层7上的投影全部位于所述第三线路层7的线路间隙内。

79.步骤s18,对所述第三线路层7进行表面处理,从而得到所述电路板100。

80.本实施方式中,所述表面处理包括但不限于防焊处理以及焊接区域的化镀镍或化镀金。

81.本技术结合et工艺与msap工艺,能够同时制作在绝缘层2上,避免传统增层工艺中需要通过层叠另一绝缘层和铜箔层并蚀刻铜箔层的方式才能制作另一线路层(即不同线路层之间还设有一绝缘层)的繁琐制程。如此,有利于简化流程,降低成本,且由于省略了一层绝缘层,有利于降低电路板的整体厚度。

82.请参阅图8,本发明还提供了采用上述制造方法制造的电路板100,所述电路板100包括该电路基板20、绝缘层2、线路槽21、第二线路层4以及第三线路层7。所述电路基板20包括基层11以及设于所述基层11至少一表面的第一线路层13;所述绝缘层2设于所述第一线路层13的表面和所述第一线路层13的线路间隙;所述线路槽21开设于所述绝缘层2,所述线路槽21的开口22位于所述绝缘层2远离所述第一线路层13的表面;所述第二线路层4设于所述线路槽21内并由所述开口22露出;所述第三线路层7至少设于所述绝缘层2的表面。

83.本实施方式中,沿所述电路板100的厚度方向上,所述第二线路层4在所述第三线路层7上的投影部分或全部位于所述第三线路层7的线路间隙内。所述第二线路层4与所述第三线路层7可以根据实际需要做成导通或不导通的结构。如果需要所述第二线路层4与所述第三线路层7电性连接,则在制作第三线路层7时,使部分所述第三线路层7与所述第二线路层4重叠即可实现二者的电性连接,在这种情况下,无需单独采用盲孔的方式实现导通,制作流程更简单,提升了线路制作的效率,成本更低。

84.在另一实施方式中,如果第二线路层4无需与第三线路层7导通,可以在制作第三线路层7时,将第三线路层7只形成于绝缘层2的表面且不与所述第二线路层4接触,此时,沿电路板100的厚度方向,所述第二线路层4在第三线路层7上的投影全部位于所述第三线路层7的线路间隙。

85.本实施方式中,所述第二线路层4的线宽10μm,所述第二线路层4的线距为10μm。

86.本实施方式中,所述第三线路层7的线宽为30μm,所述第三线路层7的线距为30μm。

87.本实施方式中,沿所述电路板100的厚度方向上,所述线路槽21贯穿所述绝缘层2,所述第二线路层4与所述第一线路层13接触并电性连接。

88.综上所述,本发明提供的电路板的制造方法在同一绝缘层制作出内埋的第二线路层和位于绝缘层表面的第三线路层这两种线路,两线路层之间避免增加另一绝缘层,制作流程更简单,提升了电路板线路制作的效率,成本更低,有利于降低电路板的整体厚度,使电路板更轻薄。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1