具有梁结构的压电MEMS硅谐振器及其形成方法、电子设备

具有梁结构的压电mems硅谐振器及其形成方法、电子设备

技术领域

1.本发明涉及谐振器技术领域,具体涉及一种压电mems硅谐振器及其形成方法,以及一种电子设备。

背景技术:

2.谐振器利用了谐振频率可以被被测物理量改变的现象,具有重复性高、分辨率高、灵敏度高等优点。高品质因数的微机电系统(mems,micro

‑

electro

‑

mechanical system)谐振器已广泛应用于传感器、振荡器和执行器中,以获得较高的机械灵敏度。

3.mems工艺中器件的真空封装是整个工艺过程中的难点,通过封装形成一个稳定的真空环境,对于mems器件的可靠性和高品质因数是至关重要的。封装的质量决定着整个器件的质量和使用寿命,良好的封装能够使器件在后续工艺中和在器件使用过程中避免潜在污染物(如灰尘颗粒、水蒸气、气体分子)对真空度的破坏。因此能够长期维持mems器件真空度的封装技术是实现mems器件商业产品化的主要障碍。

4.目前,最常用的mems器件封装方法是在mems器件上键合帽的方法。在mems器件上键合帽的工艺可以通过多种方法来实现,主要包括玻璃与硅的阳极键合、玻璃与硅热压键合以及硅与硅通过中间金层的键合。作为中间层的键合材料,磷硅酸盐玻璃(psg)或玻璃粉,已被用于将玻璃键合到硅上,由于键合材料的应用可以在键合过程中将更多的拓扑结构覆盖。为了进一步提高键合的质量,可以在键合区域局部加热,优点包括:可以更好地控制键合温度和可以在键合区域获得比器件更高的温度,减轻对整个器件中温度敏感材料的热预算的担忧。采用多晶硅和金作为微加热器的局部加热技术的键合工艺已经被用于mems生产中。此外,吸气剂有时也被用于控制空腔内的压力,减少由于键合层和器件材料释放气体带来的影响。

5.尽管技术人员不断提高键合封装的质量,但由于键合界面层的致密度无法达到和硅基底致密度一样的量级,因而仍然不能在器件长期使用中完全避免键合层的漏气。另外,键合材料也会存在一定的释放气体的现象,即使存在吸气剂也无法完全解决气体释放问题。因此,采用现有封装工艺的器件在封装后内部不能有效保持真空度,这一难题依然是mems谐振器等需要在真空下工作的器件的瓶颈。由于现有技术谐振腔内真空度随着时间延长而降低使谐振器阻尼升高,谐振器的品质因数很难保持长期稳定性。因此,亟需开发出可靠的封装技术,实现长期有效地维持谐振腔内的高真空度,以提高谐振式传感器品质因数以及使用寿命。

技术实现要素:

6.有鉴于此,本发明提出一种低成本、高品质因数、高稳定性的具有梁结构的压电mems硅谐振器及其形成方法,以及包括该具有梁结构的压电mems硅谐振器的电子设备。

7.本发明第一方面一种具有梁结构的压电mems硅谐振器的形成方法,包括:提供带下空腔的soi硅片作为衬底,所述带下空腔的soi硅片中所述下空腔的上方具有器件硅层;

在所述衬底之上依次形成下电极、压电层和上电极;刻蚀所述器件硅层以形成所述梁结构,其中所述器件硅层作为所述梁结构的从动层;在当前半导体结构上形成牺牲层,所述牺牲层完全覆盖所述当前半导体结构;在所述牺牲层之上生长封装材料以形成薄膜封装层,然后在所述薄膜封装层中的所述梁结构区域上方位置刻蚀通孔;去除所述梁结构的振动区上方的所述牺牲层以形成上空腔,并且保留所述梁结构的固定端上方的所述牺牲层;再次生长所述封装材料以封闭所述通孔;形成贯穿所述薄膜封装层以及被保留的所述牺牲层的电连接通孔;在所述电连接通孔中形成电极连接。

8.可选地,所述梁结构为悬臂梁或者固支梁,或者包含所述悬臂梁或者所述固支梁的多梁结构。

9.可选地,所述从动层为掺杂单晶硅,且掺杂浓度大于等于10

19

cm

‑3。

10.可选地,所述器件硅层下方还具有绝缘层,所述方法还包括:刻蚀所述器件硅层以形成所述梁结构的同时刻蚀所述绝缘层,其中所述器件硅层和所述绝缘层均作为所述梁结构的从动层。

11.可选地,所述牺牲层为氧化硅、光刻胶或聚合物。

12.可选地,所述封装材料为单晶硅或多晶硅。

13.可选地,生长所述封装材料的方式为外延生长。

14.可选地,所述薄膜封装层的厚度为10至100微米,或者20至50微米。

15.可选地,所述牺牲层的厚度大于10微米。

16.可选地,当所述封装材料为多晶硅时,所述在所述薄膜封装层中的所述梁结构区域上方位置开通孔的步骤替换为如下步骤:通过电化学反应刻蚀所述多晶硅的薄膜封装层,以使其转变为多孔结构多晶硅的多孔薄膜封装层。

17.可选地,还包括:在所述提供带下空腔的soi硅片作为衬底的步骤之前,在所述下空腔内侧形成吸气层;或/和,在形成所述牺牲层的步骤之后、所述生长封装材料以形成薄膜封装层的步骤之前,在所述牺牲层之上形成吸气层。

18.可选地,所述压电层材料为氮化铝或者掺杂氮化铝。

19.本发明第二方面提出一种具有梁结构的压电mems硅谐振器,其通过本发明公开的形成方法制得。

20.本发明第三方面提出一种具有梁结构的压电mems硅谐振器,包括:衬底,所述衬底的顶部具有下空腔;位于所述衬底之上的梁结构,所述梁结构包括从下至上依次堆叠的从动层、下电极、压电层和上电极;支撑结构,所述支撑结构位于所述梁结构的固定端的上方;薄膜封装层,所述薄膜封装层覆盖所述梁结构和所述支撑结构,所述薄膜封装层与所述梁结构之间构成上空腔;以及电极连接,所述电极连接贯穿所述支撑结构和所述薄膜封装层。

21.可选地,所述梁结构为悬臂梁或者固支梁,或者包含所述悬臂梁或者所述固支梁的多梁结构。

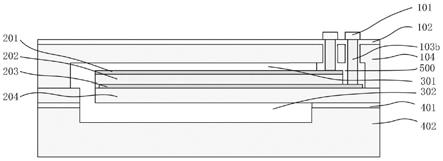

22.可选地,所述薄膜封装层的材料为单晶硅或多晶硅。

23.可选地,所述薄膜封装层的厚度为10至100微米,或者20至50微米。

24.可选地,所述上空腔的高度大于10微米。

25.可选地,还包括吸气层,所述吸气层位于所述上空腔和/或所述下空腔的内侧。

26.本发明第四方面提出一种电子设备,包括本发明公开的具有梁结构的压电mems硅

谐振器。

27.根据本发明的技术方案,基于压电mems硅谐振器(psr)谐振器,采用了硅薄膜封装技术。和传统的封装技术相比,由于不需要键合层,气密性更好,可实现更高的真空度(<1pa);同时避免了由于键合材料释放气体和键合界面漏气导致的真空度漂移。此外,在外延封装的制作步骤中需要高温加热,而本发明实例中用硅薄膜封装技术封装的psr全部采用耐高温材料,如氮化铝压电层,因此在制作上实现了工艺兼容,因此硅薄膜封装技术对于psr等耐高温的器件封装具有较大优势。

附图说明

28.为了说明而非限制的目的,现在将根据本发明的优选实施例、特别是参考附图来描述本发明,其中:

29.图1至图9为本发明实施方式的具有梁结构的压电mems硅谐振器的形成方法的过程示意图;

30.图10为本发明第一实施例的具有梁结构的压电mems硅谐振器的剖面示意图;

31.图11为本发明第二实施例的具有梁结构的压电mems硅谐振器的剖面示意图;

32.图12为本发明第三实施例的具有梁结构的压电mems硅谐振器的剖面示意图。

具体实施方式

33.目前在mems器件制备工程中采用的键合封装技术由于键合界面气密性不够好以及键合材料释放气体,导致器件中空腔的真空度难以长期维持,因而影响器件的品质因数和可靠性。鉴于现有技术存在的问题,本发明实施方式的具有梁结构的压电mems硅谐振器及其形成方法,核心为采用单晶硅外延并选择性刻蚀的方法制作谐振器的梁结构,并在单晶硅之上沉积压电薄膜形成谐振器。本发明的技术方案通过外延薄层硅并去除牺牲材料的方式实现封装,避免了键合界面和键合材料的存在,同时外延界面的气密性远高于键合界面,因而可实现在更长时间内维持空腔的高真空度。本发明的技术方案具有简便易行,制作的器件具有低成本、高品质因数、高稳定性等优势。

34.为使技术人员更好地理解,先对说明书附图中各部分结构及材料加以说明:

35.100:封装结构,包括:

36.101:金属连接区,具体材料可选钼、钌、金、铝、镁、钨、铜,钛、铱、锇、铬或以上金属的复合或其合金。

37.102:电学隔离层,具体材料可选氧化硅、氮化铝或氧化铝等。

38.103b:金属化连接,具体材料同101。

39.104:薄膜封装层,材料可选单晶硅或多晶硅。

40.200:梁结构。需要说明的是,梁结构具体可以为悬臂梁或者固支梁,或者包含悬臂梁或者固支梁的多梁结构,例如:由两个悬臂梁组合而成的音叉型结构,或者由多个悬臂梁组合而成的梳齿状结构。为了简便说明,本发明附图中采用悬臂梁,但这仅是出于示例并非限定。梁结构200包括:

41.201:上电极,材料同101。

42.202:压电层,可选氮化铝、氧化锌、pzt等材料并包含上述材料的一定原子比的稀

土元素掺杂材料。压电层材料优选氮化铝及掺杂氮化铝,因为氮化铝的热兼容性极好,即使在1100摄氏度以上的高温下(如外延生长单晶硅或多晶硅时需要高温1000度左右)依然能够保持器压电特性不退化。

43.203:下电极,材料同101。

44.204:从动层,材料可选单晶硅、氮化铝、砷化镓或蓝宝石等等。

45.该从动层可以由soi型基底中的器件硅层加工得到。

46.300:空腔,包括:上空腔301和下空腔302。

47.400:衬底,包括:

48.401:绝缘层,一般为二氧化硅。

49.402:背衬底,材料同104。

50.500:牺牲层,材料可以为氧化硅、光刻胶、聚合物材料等。

51.下面结合附图对本发明作更进一步的说明。如图1至图9所示,本发明实施方式的具有梁结构的压电mems硅谐振器的形成方法主要包括如下9个步骤。

52.步骤1:提供衬底。

53.具体地,如图1所示,可以直接提供带下空腔的soi硅片作为衬底,该衬底包括硅材料的背衬底402、二氧化硅材料的绝缘层401、下空腔302以及硅材料的器件硅层204。在实现中也可以不用带空腔的soi硅片,而是通过下面的方式逐步制作衬底:提供硅基底;在硅基底的顶表面形成绝缘层;在当前半导体结构顶部刻蚀凹槽;向凹槽中填充牺牲层;在当前半导体结构之上形成硅材料的器件硅层;去除牺牲层以形成下空腔;将当前半导体结构作为衬底。

54.步骤2:依次沉积下电极、主动层和上电极。

55.具体地,如图2所示,先在衬底上沉积钼,随后以图形化的光刻胶作为掩膜刻蚀钼电极使其图形化,得到下电极203。再沉积一层氮化铝压电层,在氮化铝上沉积氧化硅,随后以光刻胶为掩膜对氧化硅进行湿法刻蚀,然后以氧化硅作为硬掩模对氮化铝进行干法刻蚀使其图形化,得到压电层202。参考下电极的制作过程,制作出上电极201。

56.步骤3:刻蚀器件硅层以形成梁结构。

57.具体地,如图3所示在前一步骤得到的结构上沉积一层氧化硅,之后以光刻胶为掩膜,以hf为刻蚀剂刻蚀氧化硅;然后以图形化了的氧化硅为硬掩模,用干法刻蚀硅直至soi的器件硅层204和绝缘层401被刻穿,以释放梁结构。此时,器件硅层204转变为从动层204。然后,可选地,用boe去除从动层204底下的绝缘层401。若保留绝缘层401,则该绝缘层可以用于温度补偿。

58.步骤4:形成牺牲层。

59.具体地,如图4所示,在前一步骤得到的结构上生长氧化硅材料的牺牲层500,该牺牲层500完全覆盖图3结构。牺牲层500顶部可高于上电极201上表面10微米以上(根据需要可调节,要求大于梁结构的振幅),随后对氧化硅进行图形化。特别地,牺牲层500材料还可以是光刻胶、聚合物材料等。

60.步骤5:在牺牲层之上生长封装材料以形成薄膜封装层,然后在薄膜封装层中的梁结构区域上方位置刻蚀通孔。

61.具体地,如图5所示,先在前一步骤得到的结构上生长多晶硅材料以形成薄膜封装

层104,然后在薄膜封装层104中的梁结构区域上方位置,也即在上空腔区域上方位置,刻蚀多个通孔。薄膜封装层104的厚度约10至100微米,优选为20至50微米。若薄膜封装层104太薄则无法长期保证封装真空度。可选地,生长封装材料的方式具体可以为外延生长。可选地,当封装材料为多晶硅时,形成通孔步骤可以通过刻蚀的方式之外,还可以通过电化学反应刻蚀多晶硅的薄膜封装层104,以使其转变为多孔结构多晶硅的多孔薄膜封装层104。

62.步骤6:去除局部的牺牲层。

63.具体地,如图6所示,去除梁结构的振动区上方的牺牲层以形成上空腔,并且保留梁结构的固定端上方的牺牲层。可以用hf蒸汽或溶液通过多晶硅薄膜封装层104上的通孔刻蚀掉下方的氧化硅材料的牺牲层500,得到上空腔301,同时梁结构右侧需留有部分氧化硅以保证后续电连接中不至于使两电极短路。因此,在步骤5中通孔不可太靠右侧。特别地,这里去除牺牲层的方法根据步骤5中沉积牺牲层500的材料类型不同而易;若为光刻胶则用显影液或用nmp等办法去除,若为聚合物可选择加热分解等方式去除,若为其他材料则选用相应方法。

64.步骤7:再次生长封装材料以封闭通孔。

65.首先,如图7所示,通高温的氢气和氯气清洗空腔,然后在真空环境下继续外延多晶硅,使通孔完全覆盖住。

66.步骤8:形成电连接通孔。

67.具体地,如图8所示,首先沉积一层氮化铝,分别在上下电极连接处上方图形化氮化铝材料的电学隔离层102,然后以氮化铝为掩膜干法刻蚀多晶硅,接着用干法刻蚀氧化硅至钼电极;对连接孔进行氧化,防止后续电连接通过多晶硅短路。电连接通孔贯穿薄膜封装层以及被保留的牺牲层。

68.步骤9:形成电极连接。

69.具体地,如图9所示,首先沉积金属铜至填满电连接通孔,之后用铜刻蚀液去除薄膜封装层上的铜,只保留电连接通孔内部的铜;最后沉积金并进行图形化,得到金属连接区101和金属化连接103b。

70.本发明实施方式的具有梁结构的压电mems硅谐振器的形成方法中,还可以包括如下步骤:在提供带下空腔的soi硅片作为衬底的步骤之前,在下空腔内侧形成吸气层;或/和,在形成牺牲层的步骤之后、生长封装材料以形成薄膜封装层的步骤之前,在牺牲层之上形成吸气层。这样可以使得最终得到的具有梁结构的压电mems硅谐振器的上空腔和或/和下空腔中具有吸气层,能够更好地维持空腔内的真空度。

71.本发明实施方式的具有梁结构的压电mems硅谐振器的形成方法中,从动层可以为掺杂单晶硅,且掺杂浓度大于等于10

19

cm

‑3。其中掺杂方式可以为:(1)在单晶生长过程中掺杂,如直拉法(cz)将掺杂元素掺入多晶硅原料,之后用掺杂好的单晶硅制作soi型衬底;(2)采用高温扩散的办法使掺杂剂扩散进入soi的顶部硅材料,或用扩散掺杂的硅片制作soi;(3)采用离子注入的方法对soi的顶部硅材料进行掺杂。通过控制掺杂浓度可以实现对梁结构等效温度系数的调节,从而消除或者降低器件的温漂效应,有利于器件避免因温度变化带来误差问题,能够提高器件的可靠性。

72.本发明实施方式的具有梁结构的压电mems硅谐振器的形成方法中,还可以省略“去除从动层下方的绝缘层”的步骤。换言之,保留从动层下的绝缘层。该实施例中保留下来

的绝缘层401也可以用作梁结构200的温度补偿层来改善器件的温漂问题。需要说明的是,若采用sio2等材料作为温度补偿材料,还可以将温度补偿层设置在上电极表面、上电极与压电主动层之间、压电主动层与下电极之间、下电极与从动层之间或在以上界面中的两个或多个界面中。

73.本发明实施方式的具有梁结构的压电mems硅谐振器,可以通过本发明的具有梁结构的压电mems硅谐振器的形成方法制得。

74.本发明实施方式的具有梁结构的压电mems硅谐振器,包括:衬底,衬底的顶部具有下空腔;位于衬底之上的梁结构,梁结构包括从下至上依次堆叠的从动层、下电极、压电层和上电极;支撑结构,支撑结构位于梁结构的固定端的上方;薄膜封装层,薄膜封装层覆盖梁结构和支撑结构,薄膜封装层与梁结构之间构成上空腔;以及电极连接,该电极连接贯穿支撑结构和薄膜封装层。其中,薄膜封装层的材料可以为单晶硅或多晶硅。薄膜封装层的厚度可以为10至100微米,或者20至50微米。上空腔的高度可以大于10微米。此外,谐振器中还可以包括吸气剂,吸气剂位于上空腔和/或下空腔的内部。吸气剂的材料可以为钛(ti)以及钛合金,锆(zr)以及锆合金。

75.根据本发明实施方式的具有梁结构的压电mems硅谐振器,梁结构为悬臂梁或者固支梁,或者包含悬臂梁或者固支梁的多梁结构。

76.本发明第一实施例的具有梁结构的压电mems硅谐振器如图10所示。该谐振器中,由封装结构100和衬底400围出空腔300,包括上空腔301和下空腔302。空腔300的作用是为梁结构的振动提供一定的活动空间,空腔300中需保持较高的真空度以减小梁振动的阻尼。其中上空腔301由生长外延薄膜封装层后去除牺牲材料产生,下空腔302由基底硅材料顶部的刻蚀形成,或直接采用带空腔的soi硅片。封装结构100上存在电连接通孔,即在孔结构中沉积金属实现梁结构200的上下电极与外电路的连通。在沉积金属前,通孔及薄膜封装层的表面被氧化以形成隔离层102,用于防止两个电极之间短路。梁结构200位于封装结构100和衬底400之间的空腔中,由上至下依次为:上电极201、压电层202、下电极203和从动层204。梁结构200左端为自由端,右端为固定端。支撑结构500位于梁结构200的固定端的上方。

77.本发明第二实施例的具有梁结构的压电mems硅谐振器如图11所示。如图11,该实施例与图10所示实施例的区别在于其从动层204为掺杂单晶硅,且掺杂浓度大于等于10

19

cm

‑3。通过控制掺杂浓度可以实现对梁结构等效温度系数的调节,从而克服或者降低器件的温漂效应,有利于器件避免因温度变化带来误差问题,提高器件的可靠性。

78.本发明第三实施例的具有梁结构的压电mems硅谐振器如图12所示。如图12,该实施例与图10所示实施例的区别保留了从动层402下的绝缘层401。绝缘层401也可以用作梁结构200的温度补偿层,改善器件的温漂问题。

79.本发明实施方式的电子设备,包括本发明实施方式的具有梁结构的压电mems硅谐振器。

80.根据本发明的技术方案,基于压电mems硅谐振器(psr)谐振器,采用了硅薄膜封装技术。和传统的封装技术相比,由于不需要键合层,气密性更好,可实现更高的真空度(<1pa);同时避免了由于键合材料释放气体和键合界面漏气导致的真空度漂移。此外,在外延封装的制作步骤中需要高温加热,而本发明实例中用硅薄膜封装技术封装的psr全部采用耐高温材料,如氮化铝压电层,因此在制作上实现了工艺兼容,因此硅薄膜封装技术对于

psr等耐高温的器件封装具有较大优势。

81.上述具体实施方式,并不构成对本发明保护范围的限制。本领域技术人员应该明白的是,取决于设计要求和其他因素,可以发生各种各样的修改、组合、子组合和替代。任何在本发明的精神和原则之内所作的修改、等同替换和改进等,均应包含在本发明保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1