信号生成电路、使用其的半导体装置及信号生成方法与流程

信号生成电路、使用其的半导体装置及信号生成方法

1.相关申请的交叉引用

2.本技术要求于2020年9月22日向韩国知识产权局提交的韩国专利申请10-2020-0121949的优先权,其全部内容通过引用完全合并于此。

技术领域

3.各个实施例一般地涉及集成电路技术,更具体地,涉及信号生成电路和使用该信号生成电路的半导体装置。

背景技术:

4.电子设备可以包括许多电子组件。在电子组件当中,计算机系统可以包括许多由半导体组成的半导体装置。构成计算机系统的半导体装置可以在发送和接收时钟信号和数据时相互通信。可以通过对系统时钟信号进行缓冲或分频来生成具有各种相位的内部时钟信号。然而,取决于电路特性,在经缓冲的时钟信号或经分频的时钟信号之间可能发生相位偏斜和/或占空比失真。通常,半导体装置可以包括占空比校正电路,用于校正这种相位偏斜和/或占空比失真。通用占空比校正电路可以将多个时钟信号中的任何一个设置为参考时钟信号,并且可以调节在其他时钟信号和参考时钟信号之间的相位差,从而补偿相位偏斜和/或占空比失真。

技术实现要素:

5.在一个实施例中,信号生成电路可以包括第一延迟电路、第二延迟电路和占空比控制电路。第一延迟电路可以被配置为通过基于第一延迟控制信号来延迟第一输入信号而生成第一输出信号。第二延迟电路可以被配置为通过基于第二延迟控制信号来延迟第二输入信号而生成第二输出信号。占空比控制电路可以被配置为比较第一输出信号和第二输出信号的相位并改变第二延迟控制信号的值。然后,占空比控制电路可以将第一和第二延迟控制信号的值减小相同的值。

6.在一个实施例中,信号生成方法可以包括通过分别将第一输入信号和第二输入信号延迟第一时间来生成第一输出信号和第二输出信号。信号生成方法可以包括:比较第一输出信号和第二输出信号的相位;以及将第二输入信号被延迟的时间改变为第二时间。另外,信号生成方法可以包括将第一时间和第二时间减小相同的时间。

7.在一个实施例中,信号生成电路可以包括第一延迟电路、第二延迟电路和占空比控制电路。第一延迟电路可以被配置为通过延迟第一输入信号来生而第一输出信号,并且第二延迟电路可以被配置为通过延迟第二输入信号来生成第二输出信号。占空比控制电路可以被配置为改变第二延迟电路的延迟时间,直到第一输出信号与第二输出信号之间的相位差达到目标值为止。然后,占空比控制电路可以将第一延迟电路和第二延迟电路的延迟时间减小相同的时间。

8.在一个实施例中,信号生成电路可以包括四个延迟电路和占空比控制电路。第一

延迟电路可以被配置为通过将第一输入时钟信号延迟参考延迟时间来生成第一相位时钟信号,第二延迟电路可以被配置为通过将第二输入时钟信号延迟第一可变延迟时间来生成第二相位时钟信号。第三延迟电路可以被配置为通过将第三输入时钟信号延迟第二可变延迟时间来生成第三相位时钟信号,并且第四延迟电路可以被配置为通过将第四输入时钟信号延迟第三可变延迟时间来生成第四相位时钟信号。占空比控制电路可以被配置为基于第一至第四相位时钟信号之间的相位差来改变第一至第三可变延迟时间,然后可以将参考延迟时间和第一至第三可变延迟时间减小相同的时间。

9.在一个实施例中,半导体装置可以包括时钟分频器、第一占空比校正电路和延迟锁定环电路。时钟分频器可以被配置为通过对输入时钟信号进行分频来生成第一分频时钟信号和第二分频时钟信号。第一占空比校正电路可以被配置为通过延迟第一和第二分频时钟信号来生成第一参考时钟信号和第二参考时钟信号,可以比较第一参考时钟信号和第二参考时钟信号的相位以调节第二分频时钟信号被延迟时间,然后可以将第一和第二分频时钟信号被延迟的时间减小相同的时间。延迟锁定环电路可以被配置为比较第一参考时钟信号和反馈时钟信号的相位,并通过延迟第一参考时钟信号和第二参考时钟信号来生成一个或多个输出时钟信号。然后,延迟锁定环电路可以通过延迟一个或多个输出时钟信号来生成反馈时钟信号。

10.在一个实施例中,半导体装置可以包括延迟锁定环电路、时钟分频器和占空比校正电路。延迟锁定环电路可以被配置为将参考时钟信号的相位与通过延迟第一输出时钟信号而生成的反馈时钟信号的相位进行比较,以及通过可变地延迟参考时钟信号来生成延迟时钟信号。时钟分频器可以被配置为通过对延迟时钟信号进行分频来至少生成第一分频时钟信号和第二分频时钟信号。占空比校正电路可以被配置为通过延迟第一和第二分频时钟信号来生成第一输出时钟信号和第二输出时钟信号,并且可以比较第一输出时钟信号和第二输出时钟信号的相位以调节第二输出时钟信号被延迟的时间。然后,占空比校正电路可以将第一输出时钟信号和第二输出时钟信号被延迟的时间减小相同的时间。

11.在一个实施例中,半导体装置可以包括延迟锁定环电路、多相时钟生成电路、时钟分配网络和占空比校正电路。延迟锁定环电路可以被配置为通过延迟参考时钟信号来生成延迟时钟信号,并且可以将参考时钟信号的相位与通过延迟所述延迟时钟信号而生成的反馈时钟信号的相位进行比较。延迟锁定环电路还可改变参考时钟信号被延迟的时间。多相时钟生成电路可以被配置为通过对延迟时钟信号的频率进行分频来至少生成第一输出时钟信号和第二输出时钟信号。时钟分配网络可以被配置为驱动第一和第二输出时钟信号并输出第一分配时钟信号和第二分配时钟信号。占空比校正电路可以被配置为通过延迟第一分配时钟信号和第二分配时钟信号来生成第一传输时钟信号和第二传输时钟信号,并且可以比较第一传输时钟信号和第二传输时钟信号的相位以调节第二分配时钟信号被延迟的时间。然后,占空比校正电路可以将第一和第二分配时钟信号所延迟的时间减小的相同的时间。

附图说明

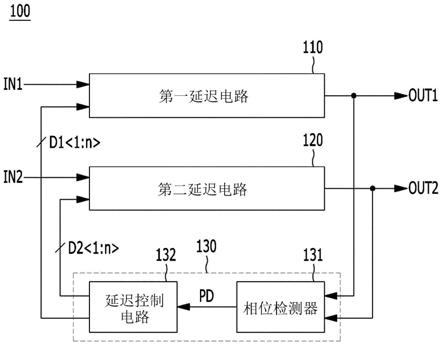

12.图1是示出根据实施例的信号生成电路的配置的框图。

13.图2是示出图1中所示的第一和第二延迟电路的配置的图。

14.图3是示出图1中所示的延迟控制电路的配置的框图。

15.图4是示出根据本实施例的信号生成电路的操作的框图。

16.图5是示出根据实施例的信号生成电路的配置的框图。

17.图6是示出图5中所示的延迟控制电路的配置的框图。

18.图7是示出根据实施例的半导体装置的配置的框图。

19.图8是示出图7中所示的延迟模型电路的配置的图。

20.图9是示出根据实施例的半导体装置的操作的框图。

21.图10是示出根据实施例的半导体装置的操作的框图。

22.图11是示出根据实施例的半导体装置的操作的框图。

具体实施方式

23.图1是示出根据实施例的信号生成电路100的配置的框图。信号生成电路100可以接收第一输入信号in1和第二输入信号in2,并且生成第一输出信号out1和第二输出信号out2。信号生成电路100可以通过延迟第一输入信号in1来生成第一输出信号out1,并且可以通过延迟第二输入信号in2来生成第二输出信号out2。信号生成电路100可以对第一输出信号out1和第二输出信号out2执行相位和/或占空比校正操作。信号生成电路100可以基于第一输出信号out1和第二输出信号out2的相位来改变第二输入信号in2被延迟的时间。信号生成电路100可以改变第二输入信号in2被延迟的时间,然后将第一输入信号in1和第二输入信号in2被延迟的时间减小相同的时间。信号生成电路100可以将第一输入信号in1和第二输入信号in2被延迟的时间减小在第一输入信号in1和第二输入信号in2被延迟的时间当中较短的时间量。因此,信号发生电路100将第一输入信号in1和第二输入信号in2所延迟的延迟时间可以被设置为最小值。

24.信号生成电路100可以包括第一延迟电路110、第二延迟电路120和占空比控制电路130。第一延迟电路110可以接收第一输入信号in1,并且通过延迟第一输入信号in1来生成第一输出信号out1。第二延迟电路120可以接收第二输入信号in2,并且通过延迟第二输入信号in2来生成第二输出信号out2。第一和第二延迟电路110和120可以是可变延迟电路,其中第一延迟电路110可以接收第一延迟控制信号d1《1:n》,并且可以具有根据第一延迟控制信号d1《1:n》而改变的延迟时间。这里,n可以是等于或大于2的整数。第二延迟电路120可以接收第二延迟控制信号d2《1:n》,并且可以具有根据第二延迟控制信号d2《1:n》改变的延迟时间。第一和第二延迟电路110和120可以是数字延迟电路。第一和第二延迟控制信号d1《1:n》和d2《1:n》可以是数字信号,其每个包括多个位。在一个实施例中,第一和第二延迟电路110和120可以是模拟延迟电路。第一和第二延迟控制信号d1《1:n》和d2《1:n》可以是具有各种电压电平的模拟信号。以下描述将基于以下假设:第一和第二延迟控制信号d1《1:n》和d2《1:n》是数字信号,并且第一和第二延迟电路110和120是其延迟量分别基于第一和第二延迟控制信号d1《1:n》和d2《1:n》来调节的数字延迟线。

25.占空比控制电路130可以接收第一输出信号out1和第二输出信号out2。占空比控制电路130可以比较第一输出信号out1和第二输出信号out2的相位。占空比控制电路130可以比较第一和第二输出信号out1和out2的相位,并可以改变第一和第二延迟电路110和120的延迟时间。为了改变第一和第二延迟电路110和120的延迟时间,占空比控制电路130可以

比较第一输出信号out1和第二输出信号out2的相位,并可以改变第一延迟控制信号d1《1:n》和第二延迟控制信号d2《1:n》的逻辑值。占空比控制电路130可以改变第二延迟控制信号d2《1:n》的值,直到在第一输出信号out1和第二输出信号out2之间的相位差达到可以随意设置的目标值为止。例如,当第一输入信号in1和第二输入信号in2是时钟信号时,目标值可以相应于第一输入信号in1或第二输入信号in2的1/4周期。在改变第二延迟控制信号d2《1:n》的值之后,占空比控制电路130可以将第一延迟控制信号d1《1:n》和第二延迟控制信号d2《1:n》的值减小相同的值。在一个实施例中,占空比控制电路130可以将第一和第二延迟控制信号d1《1:n》和d2《1:n》的逻辑值减小在第一和第二延迟控制信号d1《1:n》和d2《1:n》当中具有较小值的延迟控制信号的逻辑值。即,可以将第一和第二延迟控制信号d1《1:n》和d2《1:n》的逻辑值进行比较,并且可以将第一和第二延迟控制信号d1《1:n》和d2《1:n》的较小逻辑值利用来减小第一和第二延迟控制信号d1《1:n》和d2《1:n》的每个逻辑值。占空比控制电路130可以顺序地减小第一和第二延迟控制信号d1《1:n》和d2《1:n》的逻辑值,直到第一和第二延迟控制信号d1《1:n》和d2《1:n》中的任何一个的逻辑值被最小化为止。

26.在初始状态下,第一和第二延迟控制信号d1《1:n》和d2《1:n》可以各自具有默认值。因此,第一延迟电路110和第二延迟电路120可以将具有默认值的第一延迟控制信号d1《1:n》和第二延迟控制信号d2《1:n》延迟参考延迟时间。当第一输出信号out1和第二输出信号out2之间的相位差大于或小于目标值时,占空比控制电路130可以增大或减小第二延迟控制信号d2《1:n》的逻辑值。第二延迟电路120可以基于具有增大或减小的逻辑值的第二延迟控制信号d2《1:n》来改变延迟第二输入信号in2的延迟时间。当第一输出信号out1和第二输出信号out2之间的相位差等于目标值时,占空比控制电路130可以将第一延迟控制信号d1《1:n》和第二延迟控制信号d2《1:n》的逻辑值减小相同的值。第一延迟电路110和第二延迟电路120的延迟时间可以减小相同的时间。占空比控制电路130可以通过控制第一输出信号out1和第二输出信号out2具有与目标值相应的相位差来调节第一输出信号out1和第二输出信号out2的占空比。由于可以将用于调节占空比的第一延迟电路110和第二延迟电路120的延迟时间设置为最小值,因此可以提高信号生成电路100的运行特性和速度。

27.占空比控制电路130可以包括相位检测器131和延迟控制电路132。相位检测器131可以接收第一输出信号out1和第二输出信号out2。相位检测器131还可以通过比较第一输出信号out1和第二输出信号out2的相位来生成相位检测信号pd。相位检测器131可以采用任何公知的相位检测器和/或占空比检测器的配置,并且可以取决于第一输出信号out1和第二输出信号out2之间的相位差是大于还是小于目标值而生成具有不同逻辑电平的相位检测信号pd。例如,具有第一逻辑电平的相位检测信号pd可以增加由占空比控制电路130生成的第二延迟控制信号d2《1:n》的逻辑值,从而增加第二延迟电路120的延迟时间。具有第二逻辑电平的相位检测信号pd可以减小由占空比控制电路130生成的第二延迟控制信号d2《1:n》的逻辑值,从而减小第二延迟电路120的延迟时间。

28.延迟控制电路132可以基于相位检测信号pd来生成第一和第二延迟控制信号d1《1:n》和d2《1:n》。延迟控制电路132可以在初始状态下输出具有默认值的第一和第二延迟控制信号d1《1:n》和d2《1:n》。基于具有默认值的第一延迟控制信号d1《1:n》和第二延迟控制信号d2《1:n》,第一延迟电路110和第二延迟电路120可以分别将第一输入信号in1和第二输入信号in2延迟参考延迟时间。基于相位检测信号pd,延迟控制电路132可以改变第二延迟

控制信号d2《1:n》的逻辑值,直到在第一输出信号out1和第二输出信号out2之间的相位差等于目标值为止。在第一输出信号out1和第二输出信号out2之间的相位差等于目标值之后,延迟控制电路132可以将第一延迟控制信号d1《1:n》和第二延迟控制信号d2《1:n》的逻辑值减小相同的值。

29.图2是示出图1中所示的第一延迟电路110和第二延迟电路120的配置的图。参照图2,第一延迟电路110可以包括第一延迟器211、第一驱动器组221、第二驱动器组222和第一输出反相器231。第一延迟器211可以具有与第一延迟电路110可以具有的最大延迟时间相等的延迟量。基于第一延迟控制信号d1《1:n》,第一延迟电路110可以改变第一和第二驱动器组221和222的权重,并因此改变第一输入信号in1被延迟的时间。

30.第一驱动器组221和第二驱动器组222中的每个可以接收第一延迟控制信号d1《1:n》。

31.第一驱动器组221可以接收第一输入信号in1。基于第一延迟控制信号d1《1:n》,第一驱动器组221可以以可变的可驱动性来使得第一输入信号in1反相。可以基于第一延迟控制信号的反相信号d1b《1:n》来改变第一驱动器组221的可驱动性。第一驱动器组221可以包括与第一延迟控制信号d1《1:n》的各个位相对应的多个反相器。即,第一驱动器组221可以包括n个反相器,其中,每个反相器可以接收第一延迟控制信号d1《1:n》的一个比特位。例如,随着第一延迟控制信号d1《1:n》的比特位当中具有低逻辑电平的比特位的数目增加,第一驱动器组221的可驱动性可以增加,并且第一延迟时间电路110的延迟时间可以被缩短。

32.第二驱动器组222可以接收第一延迟器211的输出。基于第一延迟控制信号d1《1:n》,第二驱动器组222可以以可变的可驱动性来使得第一延迟器211的输出反相。可以基于第一延迟控制信号d1《1:n》来改变第二驱动器组222的可驱动性。第二驱动器组222可以包括与第一延迟控制信号d1《1:n》的各个比特位相对应的多个反相器。反相器可各自接收第一延迟控制信号d1《1:n》的一个比特位。例如,随着第一延迟控制信号d1《1:n》的比特位当中具有高逻辑电平的比特位的数量增加,第二驱动器组222的可驱动性可以增加。因此,第一延迟电路110的延迟时间可以被延长。

33.第一输出反相器231可以共同耦接到第一和第二驱动器组221和222,并且可以接收第一和第二驱动器组221和222的输出。第一输出反相器231可以通过将第一和第二驱动器组221和222的输出反相来生成第一输出信号out1。通过将第一和第二驱动器组221和222的、根据基于第一延迟控制信号d决定的权重而生成的输出的相位进行混合,第一输出反相器231可以生成第一输出信号out11《1:n》。

34.第二延迟电路120可以包括第二延迟器212、第三驱动器组223、第四驱动器组224和第二输出反相器232。第二延迟器212可以具有与第二延迟电路120可以具有的最大延迟时间相应的延迟量。第二延迟器212的延迟量可以基本上等于第一延迟器211的延迟量。基于第二延迟控制信号d2《1:n》,第二延迟电路120可以改变第三驱动器组223和第四驱动器组224的权重,从而改变第二输入信号in2被延迟的时间。第三驱动器组223和第四驱动器组224中的每个可以接收第二延迟控制信号d2《1:n》。

35.第三驱动器组223可以接收第二输入信号in2。基于第二延迟控制信号d2《1:n》,第三驱动器组223可以以可变的可驱动性来使得第二输入信号in2反相。可以基于第二延迟控制信号的反相信号d2b《1:n》来改变第三驱动器组223的可驱动性。第三驱动器组223可以包

括与第二延迟控制信号d2《1:n》的各个比特位相对应的多个反相器,其中,每个反相器都可以接收第二延迟控制信号d2《1:n》的一个比特位。例如,随着第二延迟控制信号d2《1:n》的比特位当中具有低逻辑电平的比特位的数目增加,第三驱动器组223的可驱动性可以增加,使得第二延迟电路120的延迟时间可以被缩短。

36.第四驱动器组224可以接收第二延迟器212的输出。基于第二延迟器控制信号d2《1:n》,第四驱动器组224可以以可变的可驱动性来使得第二延迟器212的输出反相。基于第二延迟控制信号d2《1:n》,可以改变第四驱动器组224的可驱动性。第四驱动器组224可以包括与第二延迟控制信号d2《1:n》的各个比特位相对应的多个反相器,其中,每个反相器都可以接收第二延迟控制信号d2《1:n》的一个比特位。例如,随着第二延迟控制信号d2《1:n》的比特位当中具有高逻辑电平的比特位的数量增加,第四驱动器组224的可驱动性可以增加。因此,第二延迟电路120的延迟时间可以被延长。

37.第二输出反相器232可以共同耦接到第三和第四驱动器组223和224,并且可以接收第三和第四驱动器组223和224的输出。通过使得第三和第四驱动器组223和224的输出反相,第二输出反相器232可以生成第二输出信号out2。第二输出反相器232可通过将第三和第四驱动器组223和224的、根据基于第二延迟控制信号d2的逻辑值确定的权重而生成的输出的相位进行混合来生成第二输出信号out2。

38.图3是示出图1中所示的延迟控制电路132的配置的框图。参照图3,延迟控制电路132可以包括第一相位锁定检测器310、第二相位锁定检测器320和延迟控制信号生成电路330。基于相位检测信号pd,第一相位锁定检测器310可以生成第一相位锁定信号pl1。第一相位锁定检测器310可以检测相位检测信号pd的逻辑电平的变化,并且可以使能第一相位锁定信号pl1。当先前接收的相位检测信号pd处于第一逻辑电平并且当前接收的相位检测信号pd处于第二逻辑电平时,第一相位锁定检测器310可以使能第一相位锁定信号pl1。例如,具有第一逻辑电平的相位检测信号pd可以增加第二延迟控制信号d2《1:n》的逻辑值,并且可以增加第二延迟电路120的延迟时间。具有第二逻辑电平的相位检测信号pd可以减小第二延迟控制信号d2《1:n》的逻辑值,并且可以减小第二延迟电路120的延迟时间。

39.第一相位锁定检测器310可以包括第一触发器311和第二触发器312,其中第一触发器311可以具有被配置为接收电源电压vdd的输入端子d和被配置为接收相位检测信号pd的时钟端子。电源电压vdd可以具有可以被确定为高逻辑电平的电压电平。第二触发器312可以具有耦接到第一触发器311的输出端子q的输入端子d,并且可以被配置为接收从第一触发器311输出的信号。第二触发器312可以具有被配置为接收相位检测信号pd的反相信号的时钟端子,以及被配置为输出第一相位锁定信号pl1的输出端子q。当先前接收的相位检测信号pd具有高逻辑电平并且当前接收的相位检测信号pd具有低逻辑电平时,第一触发器311和第二触发器312可以输出电源电压vdd作为第一相位锁定信号pl1,以将第一相位锁定信号pl1使能为高逻辑电平。

40.基于第一延迟控制信号d1《1:n》和第二延迟控制信号d2《1:n》,第二相位锁定检测器320可以生成第二相位锁定信号pl2。基于第一和第二延迟控制信号d1《1:n》和d2《1:n》的至少一些比特位,第二相位锁定检测器320可以生成第二相位锁定信号pl2。例如,第二相位锁定检测器320可以接收第一和第二延迟控制信号d1《1:n》和d2《1:n》的最低有效位,并检测最低有效位的逻辑电平并使能第二相位锁定信号pl2。当第一和第二延迟控制信号d1《1:

n》和d2《1:n》的最低有效位中的任何一个变为低逻辑电平时,第二相位锁定检测器320可以使能第二相位锁定信号pl2。随着第一延迟控制信号d1《1:n》的比特位中具有低逻辑电平的比特位的数量增加,第一延迟电路110可以具有短的延迟时间。因此,当第一延迟控制信号d1《1:n》的最低有效位具有低逻辑电平时,第一延迟控制信号d1《1:n》可以具有最小值,并且第二相位锁定检测器320可以检测到第一延迟电路110的延迟时间被设置为最小值。类似地,随着第二延迟控制信号d2《1:n》的比特位中具有低逻辑电平的比特位的数量增加,第二延迟电路120可以具有短的延迟时间。因此,当第二延迟控制信号d2《1:n》的最低有效位具有逻辑低电平时,第二延迟控制信号d2《1:n》可以具有最小值,并且第二相位锁定检测器320可以检测到第二延迟电路120的延迟时间被设置为最小值。因此,当第一延迟电路110和第二延迟电路120中的任何一个具有最小延迟时间时,第二相位锁定检测器320可以使能第二相位锁定信号pl2。

41.第二相位锁定检测器320可以包括“与非”门321,其中“与非”门321可以接收第一和第二延迟控制信号d1《1:n》和d2《1:n》的最低有效位,以及输出第二相位锁定信号pl2。当第一延迟控制信号d1《1:n》和第二延迟控制信号d2《1:n》的最低有效位中的任何一个转变为低逻辑电平时,“与非”门321可以将第二相位锁定信号pl2使能为高逻辑电平。

42.延迟控制信号生成电路330可以接收相位检测信号pd、第一相位锁定信号pl1和第二相位锁定信号pl2,并且可以生成第一延迟控制信号d1《1:n》和第二延迟控制信号d2《1:n》。延迟控制信号生成电路330可以在初始状态下输出具有默认值的第一和第二延迟控制信号d1《1:n》和d2《1:n》。可以将默认值存储在延迟控制信号生成电路330中,并且延迟控制信号生成电路330可以基于相位检测信号pd来改变第二延迟控制信号d2《1:n》的逻辑值,直到第一相位锁定信号pl1被使能。例如,当相位检测信号pd处于高逻辑电平时,延迟控制信号生成电路330可以增加第二延迟控制信号d2《1:n》的逻辑值。当相位检测信号pd处于低逻辑电平时,延迟控制信号生成电路330可以减小第二延迟控制信号d2《1:n》的逻辑值。当第一相位锁定信号pl1被使能时,延迟控制信号生成电路330可以改变第一和第二延迟控制信号d1《1:n》和d2《1:n》的逻辑值。例如,延迟控制信号生成电路330可以顺序地减小第一和第二延迟控制信号d1《1:n》和d2《1:n》的逻辑值,使得这些逻辑值像温度计代码一样被增大或减小。例如,延迟控制信号生成电路330可以将第一和第二延迟控制信号d1《1:n》和d2《1:n》的逻辑值从具有高逻辑电平的最高有效位的最高有效位起依次改变为低逻辑电平,从而顺序地减小第一和第二延迟控制信号d1《1:n》和d2《1:n》的逻辑值。延迟控制信号生成电路330可以减小第一延迟控制信号d1《1:n》和第二延迟控制信号d2《1:n》的逻辑值,直到第二相位锁定信号pl2被使能为止。当第二相位锁定信号pl2被使能时,延迟控制信号生成电路330可以保持第一和第二延迟控制信号d1《1:n》和d2《1:n》的逻辑值。例如,当第一和第二延迟控制信号d1《1:n》和d2《1:n》是4比特位信号时,第一延迟控制信号d1《1:n》的逻辑值为0011,并且第二延迟控制信号d2《1:n》的逻辑值为0111。延迟控制信号生成电路330可以首先将第一延迟控制信号d1《1:n》的第三位和第二延迟控制信号d2《1:n》的第二位改变为低逻辑电平。因此,第一延迟控制信号d1《1:n》可以具有逻辑值0001,第二延迟控制信号d2《1:n》可以具有逻辑值0011。然后,延迟控制信号生成电路330可以将第一延迟控制信号d1《1:n》的最低有效位和第二延迟控制信号d2《1:n》的第三位改变为低逻辑电平,以使第一延迟控制信号d1《1:n》的逻辑值可以为0000,第二延迟控制信号d2《1:n》的逻辑值可以为0001。当第一

延迟控制信号d1《1:n》的最低有效位转换为低逻辑电平时,第二相位锁定信号pl2可以被使能,并且延迟控制信号生成电路330可以不再减小第一延迟控制信号d1《1:n》和第二延迟控制信号d2《1:n》的逻辑值。因此,第一延迟控制信号d1《1:n》可以被设置为0000,第二延迟控制信号d2《1:n》可以被设置为0001。延迟控制信号生成电路330可以包括被配置以执行上述操作的任何逻辑电路。

43.图4是示出根据本实施例的信号生成电路的操作的框图。在图4中,条形图表示第一延迟电路110的基于第一延迟控制信号d1《1:n》设置的延迟时间,以及第二延迟电路120的基于第二延迟控制信号d2《1:n》设置的延迟时间。参照图1至图4,将如下描述根据实施例的信号生成电路100的操作。在《a》所示的初始状态下,延迟控制信号生成电路330可以输出具有默认值的第一和第二延迟控制信号d1《1:n》和d2《1:n》,并且第一和第二延迟电路110和120的延迟时间为可以被设置为参考延迟时间,其可以是第一时间t1。相位检测器131可以检测第一输出信号out1和第二输出信号out2的相位,并且可以生成相位检测信号pd。例如,当第一输出信号out1和第二输出信号out2之间的相位差大于目标值时,相位检测器131可以生成具有低逻辑电平的相位检测信号pd,并且延迟控制信号生成电路330可以基于相位检测信号pd延迟控制信号减小第二延迟控制信号d2《1:n》的逻辑值。当第二延迟电路120的延迟时间根据第二延迟控制信号d2《1:n》的逻辑值连续减小时,在第一输出信号out1和第二输出信号out2之间的相位差可接近目标值。当第一输出信号out1和第二输出信号out2之间的相位差变得小于目标值附近的目标值时,相位检测器131可以生成具有逻辑高电平的相位检测信号pd。延迟控制信号生成电路330可以增加第二延迟控制信号d2《1:n》的逻辑值,并且第一输出信号out1和第二输出信号out2之间的相位差可以变得大于目标值附近的目标值。相位检测器131可以生成具有低逻辑电平的相位检测信号pd,并且第一相位锁定检测器310可以检测到相位检测信号pd从高逻辑电平转变为低逻辑电平,并且使能第一相位锁定信号pl1。如《b》中所示,第二延迟电路120的延迟时间可以被设置为比第一时间t1短的可变延迟时间,并且可变延迟时间可以是第二时间t2。因此,第一延迟电路110的延迟时间与第二延迟电路120的延迟时间之间的差可以等于通过从第一时间减去第二时间而获得的时间t1-t2。当第一相位锁定信号pl1被使能时,延迟控制信号生成电路330可以顺序地减小第一延迟控制信号d1《1:n》和第二延迟控制信号d2《1:n》的逻辑值。由于第二时间t2在第一时间t1和第二时间t2当中是较短的,因此延迟控制信号生成电路330可以将第一延迟控制信号d1《1:n》和第二延迟控制信号d2《1:n》的逻辑值减小与第二延迟控制信号d2《1:n》相对应的逻辑值。即,延迟控制信号生成电路330可以将第一和第二延迟控制信号d1《1:n》和d2《1:n》的具有高逻辑电平的比特位以第二延迟控制信号d2《1:n》中具有高逻辑电平的比特位的数量来改变为低逻辑电平。当第二延迟控制信号d2《1:n》的逻辑值被最小化时,第二相位锁定检测器320可以使能第二相位锁定信号pl2。当第二相位锁定信号pl2被使能时,第一延迟电路110的延迟时间可以被设置为通过从第一时间减去第二时间而获得的时间t1-t2,如《c》所示,并且该第二延迟电路120的延迟时间可以基本上设置为0。因此,信号生成电路100可以通过将第一输入信号in1和第二输入信号in2延迟最小时间来生成第一输出信号out1和第二输出信号out2。信号生成电路100可以在调节第一输出信号out1和第二输出信号out2的占空比的同时最小化生成第一输出信号out1和第二输出信号out2所需的延迟时间。

44.图5是示出根据实施例的信号生成电路500的配置的框图。图1中示出的信号生成

电路100被配置为调节基于两个输入信号生成的两个输出信号的占空比和/或相位,而图5中所示的信号生成电路500可以被配置为调节基于四个输入信号生成的四个输出信号的占空比和/或相位。输入到信号生成电路或从信号生成电路输出的信号的数量不限于2或4,而可以设置为3或5或更多。参照图5,信号生成电路500可以包括第一延迟电路510、第二延迟电路520、第三延迟电路530、第四延迟电路540和占空比控制电路550。第一延迟电路510可以接收第一输入时钟信号iclk1,并通过可变地延迟第一输入时钟信号iclk1来生成第一相位时钟信号oclk1。第一延迟电路510可以通过基于第一延迟控制信号d1《1:n》可变地延迟第一输入时钟信号iclk1来生成第一相位时钟信号oclk1。通过将第一输入时钟信号iclk1延迟第一可变延迟时间,第一延迟电路510可以生成第一相位时钟信号oclk1。在初始状态下,第一延迟控制信号d1《1:n》可以具有默认值,并且基于具有默认值的第一延迟控制信号d1《1:n》可以将第一可变延迟时间设置为参考延迟时间。第二延迟电路520可以接收第二输入时钟信号iclk2,并通过可变地延迟第二输入时钟信号iclk2生成第二相位时钟信号oclk2。基于第二延迟控制信号d2《1:n》,第二延迟电路520可以通过可变地延迟第二输入时钟信号iclk2来生成第二相位时钟信号oclk2。第二延迟电路520可以通过将第二输入时钟信号iclk2延迟第二可变延迟时间来生成第二相位时钟信号oclk2。在初始状态下,第二延迟控制信号d2《1:n》可以具有默认值,并且可以基于具有默认值的第二延迟控制信号d2《1:n》将第二可变延迟时间设置为参考延迟时间。第三延迟电路530可以接收第三输入时钟信号iclk3,并通过可变地延迟第三输入时钟信号iclk3生成第三相位时钟信号oclk3。基于第三延迟控制信号d3《1:n》,第三延迟电路530可以通过可变地延迟第三输入时钟信号iclk3来生成第三相位时钟信号oclk3。第三延迟电路530可以通过将第三输入时钟信号iclk3延迟第三可变延迟时间来生成第三相位时钟信号oclk3。在初始状态下,第三延迟控制信号d3《1:n》可以具有默认值,并且基于具有默认值的第三延迟控制信号d3《1:n》,可以将第三可变延迟时间设置为参考延迟时间。第四延迟电路540可以接收第四输入时钟信号iclk4,并通过可变地延迟第四输入时钟信号iclk4来生成第四相位时钟信号oclk4。通过基于第四延迟控制信号d4《1:n》可变地延迟第四输入时钟信号iclk4,第四延迟电路540可以生成第四相位时钟信号oclk4。通过将第四输入时钟信号iclk4延迟第四可变延迟时间,第四延迟电路540可以生成第四相位时钟信号oclk4。在初始状态下,第四延迟控制信号d4《1:n》可以具有默认值,并且可以基于具有默认值的第四延迟控制信号d4《1:n》将第四可变延迟时间设置为参考延迟时间。

45.第一至第四输入时钟信号iclk1至iclk4可以顺序地具有相互之间90度的相位差。因此,第一输入时钟信号iclk1可以超前第二输入时钟信号iclk2 90度,第二输入时钟信号iclk2可以超前第三输入时钟信号iclk3 90度,第三输入时钟信号iclk3可以超前第四输入时钟信号iclk4 90度,第四输入时钟信号iclk4可以超前第一输入时钟信号iclk1 90度。理想地,当第一至第四延迟电路510、520、530和540的延迟时间等于参考延迟时间时,第一至第四相位时钟信号oclk1至oclk4可以顺序地具有90度的相位差。然而,第一至第四延迟电路510、520、530和540的延迟时间可以通过第一至第四延迟电路510、520、530和540的特性和工艺变化、或者生成或发送第一至第四输入时钟信号iclk1至iclk4的其他电路的特性和工艺变化而改变。另外,可以改变从第一至第四延迟电路510、520、530和540输出的第一至第四相位时钟信号oclk1至oclk4的相位差和占空比。占空比控制电路550可以检测第一至

第四相位时钟信号oclk1至oclk4的相位,并且通过单独地控制第一至第四可变延迟时间,可以补偿相位和/或占空比的变化。第一至第四延迟电路510、520、530和540可以具有与图2所示的第一和第二延迟电路110和120之一相同的结构,除了输入信号和输出信号之外。

46.占空比控制电路550可以检测第一至第四相位时钟信号oclk1至oclk4的相位,并且可以生成第一至第四延迟控制信号d1《1:n》至d4《1:n》。占空比控制电路550可以根据通过检测第一至第四相位时钟信号oclk1至oclk4的相位而获得的结果来单独调节第二至第四可变延迟时间。第一可变延迟时间可以被保持为参考延迟时间。在调节第二至第四可变延迟时间之后,占空比控制电路550可以将第一至第四可变延迟时间减小相同的时间。例如,占空比控制电路550可以将第一至第四可变延迟时间减小第一至第四可变延迟时间中的最短时间。占空比控制电路550可以检测第一至第四相位时钟信号oclk1至oclk4的相位,并单独地改变第二至第四延迟控制信号d2《1:n》至d4《1:n》的逻辑值,而第一延迟控制信号d1《1:n》可以保持默认值。占空比控制电路550可以改变第二至第四延迟控制信号d2《1:n》至d4《1:n》的逻辑值,然后,占空比控制电路550可以将第一至第四延迟控制信号d1《1:n》至d4《1:n》的逻辑值减小相同的值。例如,占空比控制电路550可以将第一至第四延迟控制信号d1《1:n》至d4《1:n》的逻辑值减小第一至第四延迟控制信号d1《1:n》至d4《1:n》中具有最小逻辑值的延迟控制信号的逻辑值。

47.占空比控制电路550可以包括相位检测器551和延迟控制电路552,其中相位检测器551可以检测第一至第四相位时钟信号oclk1至oclk4的相位,并且可以生成第一相位检测信号pd1、第二相位检测信号pd2和第三相位检测信号pd3。相位检测器551可以包括能够检测四个输入信号之间的相位差的任何公知的相位检测器或占空比检测器。例如,相位检测器551可以检测第一相位时钟信号oclk1和第二相位时钟信号oclk2之间的相位差是否相应于第一目标值。然后,相位检测器551可以生成第一相位检测信号pd1。第一目标值可以相应于第一输入时钟信号ickl1的1/4周期。相位检测器551可以检测第一相位时钟信号oclk1和第三相位时钟信号oclk3之间的相位差是否相应于第二目标值,该第二目标值可以相应于第一输入时钟信号ickl1的1/2周期,以及可以生成第二相位检测信号pd2。相位检测器551可以检测第一相位时钟信号oclk1和第四相位时钟信号oclk4之间的相位差是否相应于第三目标值,该第三目标值可以相应于第一输入时钟信号ickl1的3/4周期,以及可以生成第三相位检测信号pd3。至此,已经描述了相位检测器551的功能和操作。然而,本实施例不限于此,并且可以将以不同方式起作用和工作的各种相位检测器用作相位检测器551。

48.延迟控制电路552可以在初始状态下生成具有默认值的第一至第四延迟控制信号d1《1:n》至d4《1:n》。通过基于第一相位检测信号pd1改变第二延迟控制信号d2《1:n》的逻辑值,延迟控制电路552可以改变第二可变延迟时间。通过基于第二相位检测信号pd2改变第三延迟控制信号d3《1:n》的逻辑值,延迟控制电路552可以改变第三可变延迟时间。通过基于第三相位检测信号pd3改变第四延迟控制信号d4《1:n》的逻辑值,延迟控制电路552可以改变第四可变延迟时间。在通过改变第二至第四延迟控制信号d2《1:n》至d4《1:n》的逻辑值来改变第二至第四可变延迟时间之后,延迟控制电路552可以将第一至第四延迟控制信号d1《1:n》至d4《1:n》的逻辑值减小相同的值,从而将第一至第四可变延迟时间减小相同的时间。

49.图6是示出图5中所示的延迟控制电路552的配置的框图。参照图6,延迟控制电路

552可以包括第一相位锁定检测器610、第二相位锁定检测器620和第二延迟控制信号生成电路630。第一相位锁定检测器610可以接收第一至第三相位检测信号pd1至pd3,并且可以基于第一至第三相位检测信号pd1至pd3生成第一相位锁定信号pl1。由于第一相位锁定检测器610被配置为接收三个相位检测信号,所以,除了图3中所示的第一相位锁定检测器310的那些部件之外,第一相位锁定检测器610还可包括其他部件。第一相位锁定检测器610可以包括第一触发器611、第二触发器612、第三触发器613、第四触发器614、第五触发器615、第六触发器616和第一门控电路617。第一触发器611和第二触发器612可以是第一锁定检测器,用于基于第一相位检测信号pd1生成第一锁定信号lock1。第一触发器611可以具有被配置为接收电源电压vdd的输入端子d和被配置为接收第一相位检测信号pd1的时钟端子。第二触发器612可以具有耦接到第一触发器611的输出端子q的输入端子d,并且可以被配置为接收从第一触发器611输出的信号。第二触发器612可以具有被配置为接收第一相位检测信号pd1的反相信号的时钟端子、以及被配置为输出第一锁定信号lock1的输出端子q。当先前接收的第一相位检测信号pd1具有高逻辑电平并且当前接收的第一相位检测信号pd1具有低逻辑电平时,第一触发器611和第二触发器612可以输出电源电压vdd作为第一锁定信号lock1,并且因此将第一锁定信号lock1使能为高逻辑电平。

50.第三触发器613和第四触发器614可以是第二锁定检测器,用于基于第二相位检测信号pd2生成第二锁定信号lock2。第三触发器613可以具有被配置为接收电源电压vdd的输入端子d和被配置为接收第二相位检测信号pd2的时钟端子。第四触发器614可以具有耦接到第三触发器613的输出端子q的输入端子d。此外,第四触发器614可以被配置为接收从第三触发器613输出的信号。第四触发器614可以具有被配置为接收第二相位检测信号pd2的反相信号的时钟端子,以及被配置为输出第二锁定信号lock2的输出端子q。当先前接收的第二相位检测信号pd2具有高逻辑电平并且当前接收的第二相位检测信号pd2具有低逻辑电平时,第三触发器613和第四触发器614可以输出电源电压vdd作为第二锁定信号lock2,从而将第二锁定信号lock2使能为高逻辑电平。

51.第五和第六触发器615和616可以是第三锁定检测器,用于基于第三相位检测信号pd3生成第三锁定信号lock3。第五触发器615可以具有被配置为接收电源电压vdd的输入端子d和被配置为接收第三相位检测信号pd3的时钟端子。第六触发器616可以具有耦接到第五触发器615的输出端子的输入端子d,并且可以被配置为接收从第五触发器615输出的信号。第六触发器616可以具有被配置为接收第三相位检测信号pd3的反相信号的时钟端子和被配置为输出第三锁定信号lock 3的输出端子。当先前接收的第三相位检测信号pd3具有高逻辑电平并且当前接收的第三相位检测信号pd3具有低逻辑电平时,第五和第六触发器615和616可以输出电源电压vdd作为第三锁定信号lock3,从而将第三锁定信号lock3使能为高逻辑电平。

52.第一门控电路617可以接收第一至第三锁定信号lock1至lock3,并且输出第一相位锁定信号pl1。当第一至第三锁定信号lock1至lock3全部被使能时,第一门控电路617可以使能第一相位锁定信号pl1。第一门控电路617可以包括与门。当第一至第三锁定信号lock1至lock3全部被使能为高逻辑电平时,第一门控电路617可以输出被使能为高逻辑电平的第一相位锁定信号pl1。

53.第二相位锁定检测器620可以基于第一延迟控制信号d1《1:n》、第二延迟控制信号

d2《1:n》、第三延迟控制信号d3《1:n》和第四延迟控制信号d4《1:n》来生成第二相位锁定信号pl2。基于第一至第四延迟控制信号d1《1:n》至d4《1:n》的至少一些比特位,第二相位锁定检测器620可以生成第二相位锁定信号pl2。例如,第二相位锁定检测器620可以接收第一至第四延迟控制信号d1《1:n》至d4《1:n》的最低有效位,并检测最低有效位的逻辑电平并使能第二相位锁定信号pl2。当第一至第四延迟控制信号d1《1:n》至d4《1:n》的最低有效位中的任何一个变为低逻辑电平时,第二相位锁定检测器620可以使能第二相位锁定信号pl2。当第一至第四延迟电路510、520、530和540中的任何一个具有最小延迟时间时,第二相位锁定检测器620可以使能第二相位锁定信号pl2。第二相位锁定检测器620可以包括与非门631。与非门631可以接收第一至第四延迟控制信号d1《1:n》至d4《1:n》的最低有效位,并输出第二相位锁定信号pl2。当第一至第四延迟控制信号d1《1:n》至d4《1:n》的最低有效位中的任何一个转变为逻辑低电平时,与非门631可以将第二相位锁定信号pl2使能为高逻辑电平。

54.延迟控制信号生成电路630可以接收第一至第三相位检测信号pd1至pd3以及第一和第二相位锁定信号pl1和pl2,并生成第一至第四延迟控制信号d1《1:n》至d4《1:n》。延迟控制信号生成电路630在初始状态下可以输出具有默认值的第一至第四延迟控制信号d1《1:n》至d4《1:n》。延迟控制信号生成电路630可以基于第一至第三相位检测信号pd1至pd3改变第二至第四延迟控制信号d2《1:n》至d4《1:n》的逻辑值,直到第一相位锁定信号pl1被使能为止。例如,当第一至第三相位检测信号pd1至pd3都处于高逻辑电平时,延迟控制信号生成电路630可以增加第二至第四延迟控制信号d2《1:n》至d4《1:n》的逻辑值。当第一至第三相位检测信号pd1至pd3都处于低逻辑电平时,延迟控制信号生成电路630可以减小第二至第四延迟控制信号d2《1:n》至d4《1:n》的逻辑值。当第一相位锁定信号pl1被使能时,延迟控制信号生成电路630可以改变第一至第四延迟控制信号d1《1:n》至d4《1:n》的逻辑值。例如,延迟控制信号生成电路630可以顺序地减小第一至第四延迟控制信号d1《1:n》至d4《1:n》的逻辑值。延迟控制信号生成电路630可以将第一至第四延迟控制信号d1《1:n》至d4《1:n》的逻辑值从具有高逻辑电平的最高有效位起顺序地改变为低逻辑电平。延迟控制信号生成电路630可以减小第一至第四延迟控制信号d1《1:n》至d4《1:n》的逻辑值,直到第二相位锁定信号pl2被使能为止。当第二相位锁定信号pl2被使能时,延迟控制信号生成电路630可以保持第一至第四延迟控制信号d1《1:n》至d4《1:n》的逻辑值。因此,延迟控制信号生成电路630可以将第一至第四延迟控制信号d1《1:n》至d4《1:n》的逻辑值减小第一至第四延迟控制信号d1《1:n》至d4《1:n》当中具有最小逻辑值的延迟控制信号的逻辑值,从而将第一至第四可变延迟时间设置为最小延迟时间。

55.图7是示出根据实施例的半导体装置700的配置的框图。参照图7,半导体装置700可以包括时钟接收器710、第一时钟分频器720、第一占空比校正电路730和延迟锁定环电路740。时钟接收器710可以接收从半导体装置700的外部发送的系统时钟信号clk,并且可以生成输入时钟信号inclk,其中系统时钟信号clk可以作为差分信号或单端信号发送。当系统时钟信号clk作为差分信号被发送时,时钟接收器710可以通过对系统时钟信号clk和互补信号clkb进行差分放大来生成输入时钟信号inclk。当系统时钟信号clk作为单端信号发送时,输入时钟信号inclk可以由时钟接收器710通过差分放大系统时钟信号clk和参考电压vref而生成。参考电压vref可以具有对应于系统时钟信号clk的摆动范围的中部的电压电平。

56.第一时钟分频器720可以通过对输入时钟信号inclk进行分频来生成第一分频时钟信号clk1和第二分频时钟信号clk2。通过对输入时钟信号inclk的频率进行分频,第一时钟分频器720可以生成具有比输入时钟信号inclk的频率低的频率的第一和第二分频时钟信号clk1和clk2。例如,第一时钟分频器720可以将输入时钟信号inclk的频率除以2,并且第一和第二分频时钟信号clk1和clk2的频率都可以相应于输入时钟信号inclk的频率的1/2。第一分频时钟信号clk1可以与第二分频时钟信号clk2具有180度的相位差。

57.第一占空比校正电路730可以接收第一和第二分频时钟信号clk1和clk2,并生成第一参考时钟信号rclk和第二参考时钟信号fclk。通过延迟第一和第二分频时钟信号clk1和clk2,第一占空比校正电路730可以生成第一和第二参考时钟信号rclk和fclk。第一占空比校正电路730可以比较第一参考时钟信号rclk和第二参考时钟信号fclk的相位,并且调节第二分频时钟信号clk2被延迟的时间。在调节第二分频时钟信号clk2被延迟的时间之后,第一占空比校正电路730可以将第一分频时钟信号clk1和第二分频时钟信号clk2被延迟的时间减小所述时间。图1所示的信号生成电路100可以被用作第一占空比校正电路730,使得第一和第二分频时钟信号clk1和clk2可以对应于图1的第一和第二输入信号in1和in2,第一参考时钟信号rclk和第二参考时钟信号fclk可对应于图1的第一输出信号out1和第二输出信号out2。第一占空比校正电路730可以使调节第一参考时钟信号rclk和第二参考时钟信号fclk的相位和占空比所需的延迟时间最小化。

58.延迟锁定环电路740可以接收第一参考时钟信号rclk和第二参考时钟信号fclk,并且可以通过对第一参考时钟信号rclk和第二参考时钟信号fclk执行延迟锁定操作来生成一个或多个输出时钟信号。例如,延迟锁定环电路740可以生成第一至第四输出时钟信号iclk,qclk,ibclk和qbclk。然而,可以将延迟锁定环电路740修改为生成大于或小于四个的输出时钟信号。通过比较第一参考时钟信号rclk和反馈时钟信号fbclk的相位并延迟第一参考时钟信号rclk和第二参考时钟信号fclk,延迟锁定环电路740可以生成一个或多个输出时钟信号。延迟锁定环电路740可通过延迟一个或多个输出时钟信号来生成反馈时钟信号fbclk。

59.延迟锁定环电路740可以包括第一延迟线741、第二延迟线742、第二时钟分频器743、第二占空比校正电路744、延迟模型电路745和延迟线控制电路746。第一延迟线741可以接收第一参考时钟信号rclk,并通过基于延迟线控制信号dlc延迟第一参考时钟信号rclk来生成第一延迟时钟信号clkd1。第一延迟线741可以具有基于延迟线控制信号dlc来决定的延迟时间。第二延迟线742可以接收第二参考时钟信号fclk,并且通过基于延迟线控制信号dlc延迟第二参考时钟信号fclk来生成第二延迟时钟信号clkd2。第二延迟线742可以具有基于延迟线控制信号dlc决定的延迟时间。

60.第二时钟分频器743可以接收第一和第二延迟时钟信号clkd1和clkd2,并且对第一和第二延迟时钟信号clkd1和clkd2进行分频。当第二时钟分频器743分频第一和第二延迟时钟信号clkd1和clkd2的频率时,输出四个经分频的时钟信号。例如,第二时钟分频器743可以将第一延迟时钟信号clkd1和第二延迟时钟信号clkd2的频率除以2,并且生成顺序地具有90度的相位差的四个经分频的时钟信号。

61.第二占空比校正电路744可以接收从第二时钟分频器743输出的四个经分频的时钟信号,并生成一个或多个输出时钟信号,例如,第一输出时钟信号iclk、第二输出时钟信

号qclk、第三输出时钟信号ibclk和第四输出时钟信号qbclk。一个或多个输出时钟信号可以例如是第一输出时钟信号iclk。第二占空比校正电路744可以检测第一至第四输出时钟信号iclk、qclk、ibclk和qbclk的相位,并调节第一至第四输出时钟信号iclk、qclk、ibclk和qbclk的相位和/或占空比。第二占空比校正电路744可以被实现为任何公知的占空比校正电路。在一个实施例中,图5中示出的信号生成电路500可以被用作第二占空比校正电路744。从第二时钟分频器743输出的四个经分频的时钟信号可以相应于图5的第一至第四输入时钟信号iclk1、iclk2、iclk3和iclk4,第一至第四输出时钟信号iclk、qclk、ibclk和qbclk可以相应于图5的第一至第四相位时钟信号oclk1、oclk2、oclk3和oclk4。

62.延迟模型电路745可以通过延迟一个或多个输出时钟信号来生成反馈时钟信号fbclk。延迟模型电路745可以接收第一输出时钟信号iclk,并且通过将第一输出时钟信号iclk延迟建模的延迟时间来生成反馈时钟信号fbclk。建模的延迟时间可以相应于在时钟信号在半导体装置700中传播所通过的路径中发生的延迟时间。延迟模型电路745可以具有固定的延迟时间和可变的延迟时间,其中,固定的延迟时间可以是恒定的延迟时间,可变延迟时间可以是可以以各种方式改变的延迟时间。通过对由第一占空比校正电路730以外的电路引起的延迟时间进行建模,可以在时钟信号在半导体装置700中传播所通过的这些路径中出现的这些延迟时间当中获得固定的延迟时间。可变延迟时间可以以与第一占空比校正电路730的延迟时间基本相同的方式被改变。例如,延迟模型电路745可以包括具有与包含在第一占空比校正电路730中的延迟电路的结构相似结构的延迟电路。代替地,延迟模型电路745可以具有与所述延迟电路的延迟时间的1/2相对应的可变延迟时间。即,可变延迟时间的最大值可以是所述延迟电路的延迟时间的1/2,并且可以相应于参考延迟时间。基于在第一占空比校正电路730中使用的延迟控制信号,延迟模型电路745可以改变可变延迟时间。当使用第一延迟控制信号d1《1:n》来调节图1中的第一延迟电路110的延迟时间时,例如,延迟模型电路745可以从第一占空比校正电路730接收第一延迟控制信号d1《1:n》。延迟模型电路745的可变延迟时间可以被减小在第一占空比校正电路730的延迟电路中所减小的延迟时间量。因此,延迟锁定环电路740可以更精确地执行延迟锁定操作,并且可以减小时钟信号已经传播通过的路径的总延迟时间。

63.延迟线控制电路746可以接收第一参考时钟信号rclk和反馈时钟信号fbclk,并且通过比较第一参考时钟信号rclk和反馈时钟信号fbclk的相位来生成延迟线控制信号dlc。通过根据第一参考时钟信号rclk和反馈时钟信号fbclk之间的相位差来改变延迟线控制信号dlc的逻辑值,延迟线控制电路746可以改变第一延迟线741和第二延迟线742的延迟时间。

64.半导体装置700还可包括时钟分配网络750和时钟发送器760。时钟分配网络750可以接收由延迟锁定环电路740生成的一个或多个输出时钟信号,并且可以传输所述一个或多个输出时钟信号。时钟分配网络750可以接收第一至第四输出时钟信号iclk、qclk、ibclk和qbclk,并传输所述第一至第四输出时钟信号iclk、qclk、ibclk和qbclk。时钟分配网络750可以耦接到多个数据输入/输出电路(未示出),并且可以将第一至第四输出时钟信号iclk、qclk、ibclk和qbclk传输到多个数据输入/输出电路。时钟分配网络750可以包括传输线、转发器等,其被配置为传输第一至第四输出时钟信号iclk、qclk、ibclk和qbclk。

65.时钟发送器760可以接收时钟分配网络750的输出,可以生成数据选通信号dqs,并

且可以将数据选通信号dqs发送到半导体装置700的外部,其中数据选通信号dqs可以是与从多个数据输入/输出电路输出的数据同步的时钟信号。图7示出了一个时钟发送器,但是该时钟发送器可以设置在每个数据输入/输出电路中。

66.图8是示出图7中所示的延迟模型电路745的配置的图。参照图8,延迟模型电路745可以包括第一延迟器810、第二延迟器820、第一驱动器组831、第二驱动器组832和输出反相器840。第一延迟器810可以接收第一输出时钟信号iclk,可以延迟第一输出时钟信号iclk,并且可以具有与延迟模型电路745的固定延迟时间相应的延迟量。第二延迟器820可以接收第一延迟器810的输出,并且可以延迟第一延迟器810的输出。第二延迟器820的延迟量的最大值可以被设置为与构成第一占空比校正电路730的延迟电路(例如图1的第一延迟电路110)的最大延迟时间的1/2相应的延迟时间,第二延迟器820的延迟量可以相应于参考延迟时间。基于从构成第一占空比校正电路730的占空比控制电路提供的延迟控制信号d1《1:n》,延迟模型电路745可以改变第一和第二驱动器组831和832的权重,因此可以改变第一输出时钟信号iclk被延迟的时间。第一驱动器组831和第二驱动器组832中的每一个可以接收延迟控制信号d1《1:n》。

67.第一驱动器组831可以接收从第一延迟器810输出的信号。基于延迟控制信号d1《1:n》,第一驱动器组831可以以可变的可驱动性将从第一延迟器810输出的信号反相。可以基于延迟控制信号d1《1:n》的反相信号来改变第一驱动器组831的可驱动性。第一驱动器组831可以包括与延迟控制信号d1《1:n》的各个比特位相对应的多个反相器。反相器可各自接收延迟控制信号d1《1:n》的一个比特位。例如,随着延迟控制信号d1《1:n》的比特位中具有低逻辑电平的比特位的数量增加,第一驱动器组831的可驱动性可以增加,并且延迟模型电路745的延迟时间可以缩短。

68.第二驱动器组832可以接收从第二延迟器820输出的信号。基于延迟控制信号d1《1:n》,第二驱动器组832可以以可变的可驱动性将从第二延迟器820输出的信号反相。可以基于延迟控制信号d1《1:n》来改变第二驱动器组832的可驱动性。第二驱动器组832可以包括与延迟控制信号d1《1:n》的各个位相对应的多个反相器,其中,这些反相器可以各自接收延迟控制信号d1《1:n》的一个比特位。例如,随着延迟控制信号d1《1:n》的比特位中具有高逻辑电平的比特位的数量增加,第二驱动器组832的可驱动性可以增加,并且延迟模型电路745的延迟时间可以加长。

69.输出反相器840可以共同耦接到第一和第二驱动器组831和832,并接收第一和第二驱动器组831和832的输出。通过使得第一和第二驱动器组831和832的输出反相,输出反相器840可以生成反馈时钟信号fbclk。输出反相器840可以通过混合第一和第二驱动器组831和832的输出的相位来生成反馈时钟信号fbclk,所述第一和第二驱动器组831和832的输出是根据基于延迟控制信号d1《1:n》确定的权重而生成的。

70.延迟模型电路745可以具有被设置为与第一延迟器810的延迟量相应的延迟时间的最小延迟时间、以及被设置为与第一延迟器810和第二延迟器820的延迟量之和相应的延迟时间的最大延迟时间。在第一占空比校正电路730中改变的延迟时间可以改变延迟模型电路745的延迟时间。

71.图9是示出根据本实施例的半导体装置700的操作的框图。在图9中,条形图表示延迟第一分频时钟信号clk1的第一占空比校正电路730的延迟电路910的延迟时间、延迟第二

分频时钟信号clk2的第一占空比校正电路730的延迟电路920的延迟时间、以及延迟第一输出时钟信号iclk信号的延迟模型电路745的延迟时间。参照图7至图9,将如下描述根据本实施例的半导体装置700的操作。当时钟接收器710接收系统时钟信号clk并生成输入时钟信号inclk时,第一时钟分频器720可以通过对输入时钟信号inclk进行分频生成第一和第二分频时钟信号clk1和clk2。在《a》中所示的初始状态下,用于延迟第一分频时钟信号clk1的延迟电路910的延迟时间可以被设置为第一时间t1,用于延迟第二分频时钟信号clk2的延迟电路920的延迟时间也可以被设置为第一时间t1。延迟模型电路745的延迟时间可以被设置为固定延迟时间tf和第一时间t1之和。理想地,第一和第二分频时钟信号clk1和clk2需要具有彼此之间180度的相位差,并且每一个都具有50:50的占空比。然而,取决于时钟接收器710和第一时钟分频器720的特性,第一和第二分频时钟信号clk1和clk2可以既不具有相互之间180度的相位差、也不具有50:50的占空比。因此,通过可变地延迟第一和第二分频时钟信号clk1和clk2,第一占空比校正电路730可以生成第一和第二参考时钟信号rclk和fclk,从而将第一和第二参考时钟信号rclk和fclk之间的相位差调节为180并将第一和第二参考时钟信号rclk和fclk的占空比调节为50:50。例如,当减小用于延迟第二参考时钟信号fclk的延迟电路920的延迟时间以调节第二参考时钟信号fclk的相位和/或占空比时,如《b》所示,用于延迟第一参考时钟信号rclk的延迟电路910的延迟时间可以保持为第一时间t1,用于延迟第二参考时钟信号fclk的延迟电路920的延迟时间可以变为第二时间t2。即,可以将延迟电路920的延迟时间减小第一时间与第二时间之间的差t1-t2。延迟模型电路745的延迟时间仍可以保持为固定延迟时间tf和第一时间t1之和。

72.然后,第一占空比校正电路730可以一起减小延迟电路910和920的延迟时间以及延迟模型电路745的延迟时间。第二时间t2可以是在用于延迟第一参考时钟信号rclk和第二参考时钟信号fclk的延迟电路910和920的延迟时间之中的最小延迟时间。延迟电路910和920以及延迟模型电路745的延迟时间可以全部减小第二时间t2。如《c》所示,可以将用于延迟第一参考时钟信号rclk的延迟电路910的延迟时间设置为时间t1-t2,该时间t1-t2是通过从第一时间减去第二时间而获得的,用于延迟第二参考时钟信号fclk的延迟电路920的延迟可以基本为零。延迟模型电路745的延迟时间可以被设置为固定延迟时间tf与时间t1-t2之和,时间t1-t2通过从第一时间减去第二时间而获得。因此,可以将延迟电路910和920以及延迟模型电路745的延迟时间全部设置为最小时间。

73.图10是示出根据实施例的半导体装置1000的配置的框图。参照图10,半导体装置1000可以包括时钟接收器1010、延迟锁定环电路1020、时钟分频器1030、占空比校正电路1040、时钟分配网络1050和时钟发送器1060。在图7中,第一占空比校正电路730可以设置在延迟锁定环电路740和接收时钟接收器710的输出的第一时钟分频器720之间。然而,如图10所示,占空比校正电路1040可以设置在时钟分配网络1050与接收延迟锁定环电路1020的输出的时钟分频器1030之间。半导体装置1000可以包括与在图7中所示的半导体装置700的组件类似的组件,这里将省略对相同部件的相同功能和操作的重复描述。时钟接收器1010可以接收系统时钟信号clk并生成参考时钟信号rclk。

74.通过对参考时钟信号rclk执行延迟锁定操作,延迟锁定环电路1020可以生成延迟时钟信号clkd。延迟锁定环电路1020可以将参考时钟信号rclk的相位与通过延迟第一输出时钟信号iclk生成的反馈时钟信号fbclk的相位进行比较,并且可变地延迟参考时钟信号

rclk。通过可变地延迟参考时钟信号rclk,延迟锁定环电路1020可以生成延迟的时钟信号clkd。延迟锁定环电路1020可以包括延迟线1021、延迟模型电路1022和延迟线控制电路1023。通过基于延迟线控制信号dlc可变地延迟参考时钟信号rclk,延迟线1021可以生成延迟时钟信号clkd。延迟模型电路1022可以接收通过占空比校正电路1040生成的第一输出时钟信号iclk,并且通过延迟第一输出时钟信号iclk来生成反馈时钟信号fbclk。延迟模型电路1022可以接收将在下面将描述的占空比校正电路1040中使用的延迟控制信号d1《1:n》,并且具有基于延迟控制信号d1《1:n》而改变的延迟时间。通过比较参考时钟信号rclk和反馈时钟信号fbclk的相位,延迟线控制电路1023可以生成延迟线控制信号dlc。

75.时钟分频器1030可以从延迟锁定环电路1020接收延迟时钟信号clkd。时钟分频器1030可以通过对延迟时钟信号clkd进行分频来至少生成第一和第二分频时钟信号clk1和clk2。时钟分频器1030可以通过将延迟时钟信号clkd的频率除以2来生成第一和第二分频时钟信号clk1和clk2,它们之间具有90度的相位差。通过将第一和第二分频时钟信号clk1和clk2反相,时钟分频器1030可以生成四个分频时钟信号。时钟分频器1030可以生成与第一分频时钟信号clk1具有180度的相位差的第三分频时钟信号clk3和与第二分频时钟信号clk2具有180度的相位差的第四分频时钟信号clk4。理想地,第一至第四分频时钟信号clk1至clk4需要顺序地具有90度的相位差,并且每一个都具有50:50的占空比。然而,可以根据时钟分频器1030的特性和工艺变化来改变第一至第四分频时钟信号clk1至clk4的相位差和占空比。可以提供占空比校正电路1040以补偿由时钟分频器1030引起的相位和相位变化。

76.占空比校正电路1040可以至少接收第一和第二分频时钟信号clk1和clk2,并生成第一输出时钟信号iclk和第二输出时钟信号qclk。占空比校正电路1040可以通过延迟第一和第二分频时钟信号clk1和clk2来生成第一和第二输出时钟信号iclk和qclk,并且比较第一和第二输出时钟信号iclk和qclk的相位以调节第二输出时钟信号qclk被延迟的时间。在调节第二输出时钟信号qclk被延迟的时间之后,占空比校正电路1040可以将第一输出时钟信号iclk和第二输出时钟信号qclk被延迟的时间减小相同的时间。此时,基于用于设置第一输出时钟信号iclk被延迟的时间的延迟控制信号d1《1:n》,延迟模型电路1022的延迟时间可以减小得与第一输出时钟信号iclk的延迟时间一样多。图1中所示的信号生成电路100可以被用作占空比校正电路1040。第一和第二分频时钟信号clk1和clk2可以相应于图1的第一和第二输入信号in1和in2,第一和第二输出时钟信号iclk和qclk可以相应于图1的第一和第二输出信号out1和out2。占空比校正电路1040除了第一和第二分频时钟信号clk1和clk2之外,还可以另外接收第三和第四分频时钟信号clk3和clk4。当占空比校正电路1040一起接收到第一至第四分频时钟信号clk1至clk4时,在图5中所示的信号生成电路500可以被用作占空比校正电路1040。第一至第四分频时钟信号clk1至clk4可以相应于图5的第一至第四输入时钟信号iclk1至iclk4,第一至第四输出时钟信号iclk、qclk、ibclk和qbclk可以相应于图5的第一至第四相位时钟信号oclk1至oclk4。时钟分配网络1050可以传输从占空比校正电路1040输出的第一至第四输出时钟信号iclk、qclk、ibclk和qbclk,并且,时钟发送器1060可以基于时钟分配网络1050的输出生成数据选通信号dqs。

77.图11是示出根据实施例的半导体装置1100的配置的框图。参照图11,半导体装置1100可以包括时钟接收器1110、延迟锁定环电路1120、多相时钟生成电路1130、时钟分配网

络1140、占空比校正电路1150和时钟发送器1160。在图7中,占空比校正电路730设置在延迟锁定环电路740和接收时钟接收器710的输出的第一时钟分频器720之间,在图10中,占空比校正电路1040设置在时钟分配网络1050和接收延迟锁定环电路1020的输出的时钟分频器1030之间。然而,在图11中,占空比校正电路1150可以设置在时钟分配网络1140和时钟发送器1160之间。半导体装置1100可以包括与在图7或图10中所示的半导体装置700或1000相似的组件,并且这里将省略对相同部件的相同功能和操作的重复描述。时钟接收器1110可以接收系统时钟信号clk并生成参考时钟信号rclk。

78.通过对参考时钟信号rclk执行延迟锁定操作,延迟锁定环电路1120可以生成延迟时钟信号clkd。延迟锁定环电路1120可以将参考时钟信号rclk的相位与通过延迟所述延迟时钟信号clkd而生成的反馈时钟信号fbclk的相位进行比较,并且改变参考时钟信号rclk被延迟的时间。延迟锁定环电路1120可以包括延迟线1121、延迟模型电路1122和延迟线控制电路1123。延迟线1121可以基于延迟线控制信号dlc来延迟参考时钟信号rclk,并且输出延迟时钟信号clkd。通过延迟所述延迟时钟信号clkd,延迟模型电路1122可以生成反馈时钟信号fbclk。延迟模型电路1122可以接收要在下面将描述的占空比校正电路1150中使用的延迟控制信号d1《1:n》,并且具有基于延迟控制信号d1《1:n》而改变的延迟时间。通过比较参考时钟信号rclk和反馈时钟信号fbclk的相位,延迟线控制电路1123可以生成延迟线控制信号dlc。

79.多相时钟生成电路1130可以接收从延迟锁定环电路1120输出的延迟时钟信号clkd。多相时钟生成电路1130可以基于延迟时钟信号clkd至少生成第一输出时钟信号iclk和第二输出时钟信号qclk。多相时钟生成电路1130可以包括时钟分频器(未示出),并且通过经由时钟分频器对延迟时钟信号clkd进行分频来生成具有相互之间90度的相位差的第一输出时钟信号iclk和第二输出时钟信号。多相时钟生成电路1130可以进一步生成第三和第四输出时钟信号ibclk和qbclk,其中第三输出时钟信号ibclk可以与第一输出时钟信号iclk具有180度的相位差,第四输出时钟信号qbclk可以与第二输出时钟信号qclk具有180度的相位差。

80.时钟分配网络1140可以至少接收第一输出时钟信号iclk和第二输出时钟信号qclk,并输出第一分配时钟信号dclk1和第二分配时钟信号dclk2。时钟分配网络1140可以驱动第一和第二输出时钟信号iclk和qclk,并且可以输出第一和第二分配时钟信号dclk1和dclk2,其中第一分配时钟信号dclk1可以具有与第一输出时钟信号iclk相应的相位,第二分配时钟信号dclk2可以具有与第二输出时钟信号qclk相应的相位。时钟分配网络1140可以进一步接收第三和第四输出时钟信号ibclk和qbclk,并且还输出第三分配时钟信号dclk3和第四分配时钟信号dclk4。第三分配时钟信号dclk3可以具有相应于第三输出时钟信号ibclk的相位,并且第四分配时钟信号dclk4可以具有相应于第四输出时钟信号qbclk的相位。理想地,第一至第四分配时钟信号dclk1至dclk4需要顺序地具有相互之间90度的相位差,并且每个分配时钟信号都具有50:50的占空比。然而,第一至第四分配时钟信号dclk1至dclk4的相位差和占空比可以根据时钟分配网络1140的特性和工艺变化而改变。由于时钟分配网络1140包括通过其来传输时钟信号的长时钟传输线,因此难以维持第一至第四输出时钟信号iclk、qclk、ibclk和qbclk的相位差和占空比。可以提供占空比校正电路1050以补偿由时钟分配网络1140引起的相位和占空比的变化。

81.占空比校正电路1150可以至少接收第一分配时钟信号dclk1和第二分配时钟信号dclk2,并生成第一传输时钟信号tclk1和第二传输时钟信号tclk2。占空比校正电路1150可以通过延迟第一分配时钟信号dclk1和第二分配时钟信号dclk2来生成第一传输时钟信号tclk1和第二传输时钟信号tclk2,并且比较第一传输时钟信号tclk1和第二传输时钟信号tclk2的相位,以调节第二分配时钟信号dclk2被延迟的时间。在调节第二分配时钟信号dclk2被延迟的时间之后,占空比校正电路1150可以将第一和第二分配时钟信号dclk1和dclk2被延迟的时间减小相同的时间。此时,基于用于设置第一分配时钟信号dclk1被延迟的时间的延迟控制信号d1《1:n》,延迟模型电路1122的延迟时间可以减小与第一分配时钟信号dclk1的延迟时间的减小量一样多的减小量。图1中所示的信号生成电路100可以被用作占空比校正电路1150。第一和第二分配时钟信号dclk1和dclk2可以相应于图1的第一和第二输入信号in1和in2,第一和第二传输时钟信号tclk1和tclk2可以相应于图1的第一和第二输出信号out1和out2。占空比校正电路1150可以进一步接收第三分配时钟信号dclk3和第四分配时钟信号dclk4,并且还生成第三传输时钟信号tclk3和第四传输时钟信号tclk4。占空比校正电路1150可以通过延迟第一至第四分配时钟信号dclk1至dclk4来生成第一至第四传输时钟信号tclk1、tclk2、tclk3和tclk4,并且将第一至第四分配时钟信号dclk1至dclk4的相位进行比较,以调节第二至第四分配时钟信号dclk2至dclk4被延迟的时间。在调节第二至第四分配时钟信号dclk2至dclk4被延迟的时间之后,占空比校正电路1150可以将第一至第四分配时钟信号dclk1至dclk4被延迟的时间减小相同的时间。此时,基于用于设置第一分配时钟信号dclk1被延迟的时间的延迟控制信号d1《1:n》,延迟模型电路1122的延迟时间可以减小与第一分配时钟信号dclk1的延迟时间的减小量一样多的减小量。图5中所示的信号生成电路500可以被用作占空比校正电路1150。第一至第四分配时钟信号dclk1至dclk4可以相应于图5的第一至第四输入时钟信号iclk1至iclk4,第一至第四传输时钟信号tclk1至tclk4可以相应于图5的第一至第四相位时钟信号oclk1至oclk4。

82.尽管上面已经描述了各种实施例,但是本领域技术人员将理解:所描述的实施例仅是示例。因此,不应基于所描述的实施例来限制在此已经描述的信号生成电路和方法以及半导体装置。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1