一种含数字校准的逐次逼近模数转换器

1.本发明涉及视数模转换的技术领域,尤其涉及一种含数字校准的逐次逼近 模数转换器。

背景技术:

2.模数转换器(adc)是模拟前端和数字处理单元之间的接口,其分辨率、面 积是设计的重要考虑因素,最新的逐次逼近寄存器模数转换器提供了具有中 等分辨率(<12

‑

bit)的省电解决方案(<10fj/转换步长)。

3.随着分辨率的提高,逐次逼近寄存器模数转换器中传统二进制加权数模转 换器(digital to analog converter,dac)阵列的输入负载电容和面积呈指 数级爆炸式增长,使得超过12位分辨率的良好电容器匹配变得更加困难,从 而导致模数转换器的有效分辨率下降。为了使得数转换器在取得高精度的同 时具有较低的面积开销并且具有良好的性能表现,具有分段式dac架构的逐 次逼近寄存器模数转换器提供了一种有吸引力的解决方案。

4.近年来,随着cmos器件进入纳米尺度区域,在器件可变性增加的情况下, 做到尺寸越来越困难,因此需要校准技术。由于cmos器件尺寸的缩放给数字 电路提供了在密度、速度和集成度方面的明显优势,所以将校准推进到数字 领域是有优势的,并且,数字校准技术相比模拟校准技术,具有集成度高、 面积开销小的特点。为了提高逐次逼近寄存器模数转换器的sndr,各种类型 的数字校准技术已经被提出,这些校准技术可以进一步分为三大类:

5.基于数字输出相关性的数字校准技术,将伪随机噪声(pseudorandom noise, pn)序列叠加注入到输入信号中,然后将其从量化输出中数字地删除,删除 后的余数就是最终的数字输出,然后数字结构为与伪随机噪声序列单独相关 的位,从而指导后续的算法。

6.在基于差异化输入的方法中,每个样本被转换两次,如果adc的输出转移 曲线有不匹配,则两次转换的结果之间的差异为非零,如果adc的输出转移 曲线完全匹配,则两次转换的结果之间不存在差异。由于这些方法中的差分 信号与输入误差源高度相关,因此可以在比pn注入方法少很多样本的情况下 实现校准。

7.基于概率模型的数字校准技术要求逐次逼近寄存器模数转换器在转换结 束(eoc)之后执行额外的m次比较,以便将这些结果用于通过概率模型算法 来估计输入信号的更准确的量化。。

8.三种方法中,前两种方法都修改了模数转换器结构并且时间开销较大,基 于概率模型的数字校准方法具有可移植,不影响模数转换器结构,速度快的 特点,然而传统的基于概率模型的数字校准技术得到的电压余量估计值的范 围是固定的,并且与分辨率无关,限制了残基的估计精度,因此,我们急需 设计一款新型的逐次逼近型模数转换器来克服上述问题。

技术实现要素:

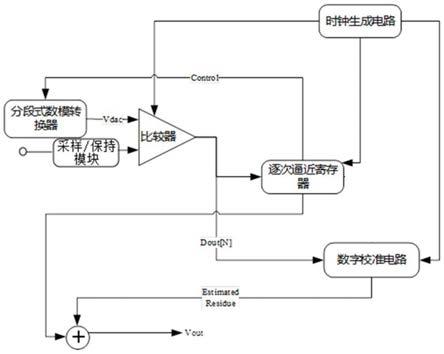

9.为了解决上述问题,本发明提出一种含数字校准的逐次逼近模数转换器, 在逐次逼近控制逻辑电路发出终止量化信号后,比较器被触发额外m次,数 字校准电路通过对m次比较器输出结果进行基于概率模型的分析后,输出预 估的电压余量,dac数字输出与预估电压余量之和,即为最终的输出。通过基 于概率模型的数字校准技术,实现了对采用分段式dac的逐次逼近型模数转 换器的校准,方案简单,有效减小了校准所需的硬件单元,通过将比较器噪 声、电容失配、寄生电容等非理想噪声考虑进去,并在中体现然后在输出端 消除,降低了噪声对模数转换器电路的影响,从而提高了adc的信噪失真比。

10.本发明可通过以下技术方案实现:

11.一种含数字校准的逐次逼近模数转换器,包括比较器,所述比较器的正端 与分段式dac的输出端连接,负端通过采样/保持电路与模拟输入量连接,输 出端与逐次逼近电路、数字校准电路的输入端连接,所述逐次逼近电路的输 出端与数字校准电路连接的输入端连接,还与数字校准电路的输出端一起与 加法器连接,所述加法器的输出即为逐次逼近模数转换器的数字输出量,所 述数字校准电路用于将比较器m次触发结果中出现1的k次结果映射到一个 电压余量的概率估计模型中,输出数字校准码,

12.基于概率估计模型所得到的电压余量函数为其中,g 和b为常数,m为比较次数,d[n]

i

为每次比较器的输出结果。

[0013]

进一步,所述分段式dac使用了一个或多个桥接电容,所述桥接电容为分 数电容或是单位电容的整数倍。

[0014]

进一步,还包括时钟电路,所述时钟电路与比较器、逐次逼近电路、数字 校准电路相连,用于提供时钟信号。

[0015]

本发明有益的技术效果在于:

[0016]

(1)利用图像分割模块的预测结果过滤掉大部分背景像素极大地减少了 待预测预置文本框数量,有利于提升模型效率。

[0017]

(2)对预置文本框边缘上的基准点进行回归预测,有利于检测任意方向 和形状的文本区域。

[0018]

(3)利用尺度变换和空间变换进行数据增强,并使用特征相似性约束策 略从文本图像中提取表达能力强的特征,有利于提升模型对弯曲文本和低分 辨率文本图像识别的鲁棒性。

附图说明

[0019]

图1是本发明的总体结构示意图。

具体实施方式

[0020]

下面结合附图及较佳实施例详细说明本发明的具体实施方式。

[0021]

如图1所示,本发明提供了一种含数字校准的逐次逼近模数转换器,包括 比较器,该比较器的正端与分段式dac的输出端连接,负端通过采样/保持电 路与模拟输入量连接,

对数形式的似然函数为 求出对数似然函数的偏导数令偏导为0,即lnl(g(v

res

‑

b)|d[n]

i

)=0,可以求出估计的电压余量的表达式为其中,g和b为常数,取决于电路中的比较器噪声、电 容失配、寄生电容等非理想特性,m为比较次数,d[n]

i

为每次比较器的输出结 果,输出预估的电压余量与逐次逼近电路的数字输出之和,即为最终的输 出。本公式相比其他公式,估计的余量电压范围更大,可以更好的估计电路 中的非理想特性并从输出端进行处理。

[0029]

公式中的常数g和常数b受以下变量影响:模数转换器的分辨率和电源电 压、热噪声和其他非理想特性。根据公式v

res

=n

th

+q1,其中n

th

是adc热噪声, q1是adc的量化噪声。由于量化噪声的理想范围是可以推导出 电压余量的理想范围是[

‑

lsb,lsb]。

[0030]

为了使估计的电压余量的范围接近理想的范围,v

res

的两个边界值如下所示:

[0031]

通过求解出公式中的未知参数g和b,然后再代入公 式我们可以得到估计的余量电压的最终表达式:

[0032][0033]

在边界情况分析中,为了得出边界条件,通过令等于0或1,可以 将简化为或所以,估计的余量电压的最终范围是

[0034]

上述表格给出了四种数字校准方案的对比。

[0035]

与多数表决相比,本发明提出的算法使用更精细的估计器可以获得更好的 估计,从而获得比较器的符号和幅值信息,而贝叶斯算法要求噪声分布的概 率分布的先验知识。当噪声标准差随着pvt的变化而变化时,贝叶斯算法性 能在变化的条件下是不稳定的,而本发明所提出的方法不需要事先知道噪声 分布的标准差,从而提高了对pvt变化的鲁棒性。与极大似然估计法相比, 本发明可以将残差估计范围从提高到[

‑

lsb,lsb]。

[0036]

并且,传统的极大似然估计法得出的电压余量的估计范围是固定的,并且 与分辨率无关。因此,由于余量电压的固定估计范围,限制了余量电压的估 计精度,使用极大似然估计法对sndr的改进可能不被视为具有提高分辨率的 有效解决方案。而本发明中提出的优化的极大似然估计法,得出的估计的余 量电压的最终范围是

[0037]

当分辨率提高时,极大似然估计法的的范围保持不变且不收敛,而所提 算法的的估计范围更接近实际电压余量的范围,同时有收敛的趋势。由此 可见,本发明中采用的算法在理论上相比现有的基于概率模型的数字校准技 术具有显著优势。

[0038]

该分段式dac使用了一个或多个衰减电容,该衰减电容为单位电容的整数 倍。整个dac阵列被分成三个子阵列,分别是msb、lmsb、lsb,分段比是m:n:l。 每个子阵列中,电容值按照权重比为2的原则设置。对于衰减电容c

a1

,其值 设置为lsb子阵列内所有电容的等效电容。同时,lmsb字阵列最左边的电容 被设置为c

a1

的一半,这确保lsb子数组和c

a1

的串联与c1等价。同理,c

a2

的 值设置为左侧所有电容的等效电容。msb电容子阵列对应的电容c

n+1

~c

n+m

,电 容值为2

i

‑2c

u

,次高电容阵列lmsb子阵列具有n位电容,电容值为2

i

‑1c

u

。在 该结构

中,lsb子阵列使用1位lsb分段来获得最好的dnl。lsb阵列的电容 值为c

u

。

[0039]

另外,还包括时钟电路,该时钟电路与比较器、逐次逼近电路、数字校准 电路相连,用于提供时钟信号。

[0040]

技术人员应当理解,这些仅是举例说明,在不背离本发明的原理和实质的 前提下,可以对这些实施方式做出多种变更或修改,因此,本发明的保护范 围由所附权利要求书限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1