MIPI接口电路及其控制方法、芯片、终端与流程

mipi接口电路及其控制方法、芯片、终端

技术领域

1.本发明涉及集成电路技术领域,尤其涉及一种mipi接口电路及其控制方法、芯片、终端。

背景技术:

2.移动产业处理器接口(mobile industry processor interface,mipi)是mipi联盟发起的为移动应用处理器制定的开放标准和一个规范。

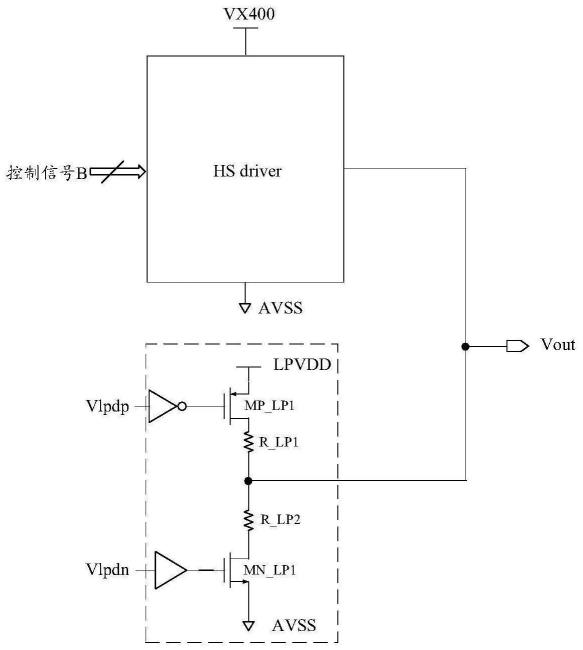

3.在mipi协议d物理层(d-phy)或c物理层(c-phy)中,输出端口可以输出高速(high speed,hs)模式信号和低功耗(low power,lp)模式信号。如图1所示,在传统mipi接口电路中,高速模式信号和低功耗模式信号分别由hs驱动器和lp驱动器(图1中虚线部分所示)驱动。lp模式的输出电压摆幅为0~1.2v,hs模式的输出电压摆幅为0.1~0.3v。在非先进制程下,芯片内部模拟电源电压为1.2v。

4.但是,随着先进制程(如28nm制程)的使用,芯片内部模拟电源电压降低。若hs驱动器使用先进制程的芯片内部管,则因为芯片内部管的源漏耐压小于1.2v,导致发送接口工作在lp模式时hs驱动器内部mos管承受不安全的源漏电压。

技术实现要素:

5.本发明解决的技术问题是发送接口驱动器内部mos管耐压不足的问题。

6.为解决上述技术问题,本发明实施例提供一种mipi接口电路的控制方法,所述mipi接口电路包括:高速驱动器,第一开关单元,第二开关单元和低功耗驱动器;所述第一开关单元的第一端接入电源电压;所述高速驱动器的输入端耦接所述第一开关单元的第二端;所述第二开关单元的第一端耦接所述高速驱动器的输出端,所述第二开关单元的第二端接地;mipi接口电路的控制方法包括:通过第一时序控制信号控制高速驱动器工作在高速模式,并输出高速信号;通过第二时序控制信号控制第一开关单元导通或关断;通过第三时序控制信号控制第二开关单元导通或关断;通过第四时序控制信号控制低功耗驱动器工作在低功耗模式,以在低功耗模式下驱动输出低功耗信号。

7.为解决上述技术问题,本发明实施例还公开了一种mipi接口电路,mipi接口电路包括:第一开关单元,用于在高速模式下导通,所述第一开关单元的第一端接入电源电压;高速驱动器,用于在所述高速模式下驱动输出高速信号,所述高速驱动器的输入端耦接所述第一开关单元的第二端;第二开关单元,用于在所述高速模式下导通,所述第二开关单元的第一端耦接所述高速驱动器的输出端,所述第二开关单元的第二端接地;低功耗驱动器,用于在低功耗模式下驱动输出低功耗信号。

8.可选的,所述mipi接口电路还包括:模式切换单元,用于根据接口电路的工作模式控制所述第一开关单元在高速模式下导通,以及控制所述第二开关单元在所述高速模式下导通。

9.可选的,所述模式切换单元的输出端输出模式控制电压,所述模式控制电压控制

所述第一开关单元和所述第二开关单元在所述高速模式下处于导通状态,在所述低功耗模式下处于关断状态。

10.可选的,所述模式切换单元包括:或非门,所述或非门的第一输入端接入第一控制电压,所述或非门的第二输入端接入第二控制电压;与非门,所述与非门的第一输入端耦接所述或非门的输出端,所述与非门的第二输入端接入第三控制电压;非门,所述非门的输入端耦接所述与非门的输出端,所述非门的输出端输出所述模式控制电压。

11.可选的,所述高速驱动器包括多个并联的高速驱动单元,每一高速驱动单元的输入端耦接对应的第一开关单元的第二端,每一高速驱动单元的输出端耦接对应的第二开关单元的第一端;或者,每一高速驱动单元的输入端耦接对应的第一开关单元的第二端,每一高速驱动单元的输出端耦接同一第二开关单元的第一端;或者,每一高速驱动单元的输入端耦接同一第一开关单元的第二端,每一高速驱动单元的输出端耦接对应的第二开关单元的第一端;或者,每一高速驱动单元的输入端耦接同一第一开关单元的第二端,每一高速驱动单元的输出端耦接同一第二开关单元的第一端。

12.可选的,所述第一开关单元包括第一nmos管,所述第一nmos管的栅极接入第一控制电压,所述第一nmos管的源极耦接所述高速驱动器的输入端,所述第一nmos管的漏极接入电源电压;所述第二开关单元包括第二nmos管,所述第二nmos管的栅极接入第二控制电压,所述第二nmos管的漏极耦接所述高速驱动器的输出端,所述第二nmos管的源极接地。

13.可选的,所述第一nmos管的数量为一个或多个,多个第一nmos管相互并联或相互串联:所述第二nmos管的数量为一个或多个,多个第二nmos管相互并联或相互串联。

14.可选的,所述第一开关单元包括第一电阻,所述第二开关单元包括第二电阻,所述第一电阻的数量为一个或多个,多个第一电阻相互并联或相互串联:所述第二电阻的数量为一个或多个,多个第二电阻相互并联或相互串联。

15.可选的,所述第一开关单元的数量为一个或多个,多个第一开关单元相互并联或相互串联:所述第二开关单元的数量为一个或多个,多个第二开关单元相互并联或相互串联。

16.本发明实施例还公开了一种芯片,所述芯片包括所述mipi接口电路。

17.本发明实施例还公开了一种终端,所述终端包括所述mipi接口电路。

18.与现有技术相比,本发明实施例的技术方案具有以下有益效果:

19.本发明技术方案中,mipi接口电路包括第一开关单元,用于在高速模式下导通,所述第一开关单元的第一端接入电源电压;高速驱动器,用于在所述高速模式下驱动输出高速信号,所述高速驱动器的输入端耦接所述第一开关单元的第二端;第二开关单元,用于在所述高速模式下导通,所述第二开关单元的第一端耦接所述高速驱动器的输出端,所述第二开关单元的第二端接地;低功耗驱动器,用于在低功耗模式下驱动输出低功耗信号。本发明技术方案通过设置第一开关单元和第二开关单元,并在不同模式下处于不同的状态,使得高速驱动器内部管的源漏端电压较小,避免高速驱动器内部mos管耐压不足的问题,从而保证高速驱动器的正常工作,提升驱动性能。

附图说明

20.图1是现有技术中mipi接口电路的结构示意图;

21.图2是本发明实施例一种mipi接口电路的结构示意图;

22.图3是本发明实施例一种mipi接口电路的具体结构示意图;

23.图4是本发明实施例另一种mipi接口电路的具体结构示意图;

24.图5是本发明实施例一种模式切换单元的结构示意图;

25.图6是本发明实施例一种模式切换单元的具体结构示意图;

26.图7是本发明实施例一种信号时序图;

27.图8是本发明实施例另一种信号时序图。

具体实施方式

28.如背景技术中所述,随着先进制程(如28nm制程)的使用,芯片内部模拟电源电压降低。若hs驱动器使用先进制程的芯片内部管,则因为芯片内部管的源漏耐压小于1.2v,导致发送接口工作在lp模式时hs驱动器内部mos管承受不安全的源漏电压。

29.本技术发明人经研究发现,在图1所示传统mipi接口电路中,当接口工作在低功耗模式时,输出电压vout在0~1.2v范围内摆动,此时高速驱动器的输入信号vup=vdn=0(也即控制信号b),高速驱动器内部mos管可能承受1.2v的不安全源漏电压。

30.本发明技术方案通过设置第一开关单元和第二开关单元,并在不同模式下处于不同的状态,使得高速驱动器内部管的源漏端电压较小,避免高速驱动器内部mos管耐压不足的问题,从而保证高速驱动器的正常工作,提升驱动性能。

31.本发明实施例中所称高速模式(也可以称为高速信号模式)用于高速数据传输,例如传输速率为80mbps~1gbps/lane。

32.本发明实施例中所称低功耗模式(也可以称为低功耗信号模式)用于控制,功耗通常较低,例如最大发射频率为10mhz。

33.相应地,本发明实施例中所称高速驱动器是指能够工作在高速模式下的驱动器,输出的信号可以称为高速信号。本发明实施例中所称低功耗驱动器是指能够工作在低功耗模式下的驱动器,输出的信号可以称为低功耗信号。

34.为使本发明的上述目的、特征和优点能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

35.图2是本发明实施例一种mipi接口电路的结构示意图。

36.mipi接口电路包括第一开关单元和第二开关单元,分别用于在高速模式下导通。其中,所述第一开关单元的第一端接入电源电压vx400,第二开关单元的第一端耦接所述高速驱动器20的输出端,所述第二开关单元的第二端接地avss。

37.在图2中,第一开关单元以mos管mn1为例示出,第二开关单元以mos管mn2为例示出。

38.本领域技术人员应当理解的是,除mos管外,第一开关单元和第二开关单元也可以是其他任意可实施的开关器件,本发明实施例对此不作限制。

39.mipi接口电路的输出信号vout可以是高速信号,也可以是低功耗信号。继续参照图2,mipi接口电路还包括高速驱动器20,用于在高速模式下驱动输出高速信号,所述高速驱动器20的输入端耦接mos管mn1的第二端。mipi接口电路还包括低功耗驱动器21(如图2中虚线部分所示),用于在低功耗模式下驱动输出低功耗信号。

40.具体实施中,mos管mn1的漏极接入电源电压vx400,mos管mn1的源极耦接高速驱动器20的一端。mos管mn2的漏极耦接高速驱动器20的另一端,mos管mn2的源极接地avss。mos管mn1的栅极和mos管mn2的栅极接入控制电压vsw。控制电压vsw为低功耗控制相关信号和高速控制相关信号的组合。

41.在具体实施中,mos管mn1和mos管mn2的器件类型可以是芯片内部(core)管,也可以是输入输出(io)管。选择core管则导通电阻小,接口工作在高速模式时性能更好。选择io管则源漏端耐压大,接口工作在低功耗时高速驱动器更安全。mos管mn1和mos管mn2的栅极控制电压可以相同,也可以不同。相关的电源电压只需要保证电路正常工作即可,其他没有限制。

42.需要说明的是,本发明实施例的高速驱动器可以是d-phy的,可以是c-phy的,也可以是d-phy和c-phy联合(c/d-phy combo)的。

43.在本发明一个非限制性的实施例中,mipi接口电路还可以包括模式切换单元(图未示),用于根据接口电路的工作模式控制所述第一开关单元在高速模式下导通,以及控制所述第二开关单元在所述高速模式下导通

44.进一步地,所述模式切换单元的输出端输出模式控制电压(也即前述的控制电压vsw),所述模式控制电压vsw控制所述第一开关单元和所述第二开关单元在所述高速模式下处于导通状态,在所述低功耗模式下处于关断状态。

45.在一个具体实施例中,在图3和图4所示mipi接口电路中,高速驱动器20包括多个并联的高速驱动单元,每一高速驱动单元的输入端耦接对应的第一开关单元的第二端,每一高速驱动单元的输出端耦接对应的第二开关单元的第一端;或者,每一高速驱动单元的输入端耦接对应的第一开关单元的第二端,每一高速驱动单元的输出端耦接同一第二开关单元的第一端;或者,每一高速驱动单元的输入端耦接同一第一开关单元的第二端,每一高速驱动单元的输出端耦接对应的第二开关单元的第一端;或者,每一高速驱动单元的输入端耦接同一第一开关单元的第二端,每一高速驱动单元的输出端耦接同一第二开关单元的第一端。

46.在本发明一个非限制性的实施例中,请参照图5,图5示出了模式切换单元的输入信号和输出信号。模式切换单元的输入信号包括第一控制电压vlpdp、第二控制电压vlpdn、第三控制电压vhsen以及控制信号a(control signals a),模式切换单元的输出信号包括模式控制电压vsw和控制信号b(control signals b),控制信号b用于输入至高速驱动器20。

47.在本发明一个非限制性的实施例中,模式切换单元包括:或非门,所述或非门的第一输入端接入第一控制电压,所述或非门的第二输入端接入第二控制电压;与非门,所述与非门的第一输入端耦接所述或非门的输出端,所述与非门的第二输入端接入第三控制电压;非门,所述非门的输入端耦接所述与非门的输出端,所述非门的输出端输出所述模式控制电压。

48.具体请参照图6,在模式切换单元的具体结构中,或非门o1的第一输入端接入第一控制电压vlpdp,或非门o1的第二输入端接入第二控制电压vlpdn,与非门a1的第一输入端耦接所述或非门o1的输出端,与非门a1的第二输入端接入第三控制电压vhsen。非门n1的输入端耦接所述与非门a1的输出端,所述非门n1的输出端输出所述模式控制电压vsw。

49.进一步地,模式切换单元还可以提供高速驱动器20的控制信号b,也即输入电压vup和vdn。具体地,非门n2的输入端接入第四控制电压vupa,非门n1的输出端耦接与非门a2的第一输入端,与非门a2的第二输入端接入第三控制电压vhsen,与非门a2的输出端输出电压vup。非门n3的输入端接入第五控制电压vdna,非门n3的输出端耦接与非门a3的第一输入端,与非门a3的第二输入端接入第三控制电压vhsen,与非门a3的输出端输出电压vdn。

50.本实施例中,当mipi发送器工作在高速模式(hs mode)时,低功耗驱动器21的输入电压vlpdp和vlpdn均为0(也即第一控制电压和第二控制电压均为0),模式控制电压vsw为电源电压avdd。输入电压vup=vupa(第四控制电压),输入电压vdn=vdna(第五控制电压)。此时,高速驱动器20的控制信号b发挥作用。当mipi发送器工作在低功耗模式(lp mode)时,第三控制电压vhsen=0,模式控制电压vsw=0,输入电压vup=avdd,输入电压vdn=avdd,高速驱动器20的控制信号被拉高,高速驱动器20输出高阻态。

51.图7示出了在高速模式(high speed mode)下,各个信号的时序图。其中,第一控制电压vlpdp和第二控制电压vlpdn为0,第三控制电压vhsen为高电平,控制信号a和控制信号b处于有效状态,控制电压vsw为电源电压avdd。控制信号a和控制信号b处于有效状态可以是指能够控制相应的mos管导通。

52.请一并参照图3,当mipi发送器工作在高速模式(hs mode)时,低功耗驱动器21的输入电压vlpdp和vlpdn(也即第一控制电压和第二控制电压)均为0,低功耗驱动器21输出高阻态。同时模式控制电压vsw为电源电压avdd,mos管mn1和mos管mn2导通,高速驱动器20正常工作。

53.在另一个具体实施例中,请一并参照图4,当mipi发送器工作在高速模式(hs mode)时,低功耗驱动器21的输入电压vlpdp和vlpdn均为0,低功耗驱动器21输出高阻态。同时模式控制电压vsw为电源电压avdd,mos管mn1和mos管mn2导通,高速驱动器20正常工作。

54.图8示出了在低功耗模式(low power mode)下,各个信号的时序图。其中,第一控制电压vlpdp和第二控制电压vlpdn处于有效状态,第三控制电压vhsen为低电平,控制信号a处于有效状态,控制信号b处于无效状态,控制电压vsw为低电平。控制信号b处于无效状态可以是指能够控制相应的mos管关断。

55.请一并参照图3,当mipi发送器工作在低功耗模式(lp mode)时,模式控制电压vsw为0,mos管mn1和mos管mn2关断,高速驱动器20输出高阻态。低功耗驱动器21正常工作。此时,高速驱动器20内部mos管mn4的源端电压略低于电源电压avdd,保证mos管mn4的源漏电压处于安全范围。

56.在另一个具体实施例中,请一并参照图4,当mipi发送器工作在低功耗模式(lp mode)时,模式控制电压vsw为0,mos管mn1和mos管mn2关断,高速驱动器20输出高阻态。低功耗驱动器21正常工作。此时,高速驱动器20内部mos管mn4和mn6的源端电压略低于电源电压avdd,保证mos管mn4和mn6的源漏电压处于安全范围。

57.在本发明一个非限制性的实施例中,所述第一nmos管(也即mos管mn1)的数量为一个或多个,多个第一nmos管相互并联或相互串联:所述第二nmos管(也即mos管mn2)的数量为一个或多个,多个第二nmos管相互并联或相互串联。其中,多个第一nmos管的栅极接入的控制电压可以相同,也可以不同;多个第二nmos管的栅极接入的控制电压可以相同,也可以不同。

58.本发明实施例还公开了一种mipi接口电路的控制方法,mipi接口电路的控制方法为一种时序控制方法,具体可以包括以下步骤:通过第一时序控制信号控制高速驱动器工作在高速模式,并输出高速信号;通过第二时序控制信号控制第一开关单元导通或关断;通过第三时序控制信号控制第二开关单元导通或关断;通过第四时序控制信号控制低功耗驱动器工作在低功耗模式,以在低功耗模式下驱动输出低功耗信号。

59.需要指出的是,本实施例中各个步骤的序号并不代表对各个步骤的执行顺序的限定。

60.在具体实施中,在控制高速驱动器工作在高速模式时,控制第一开关单元和第二开关单元导通;在控制低功耗驱动器工作在低功耗模式时,控制第一开关单元和第二开关单元关断。

61.具体实施中,所述第一时序控制信号可以是前述实施例中的第一控制电压vlpdp、第二控制电压vlpdn、控制信号b以及模式控制电压vsw。

62.所述第二时序控制信号和所述第三时序控制信号可以是前述实施例中的模式控制电压vsw。

63.所述第四时序控制信号可以是前述实施例中的第一控制电压vlpdp、第二控制电压vlpdn、控制信号b以及模式控制电压vsw。

64.可以理解的是,关于所述第一时序控制信号、第二时序控制信号、第三时序控制信号和第四时序控制信号的时序关系可以参照前述实施例的描述,此处不再赘述。

65.本发明实施例还公开了一种芯片,所述芯片包括所述mipi接口电路。所述芯片可以是单一的芯片部件,也可以是芯片模组。

66.本发明实施例还公开了一种终端片,所述终端包括所述mipi接口电路。。所述终端包括但不限于手机、计算机、平板电脑等终端设备。

67.本技术实施例中出现的第一、第二等描述,仅作示意与区分描述对象之用,没有次序之分,也不表示本技术实施例中对设备个数的特别限定,不能构成对本技术实施例的任何限制。

68.虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1