一种在低速时钟下对高速信号的下变频处理系统和方法与流程

1.本发明涉及窄带信号高速采样分析领域,尤其涉及一种在低速时钟下对高速信号的下变频处理系统和方法。

背景技术:

2.目前国内外比较常见fpga的稳定工作时钟一般不会超过300mhz,但是高速信号采样一般都可以达到1g以上,如何在低速时钟下对高速信号进行下变频处理,目前已经有比较成熟的方法,但这些方法一般都要求有丰富的fpga的乘法器资源,与此相应只有中高端fpga才能满足需求。如何在保证各项指标的情况下,在乘法器资源不丰富的中低端fpga上实现低速时钟下对高速信号的进行下变频处理,将是一个需要解决的问题。

技术实现要素:

3.为解决现有的技术问题,本发明提供了一种在低速时钟下对高速信号的下变频处理系统和方法。

4.本发明的具体内容如下:一种在低速时钟下对高速信号的下变频处理系统,包括采样模块和fpga模块,采样模块采集模拟信号后经过模数转换输入fpga模块中,fpga模块包括接口、若干个乘法器、nco(数字振荡器)和累加器;接口将采样后的数据传送到乘法器中,nco与乘法器相连,将接口传送的数据的原始频率转换映射到nco的频率范围,经过nco变频后得到的数据分为实部信号和虚部信号,实部信号和虚部信号分别通过对应的累加器累加。

5.进一步的,采样模块的采样时钟与fpga模块接口的同步时钟是同步同源。

6.进一步的,fpga模块还包括滤波器,累加器与滤波器相连。

7.本发明还公开了一种在低速时钟下对高速信号的下变频处理方法,基于上述任一处理系统,包括如下步骤:

8.s1,确定采样模块采样时钟下的信号与接口的同步时钟下的信号的关系,取nco的数量为4;

9.s2,nco下变频,将接口传送的数据的原始频率转换映射到nco的频率范围,包括实部转换和虚部转换;

10.s3,s2得到的多路实部信号和虚部信号分别通过累加器累加。

11.进一步的,s3中累加器的输出信号分别通过滤波器,得到信号的幅度、相位、频率信息。

12.进一步的,s2中nco的下变频处理采用相移下变频法:

13.设高速ad输出的信号如下:

14.k∈n,n为nco个数;

15.令k=4m+n,m∈n,n=0,1,2,3,则高速ad输出信号为:

16.m∈n,n=0,1,2,3;

17.假设高速ad的时钟是fpga的数据接收的工作时钟的4倍,

18.在fpga的一个时钟的时间间隔,ad将有4个数据刷出,4个fpga的nco产生与之对应的4个信号,分别为:

19.当n=0时,m∈n

20.当n=1时,m∈n

21.当n=2时,m∈n

22.当n=3时,m∈n

23.按照以下公式,把信号按频率分为4类:

24.当0.75*f

s

<f

signal

<f

s

时,f

signal_modify

=f

signal

‑

0.75*f

s

;

25.当0.5*f

s

<f

signal

<0.75*f

s

时,f

signal_modify

=f

signal

‑

0.5*f

s

;

26.当0.25*f

s

<f

signal

<0.5*f

s

时,f

signal_modify

=f

signal

‑

0.25*f

s

;

27.当0<f

signal

<0.25*f

s

时,f

signal_modify

=f

signal

;

28.其中,f

s

为采样模块的采样时钟最大频率,f

signal

为采样模块的采样时钟的频率,f

signal_modify

为修改后的频率;

29.把修改后的频率设置给fpga的nco,分别进行如下虚部和实部转换:

30.当f

req_signal

≥0.75*f

s

,

31.sin_0_out<=sin_0_nco;

32.sin_1_out<=

‑

cos_1_nco;

33.sin_2_out<=

‑

sin_2_nco;

34.sin_3_out<=cos_3_nco;

35.cos_0_out<=cos_0_nco;

36.cos_1_out<=sin_1_nco;

37.cos_2_out<=

‑

cos_2_nco;

38.cos_3_out<=

‑

sin_3_nco;

39.当f

req_signal

≥0.5*f

s

,

40.sin_0_out<=sin_0_nco;

41.sin_1_out<=

‑

sin_1_nco;

42.sin_2_out<=

‑

sin_2_nco;

43.sin_3_out<=cos_2_nco;

44.cos_0_out<=cos_0_nco;

45.cos_1_out<=

‑

cos_1_nco;

46.cos_2_out<=cos_2_nco;

47.cos_3_out<=

‑

cos_3_nco;

48.当f

req_signal

≥0.25*f

s

,

49.sin_0_out<=sin_0_nco;

50.sin_1_out<=cos_1_nco;

51.sin_2_out<=

‑

sin_2_nco;

52.sin_3_out<=

‑

cos_3_nco;

53.cos_0_out<=cos_0_nco;

54.cos_1_out<=

‑

sin_1_nco;

55.cos_2_out<=

‑

cos_2_nco;

56.cos_3_out<=sin_3_nco;

57.当f

req_signal

<0.25*f

s

;

58.cos_0_out<=cos_0_nco;

59.cos_1_out<=cos_1_nco;

60.cos_2_out<=cos_2_nco;

61.cos_3_out<=cos_3_nco;

62.sin_0_out<=sin_0_nco;

63.sin_1_out<=sin_1_nco;

64.sin_2_out<=sin_2_nco;

65.sin_3_out<=sin_3_nco。

66.本实施例的在低速时钟下对高速信号的下变频处理系统和方法,通过对fpga的nco的控制系统,实现了在低速时钟下对高速信号的下变频处理,最大限度的节省了fpga的乘法器资源,在乘法器资源不丰富的中低端fpga上可得到成功应用。在保证各项指标的情况下,大大降低了硬件采购成本,从而提高了整个产品的性价比。

附图说明

67.下面结合附图对本发明的具体实施方式做进一步阐明。

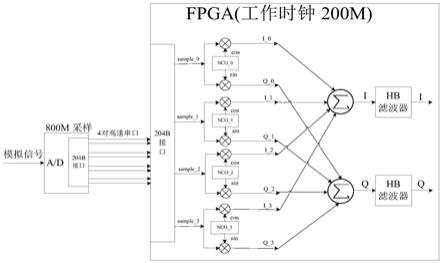

68.图1为本发明的在低速时钟下对高速信号的下变频处理系统的示意图。

具体实施方式

69.结合图1,本发明的本实施例公开了一种在低速时钟下对高速信号的下变频处理系统,包括采样模块和fpga模块,采样模块采集模拟信号后经过模数转换输入fpga模块中,fpga模块包括接口、若干个乘法器、nco、累加器和滤波器;接口将采样后的数据传送到乘法器中,nco与乘法器相连,将接口传送的数据的原始频率转换映射到nco的频率范围,经过nco变频后得到的数据分为实部信号和虚部信号,实部信号和虚部信号分别通过对应的累加器累加,累加器与滤波器相连,累加后的信号通过滤波器滤波。采样模块的采样时钟与fpga模块接口的同步时钟是同步同源。

70.基于该下变频处理系统,本实施例还公开一种下变频处理方法,包括如下步骤:

71.s1,确定采样模块采样时钟下的信号与接口的同步时钟下的信号的关系,一般是4倍关系,所以nco的数量为4;

72.s2,nco下变频,将接口传送的数据的原始频率转换映射到nco的频率范围,包括实部转换和虚部转换;

73.s3,s2得到的多路实部信号和虚部信号分别通过累加器累加。

74.s3中累加器的输出信号分别通过滤波器,得到信号的幅度、相位、频率信息。

75.根据nco的数量n,将采样的数据按表1进行相移下变频处理。

76.设高速ad输出的信号如下:

77.k∈n,n为nco个数;

78.令k=4m+n,m∈n,n=0,1,2,3

79.m∈n,n=0,1,2,3

80.假设高速ad的时钟是fpga的数据接收的工作时钟的4倍,则fpga的一个时钟的时间间隔,ad将有4个数据刷出,所以我们需要4个fpga的nco产生与之对应的4个信号:

81.当n=0时,m∈n

82.当n=1时,m∈n

83.当n=2时,m∈n

84.当n=3时,m∈n

85.而本实施例的方法,未频率变换法,假设高速ad的时钟是fpga的数据接收的工作时钟的4倍,按照以下公式1,把信号按频率分为4类:

86.当0.75*f

s

<f

signal

<f

s

时,f

signal_modify

=f

signal

‑

0.75*f

s

;

87.当0.5*f

s

<f

signal

<0.75*f

s

时,f

signal_modify

=f

signal

‑

0.5*f

s

;

88.当0.25*f

s

<f

signal

<0.5*f

s

时,f

signal_modify

=f

signal

‑

0.25*f

s

;

89.当0<f

signal

<0.25*f

s

时,f

signal_modify

=f

signal

;

90.其中,f

s

为采样模块的采样时钟最大频率,f

signal

为采样模块的采样时钟的频率,f

signal_modify

为修改后的频率;

91.把修改后的频率设置给fpga的nco,根据以下表1进行如下转换(其中的<=表示对应关系):

92.表1虚部和实部转换对应关系

93.[0094][0095]

本实施例优选的,以一个ad采样频率为800mhz,采样后的数据采用204b接口传送,采样模块的204b接口和fpga的204b接口用200mhz时钟同步,并且200mhz同步时钟和800mhz采样时钟是同步同源,相应的fpga的工作时钟设置为200mhz为例。

[0096]

首先,理出800mhz下的信号与200mhz下的信号的关系,参见表1为800m时钟下输出的信号与200m时钟下输出的信号的等价性,由此可知,利用fpga时间并行特性,800mhz时钟下输出的信号可以由4个工作在200mhz时钟下并行的nco产生。即fs为800mhz,f

signal

的范围是0~800mhz,f

nco

为200mhz,n为4;

[0097]

由于f

signal

的范围是0~800mhz,而fpga的nco输出的频率范围是0~200mhz,所以需要先进行频率转换,把信号频率从0~800mhz映射到0~200mhz,参见表2,表3,表4,表5,表6,表7,根据下变频方法,通过转换后,信号的原始频率都转换为可在200m工作时钟下的nco的可设置的频率。

[0098]

表1 200mhz~400mhz虚部转换

[0099][0100]

表2 200mhz~400mhz实部转换

[0101]

[0102][0103]

表3 400mhz~600mhz虚部转换

[0104][0105]

表4 400mhz~600mhz实部转换

[0106]

[0107][0108]

表5 600mhz~800mhz虚部转换

[0109][0110]

表6 600mhz~800mhz实部转换

[0111]

[0112][0113]

经过nco下变频后,得出4路实部信号和4路虚部信号,分别通过累加器(等效于cic滤波器),得到了200m时钟下的实数信号和虚部信号;累加器输出信号通过hb滤波器后,可以很方便求出信号的幅度、相位、频率等信息。

[0114]

本实施例的在低速时钟下对高速信号的下变频处理系统和方法,通过对fpga的nco的控制系统,实现了在低速时钟下对高速信号的下变频处理,最大限度的节省了fpga的乘法器资源,在乘法器资源不丰富的中低端fpga上可得到成功应用。在保证各项指标的情况下,大大降低了硬件采购成本,从而提高了整个产品的性价比。

[0115]

在以上的描述中阐述了很多具体细节以便于充分理解本发明。但是以上描述仅是本发明的较佳实施例而已,本发明能够以很多不同于在此描述的其它方式来实施,因此本发明不受上面公开的具体实施的限制。同时任何熟悉本领域技术人员在不脱离本发明技术方案范围情况下,都可利用上述揭示的方法和技术内容对本发明技术方案做出许多可能的变动和修饰,或修改为等同变化的等效实施例。凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所做的任何简单修改、等同变化及修饰,均仍属于本发明技术方案保护的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1