用于固态驱动器的印刷电路板结构的制作方法

1.本发明的实施例涉及一种印刷电路板结构。

背景技术:

2.计算机环境范例已经转变为可以随时随地使用的普适计算系统。因此,诸如移动电话、数码相机和笔记本电脑的便携式电子装置的使用已经迅速增加。这些便携式电子装置通常使用具有存储器装置(即,数据存储装置的存储器系统。数据存储装置用作便携式电子装置的主存储器装置或辅助存储器装置。

3.诸如数据存储装置的电子装置可以利用印刷电路板(pcb)实施。

技术实现要素:

4.本发明的方面包括一种用于诸如固态驱动器的数据存储装置的印刷电路板(pcb)结构。

5.一方面,一种固态驱动器包括:顶层和底层,顶层和底层中的每一层包括用于操作固态驱动器的多个组件;多个中间层,被配置成使得电信号能够在顶层和底层上的组件之间传递,多个中间层中的一层包括相对于其他平面中的每一个具有高电压的电源平面;以及接地笼(ground cage),被配置成屏蔽噪声高电压电源平面,这极大地减少了联接到附近或相邻层周围的受害电源平面或信号迹线的噪声。

6.另一方面,一种用于固态驱动器的印刷电路板,包括:顶层和底层,顶层和底层中的每一层包括用于操作固态驱动器的多个组件;以及多个中间层,设置在顶层和底层之间,并且被配置成使得电信号能够在顶层和底层上的组件之间传递。多个中间层包括:第一中间层,包括具有高电压的高电源平面(100)以及与高电源平面相邻的第一和第二信号迹线(200a、200b);第二中间层(400),形成在第一中间层上方和顶层下方,并且包括具有低于高电压的低电压的第一低电源平面(410或430);第三中间层(500),其形成在第一中间层下方和底层上方,并且包括具有低电压的第二低电源平面(510或530);以及接地笼(300a、300b、300c),被配置成包围高电源平面,使得高电源平面与第一和第二信号迹线中的每一个之间的电容和电感路径以及高电源平面与第一和第二低电源平面中的每一个之间的电容和电感路径被阻断。

7.通过以下描述,本发明的其他方面将变得显而易见。

附图说明

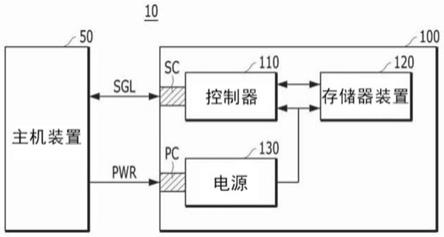

8.图1是示出数据处理系统的示例的框图。

9.图2是示出存储装置的电源的示例的示图。

10.图3a和3b是分别示出在电气路径中发生的电压振铃噪声和电流涌入尖峰的示图。

11.图4是示出多层印刷电路板的示例的示图。

12.图5是示出具有噪声电源平面和相邻平面或迹线的印刷电路板(pcb)部分的示例

的截面图。

13.图6a和6b示出通过静电场的电容耦合路径及其等效电路。

14.图7a和7b示出通过静电场的电感耦合路径及其等效电路。

15.图8a和8b是示出根据本发明实施例的印刷电路板(pcb)的结构的示图。

16.图9是示出根据本发明实施例的存储装置的印刷电路板(pcb)结构的截面图。

17.图10a是根据本发明实施例的存储装置的印刷电路板(pcb)结构(如图9所示的pcb结构)的三维(3d)立体图。

18.图10b是图10a所示的印刷电路板(pcb)结构沿y轴的截面图。

19.图10c是图10a所示的印刷电路板(pcb)结构沿x轴的截面图。

具体实施方式

20.下面参考附图更详细地描述各个实施例。然而,本发明可以以不同形式实施,因此不应被解释为限于本文所阐述的实施例。相反,提供这些实施例使得本公开是彻底且完整的,并且向本领域技术人员充分传达了本发明的范围。此外,本文中对“实施例”、“另一实施例”等的参考不一定仅针对一个实施例,并且对任何此类短语的不同参考不一定针对相同的实施例。在整个本公开中,相同的附图标记在本发明的附图和实施例中指代相同的部分。

21.本发明可以以多种方式实施,包括作为进程;设备;系统;在计算机可读存储介质上实现的计算机程序产品;和/或处理器,例如适于运行存储在联接到处理器的存储器上的指令和/或由联接到处理器的存储器提供的指令的处理器。在本说明书中,这些实施方式或本发明可以采取的任何其他形式可称为技术。一般来说,在本发明的范围内,可以改变所公开的进程的步骤的顺序。除非另有说明,否则被描述为适于执行任务的、诸如处理器或存储器的组件可以被实施为临时被配置成在给定时间执行该任务的通用组件或者被制造为执行该任务的特定组件。如本文所使用的,术语“处理器”等是指适于处理诸如计算机程序指令的数据的一个或多个装置、电路和/或处理内核。

22.下面结合示出本发明各个方面的附图提供本发明实施例的详细描述。结合这些实施例描述本发明,但本发明不限于任何实施例。本发明的范围仅由权利要求书限定。本发明涵盖权利要求书范围内的许多替代方案、修改和等效方案。在以下描述中阐述了许多具体细节,以提供对本发明的透彻理解。提供这些细节是为了示例;可以根据权利要求书来实践本发明,而不需要这些特定细节中的部分或全部。为清楚起见,与本发明相关的技术领域中已知的技术材料未被详细描述,以避免不必要地模糊本发明。

23.图1是示出数据处理系统10的示例的框图。

24.参考图1,数据处理系统10可以包括主机装置50和存储装置(其可以实施为存储器系统)100。存储装置100可以接收来自主机装置50的请求,并且响应于接收到的请求而操作。例如,存储装置100可以存储待由主机装置50访问的数据。

25.主机装置50可以利用各种电子装置中的任一种来实施。在各个实施例中,主机装置50可以包括诸如以下的电子装置:台式计算机、工作站、三维(3d)电视、智能电视、数字音频记录器、数字音频播放器、数字图片记录器、数字图片播放器和/或数字视频记录器和数字视频播放器。在各个实施例中,主机装置50可以包括诸如以下的便携式电子装置:移动电话、智能电话、电子书、mp3播放器、便携式多媒体播放器(pmp)和/或便携式游戏机。

26.存储装置100可以包括控制器110、存储器装置120和电源130。控制器110可以通过信号连接器sc与主机装置50交换信号sgl(其可以表示多个信号)。信号sgl可以包括命令、地址和数据。根据主机装置50和存储装置100之间的接口方案,信号连接器sc可以被配置为各种类型的连接器中的任一种。

27.控制器110可以响应于来自主机装置50的信号sgl来控制存储器装置120的全部操作。例如,控制器110可以控制存储器装置120以执行一个或多个擦除操作、编程操作和读取操作。

28.存储器装置120可以通过一个或多个通道联接到控制器110。存储器装置120可以利用多个非易失性存储器装置来实施。控制器110和存储器装置120可以利用诸如固态驱动器(ssd)和存储卡的各种存储装置中的任一种来实施。

29.电源130可以向存储装置100中的组件提供通过电源连接器pc从主机装置50输入的电力pwr。

30.图2是示出存储装置100的电源130的示例的示图。

31.参考图2,电源130可以包括多个电容器c1至cn、升压调节器ru和降压调节器rd。尽管未在图1中示出,但存储装置100可以进一步包括联接到电源130的电源开关140和电源控制器150,如图2所示。

32.电源开关140可以在电源控制器150的控制下提供正常电力传输路径或失电保护(plp)传输路径。在正常电力传输路径中,从主机装置50提供的电力通过电源开关140、电源控制器150以及升压调节器ru被传输至多个电容器c1至cn。升压调节器ru可以将来自主机装置50的低输入电压转换为高电压(例如,35v或更高)。高电压可以用于对多个电容器c1至cn充电。电源130可以包括在电压调节器ru、rd和多个电容器c1至cn之间传递电力(即高电压)的第一路径(即v_high_bus),以及通过电源开关140在电压调节器ru、rd和主机装置50之间传递电力(即低电压)的第二路径(即v_low_bus)。此外,电源130可以包括将信号从电源控制器150传递到电压调节器ru、rd的第三路径。

33.当从主机装置50到存储装置100的电力被中断或切断时,多个电容器c1到cn可以被放电,并且其中存储的能量可以通过plp传输路径传输,该plp传输路径包括降压调节器rd、电源开关140、电源控制器150和内部电源调节器。存储装置100可以使用多个电容器作为电源,将数据从控制器110的内部存储器(例如,易失性存储器)备份到存储器装置120(例如,nand闪存装置)。

34.因此,多个电容器c1至cn可以形成电容器阵列,以提供足够的能量来维持用于从控制器110到存储器装置120的数据备份传输的电源轨电压。电容器阵列或大容量电容器可以用作存储装置100的失电保护(plp)电容器。升压调节器ru可以利用包括开关组件(例如,fet)的电压调节器来实施,电压调节器通常用于高功率转换效率。升压调节器ru可以通过电源路径v_high_bus连接至plp电容器。电力路径v_high_bus和v_low_bus可以通过使用一个或多个电源平面或层,在存储装置100(例如,固态驱动器(ssd))的印刷电路板(pcb)中实施。

35.寄生电容和寄生电感可以存在于电气路径上和电气组件内。由于电压调节器的开关组件以高频(例如1mhz或更高)打开和关闭,因此突然改变电流路径,可能会出现几百mhz的强烈电压振铃噪声,并且在plp电容器的充电过程和放电过程中也可能出现明显的高电

流涌入尖峰,如图3a和3b所示。

36.图4是示出多层印刷电路板(pcb)的示例的示图。

37.参考图4,pcb可以具有多层结构。在所示出的示例中,pcb具有12层,包括顶部导体层、底部导体层和设置在顶部导体层和底部导体层之间的十个导体层l02至l11。表面介电层可以设置在pcb的上表面和顶部导体层之间,另一表面介电层可以设置在pcb的下表面和底部导体层之间。特定电路的组件(例如,图2的电源130)可以安装在顶部导体层和底部导体层上。第二导体层l02至第十一导体层l11中的每一个可以传递电力或信号,或者可以形成接地。在示例中,第二导体层l02至第十一导体层l11的使用如下表1所示:

[0038][0039][0040]

在表1中,每条迹线可以是用于传递信号的细铜导体,并且每个平面可以是用于传递电力的粗铜导体。

[0041]

进一步,pcb可以包括上表面和下表面之间的通孔th1、th2,以及用于在层之间进行电气连接的垂直过孔v1、v2、v3。

[0042]

如上所述,在pcb上,相邻层之间以及相同层上的相邻电源平面或信号迹线之间可能存在结构互电容和结构互电感。换言之,某个电源平面(即,干扰源)可能导致电源噪声耦合到其他电源平面或信号迹线(即,受害者)。已经发现电源噪声耦合情况在电压可能比pcb上的其余电路区域高数倍的电路区域中更糟。例如,当利用如图4所示的具有多层的pcb实施图2的电源130时,发明人观察到路径v_high_bus的电源平面导致电压振铃噪声和电流涌入尖峰出现在其他平面或迹线中。这种电源噪声耦合污染是不可容忍的,因为它最终将导致信号完整性问题,并导致存储装置的系统故障。

[0043]

图5是示出具有噪声电源平面和相邻平面或迹线的印刷电路板(pcb)部分的示例的截面图。

[0044]

参考图5,pcb可以包括可单独地或共同地被称为干扰源的噪声电源平面以及为受害者的相邻平面或迹线。在所示出的示例中,pcb可以包括在pcb上电连接在一起的3个噪声

电源平面。根据pcb的具体设计,每个噪声电源平面可以是一个或多个层。受害平面可以与噪声电源平面位于相同层或相邻层。干扰源平面和受害平面之间的间隙可以利用介电材料填充。

[0045]

以下参考图6a至7b分析从干扰源到受害者的噪声耦合。

[0046]

图6a和图6b示出通过静电场的电容耦合路径及其等效电路。耦合路径可以在相同层上(图6a),也可以在相邻层之间(图6b)。受害平面或迹线上的耦合电压可以表示为:

[0047]

vn=jωcrvs

ꢀꢀꢀꢀꢀꢀ

(1)

[0048]

在等式(1)中,ω=2πf,f是振铃噪声频率,c是耦合路径互电容,r是负载阻抗,vs是电源平面的电压振铃噪声(例如,图2中plp电容器的电源平面v_high_bus)。

[0049]

从等式(1)可以看出,当c足够大时,高频和高压振铃噪声可以被耦合到受害平面或迹线,如vn。

[0050]

图7a和7b示出通过静电场的电感耦合路径及其等效电路。耦合路径可以在相同层上(图7a),也可以在相邻层之间(图7b)。受害平面或迹线上的耦合电压可以表示为:

[0051]

vn=jωmis

ꢀꢀꢀ

(2)

[0052]

在等式(2)中,ω=2πf,f是涌入尖峰频率,m是耦合路径互电感,is是电源平面的电流涌入尖峰(例如,图2中plp电容器的电源平面v_high_bus)。

[0053]

从等式(2)可以看出,当m足够大时,高频和高电流尖峰可以耦合到受害平面或迹线,如vn。

[0054]

如上所述,在印刷电路板中,存储装置(例如,图2中的电源130)的电气路径中可能出现电压振铃噪声和电流涌入尖峰。因此,希望提供一种能够避免印刷电路板(pcb)中的高能振铃噪声和电流涌入尖峰的结构。实施例提供了一种用于封装作为干扰源的一个或多个高压电源平面的pcb结构,其中高压电源平面由多个接地平面包围。因此,到受害平面或迹线的电源噪声耦合路径被有效地阻断或终止。

[0055]

图8a和8b是示出根据本发明实施例的印刷电路板(pcb)的结构的示图。

[0056]

参考图8a和图8b,pcb可以包括作为干扰源的高压电源平面100以及统称为受害元件的两个相邻平面或迹线200a、200b。在一些实施例中,高压电源平面100可以是调节器ru、rd和plp电容器之间的电力路径v_high_bus,如图2中的电源130所示。两个相邻平面或迹线200a、200b可以是调节器ru、rd和电源开关140之间的电力路径v_low_bus,或是调节器ru、rd和电源控制器150之间的信号路径。

[0057]

高压电源平面100可以由外壳组件包围(或封装)。在一些实施例中,外壳组件可以利用包括多个接地平面的接地笼实施。在所示出的示例中,外壳组件可以包括第一接地平面300a、第二接地平面300b和第三接地平面300c。第一接地平面300a可以与高压电源平面100(即,噪声电源平面)布置在相同层。第二地平面300b可以布置在第一地平面300a的上方。第三地平面300c可以布置在第一地平面300a的下方。第一接地平面300a可以水平地包围高压电源平面100的外围,第二接地平面300b和第三接地平面300c可以配合以垂直地包围高压电源平面100。换言之,第一接地平面300a至第三接地平面300c可以形成接地笼以包围高压电源平面100。高压电源平面100可以包括一个或多个电源平面。因此,实施例提供了一种特殊的pcb结构,以有效地屏蔽一个或多个高压平面,从而可以在不增加额外组件或成本的情况下将高能振铃噪声和电流涌入尖峰限制在该结构内。这种特殊的pcb结构可以称

为“夹层pcb结构”。因此,作为干扰源的噪声电源平面和作为受害元件的电源平面或迹线之间的互电容和互电感可以被最小化。

[0058]

图9是示出根据本发明实施例的存储装置(例如ssd)的印刷电路板(pcb)结构的截面图。

[0059]

参考图9,pcb结构可以包括第一层、第二层400和第三层500。第一层中的每一层可以包括被配置为作为高压电源平面(即干扰源)传递电力的第一平面,以及与第一平面相邻的第二和第三平面(即受害者)。作为示例且不受任何限制,第一层可以包括3个第一层,包括顶部第一层、中间第一层和底部第一层。顶部第一层可以包括第一平面100-1、第二平面200a-1和第三平面200b-1。中间第一层可以包括第一平面100-2、第二平面200a-2和第三平面200b-2。底部第一层可以包括第一平面100-3、第二平面200a-3和第三平面200b-3。在一些实施例中,第二平面和第三平面中的每一个可以包括传递电力的电源平面或传递信号的信号迹线。

[0060]

第二层400可以形成在顶部第一层之上。例如,第二层400可以包括多个平面410、420、430。第三层500可以形成在底部第一层的下方。例如,第三层500可以包括多个平面510、520、530。在一些实施例中,第二层400和第三层500中的每一层可以包括传递电力的电源平面或传递信号的迹线。

[0061]

pcb结构可以包括外壳组件,该外壳组件包括接地笼,该接地笼被配置为水平和垂直地包围形成干扰源的第一平面100-1、100-2、100-3。在一些实施例中,接地笼可以包括水平布置和垂直布置的多个接地平面,从而阻断干扰源和受害者之间的电容和电感路径。

[0062]

接地笼可以包括第一平面100-1与第二平面200a-1之间的第四平面300a-11,以及第一平面100-1与第三平面200b-1之间的第五平面300a-12。接地笼可以包括第一平面100-2与第二平面200a-2之间的第四平面300a-21,以及第一平面100-2与第三平面200b-2之间的第五平面300a-22。接地笼可以包括第一平面100-3与第二平面200a-3之间的第四平面300a-31,以及第一平面100-3和第三平面200b-3之间的第五平面300a-32。此外,接地笼可以包括形成在顶部第一层和第二层400之间的第四层300b,以及形成在底部第一层和第三层500之间的第五层300c。接地笼的多个接地平面可以电耦合。

[0063]

在一些实施例中,可以调整层和平面的厚度和宽度,使得互耦电容和互耦电感最小化。

[0064]

对于每个第一层,第一至第五平面可以具有相同的厚度t2。对于顶部第一层,第一平面100-1与第二平面200a-1之间的第四平面300a-11以及第一平面100-1与第三平面200b-1之间的第五平面300a-12可以具有厚度t2。第四平面300a-11和第五平面300a-12可以具有相同的宽度w2。对于中间第一层,第一平面100-2与第二平面200a-2之间的第四平面300a-21以及第一平面100-2与第三平面200b-2之间的第五平面300a-22可以具有厚度t2。第四平面300a-21和第五平面300a-22可以具有相同的宽度w2。对于底部第一层,第一平面100-3与第二平面200a-3之间的第四平面300a-31以及第一平面100-3与第三平面200b-3之间的第五平面300a-32可以具有厚度t2。第四平面300a-31和第五平面300a-32可以具有相同的宽度w2。

[0065]

第四层300b和第五层300c可以具有相同的厚度t1并且可以具有相同的宽度w1。

[0066]

pcb结构可以包括各层之间的间隙以及每层中的平面之间的间隙。在一些实施例

中,这些间隙可以利用介电材料(例如,环氧层压材料)填充。

[0067]

顶部第一层可以包括第一平面100-1和第四平面300a-11之间的长度为g2的第一间隙,第一平面100-1和第五平面300a-12之间的长度也为g2的第二间隙,第二平面200a-1和第四平面300a-11之间的第三间隙以及第三平面200b-1和第五平面300a-12之间的第四间隙。中间第一层可以包括第一平面100-2和第四平面300a-21之间的第一间隙,第一平面100-2和第五平面300a-22之间的第二间隙,第二平面200a-2和第四平面300a-21之间的第三间隙以及第三平面200b-2和第五平面300a-22之间的第四间隙。底部第一层可以包括第一平面100-3和第四平面300a-31之间的第一间隙,第一平面100-3和第五平面300a-32之间的第二间隙,第二平面200a-3和第四平面300a-31之间的第三间隙以及第三平面200b-3和第五平面300a-32之间的第四间隙。

[0068]

pcb结构可以包括顶部第一层和第四层300b之间的长度为g1的第五间隙,第二层400和第四层300b之间的第六间隙,底部第一层和第五层300c之间的第七间隙以及第三层500和第五层300c之间的第八间隙。

[0069]

在一些实施例中,可以调整层之间的间隙和平面之间的间隙,以使互耦电容和互耦电感最小化。在一些实施例中,pcb结构可以具有如图4所示的多个层,并且多个层的厚度可以小于1mm,其中g1小于50μm,g2小于100μm,使得高频下的高压振铃噪声和高电流涌入尖峰可以垂直和水平跨越间隙,到达受害平面或迹线。

[0070]

图10a是根据本发明实施例的存储装置的印刷电路板(pcb)结构,即图9所示的pcb结构的三维(3d)立体图。pcb结构以相对于xyz坐标系的方式被显示。图10b是图10a所示的印刷电路板(pcb)结构沿y轴的截面图。图10c是图10a所示的印刷电路板(pcb)结构沿x轴的截面图。

[0071]

参考图10a至10c,高压电源平面100-1、100-2、100-3由包括多个接地平面300a-10、300a-20、300a-30、300b、300c的外壳组件包围。外壳组件被设置和配置成阻止或显著减少从高压电源平面100-1、100-2、100-3到受害电源平面或信号迹线200b-1、200b-2、200b-3、410、420、510、520的噪声耦合(即,电压振铃噪声和电流涌入尖峰)。

[0072]

如上所述,实施例提供了一种能够避免诸如存储装置(例如ssd)的电子装置的印刷电路板(pcb)中的电源噪声耦合(例如,高能振铃噪声和电流涌入尖峰)的结构。根据实施例,pcb结构通过使用多个接地平面封装一个或多个高压电源平面。因此,实施例阻止从高压电源平面到受害电源平面或信号迹线的电源噪声耦合。

[0073]

尽管为了清楚和理解的目的,已经对上述实施例进行了一些详细的说明和描述,但本发明不限于所提供的细节。如本领域技术人员根据前述公开将理解的,有许多实现本发明的替代方法。因此,所公开的实施例是说明性的,而不是限制性的。本发明旨在涵盖落入权利要求书范围内的所有修改方案和替代方案。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1