用于倍频的时钟产生器的制作方法

1.本发明涉及一种时钟产生器,尤其涉及一种可用于倍频的时钟产生器。

背景技术:

2.在传统电路系统中,具有倍数频率的时钟信号通常是通过锁相环(phase-locked loop,pll)或延迟锁相环(delay-locked loop,dll)来产生。锁相环一般是由相位侦测器、电荷泵(charge pump)、回路滤波器(loop filter)、压控振荡器(voltage-controlled oscillator,vco)、及分频器(frequency divider)所组成,而延迟锁相环一般是由相位侦测器、电荷泵、回路滤波器、及压控延迟线所组成。这些电路方块较为复杂,且往往需要高功耗并占用大量电路面积。因此,实有必要提出一种新式的时钟产生器,可在避免使用锁相环或延迟锁相环的情况下产生具有倍数频率的输出时钟信号,从而节省功耗及电路面积。

技术实现要素:

3.因此,本发明的主要目的即在于提供一种用于倍频的时钟产生器,以解决上述问题。

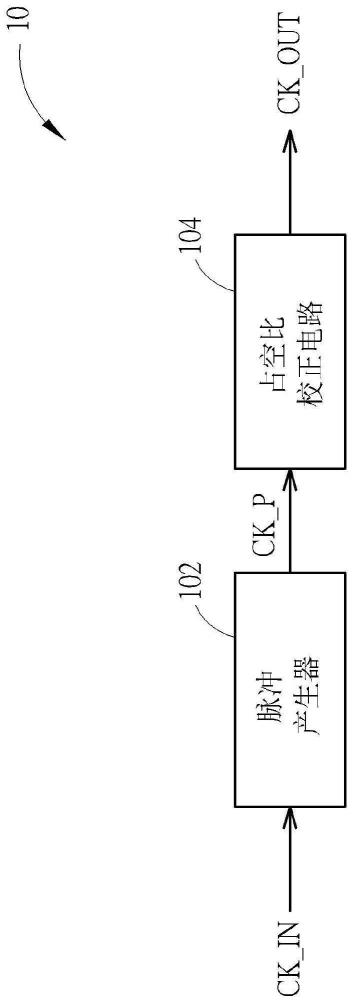

4.本发明的一实施例公开了一种时钟产生器,其包括一脉冲产生器及一占空比校正(duty cycle correction,dcc)电路。该脉冲产生器用来接收一输入时钟信号,并根据该输入时钟信号来产生一脉冲信号。该占空比校正电路耦接于该脉冲产生器,用来调整该脉冲信号的一占空比以产生一输出时钟信号。

5.本发明的另一实施例公开了一种时钟产生器,其包括串接的多个倍频器(frequency doubler),其中每一倍频器包括一脉冲产生器及一占空比校正电路。该脉冲产生器用来接收一输入时钟信号,并根据该输入时钟信号来产生一脉冲信号。该占空比校正电路耦接于该脉冲产生器,用来调整该脉冲信号的一占空比以产生一输出时钟信号。

附图说明

6.图1为本发明实施例一时钟产生器的示意图。

7.图2为图1中的时钟产生器的信号波形图。

8.图3为本发明实施例一时钟产生器的示意图。

9.图4为图3中的时钟产生器的信号波形图。

10.图5示出了脉冲产生器的一种详细实施方式。

11.图6示出了占空比校正电路的一种详细实施方式。

12.图7示出了脉冲间隔侦测器的一种详细实施方式。

13.图8为脉冲间隔侦测器中产生的延迟脉冲的波形图。

14.图9示出了可用来实现延迟单元的一种示例性反向器。

15.图10~12示出了占空比校正电路的其它详细实施方式。

16.其中,附图标记说明如下:

17.10、30

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

时钟产生器

18.102

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

脉冲产生器

19.104

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

占空比校正电路

20.ck_in

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

输入时钟信号

21.ck_p、ck_p1、ck_p2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

脉冲信号

22.ck_out、ck_out1、ck_out2

ꢀꢀꢀꢀꢀꢀꢀꢀ

输出时钟信号

23.fd1、fd2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

倍频器

24.d1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

延迟单元

25.502

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

异或门

26.ck_d

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

延迟信号

27.602

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

脉冲间隔侦测器

28.604

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

sr锁存器

29.612

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一延迟电路

30.614

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

控制逻辑

31.616

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二延迟电路

32.p_d

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

侦测脉冲

33.p_out

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

输出脉冲

34.td

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

延迟时间

35.t1、t2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

晶体管

36.c1、c2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电流源

37.dc1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

驱动单元

38.1002

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

放大器

39.1004

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

运算元

40.f1、f2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

滤波器

41.v_f、v_f1、v_f2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

滤波信号

42.ck_ref

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

参考时钟

43.v_ref

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

参考电压

44.v_err

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

反馈信号

45.1100

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

单端转差分转换器

46.1200

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

反向器

47.ck_p

’ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

反向脉冲信号

具体实施方式

48.请参考图1,图1为本发明实施例一时钟产生器10的示意图。如图1所示,时钟产生器10包括一脉冲产生器102及一占空比校正(duty cycle correction,dcc)电路104。脉冲产生器102可用来接收一输入时钟信号ck_in,并根据输入时钟信号ck_in来产生一脉冲信号ck_p。占空比校正电路104可从脉冲产生器102接收脉冲信号ck_p,并调整脉冲信号ck_p的占空比以产生一输出时钟信号ck_out。

49.图2为图1中的时钟产生器10的信号波形图,其示出了输入时钟信号ck_in、脉冲信

号ck_p及输出时钟信号ck_out的波形。如图2所示,输入时钟信号ck_in的占空比等于50%,脉冲信号ck_p包括多个脉冲,其发生在输入时钟信号ck_in转态的时间点。当脉冲信号ck_p产生之后,可通过占空比校正电路104来调整或修改脉冲信号ck_p的占空比,从而产生输出时钟信号ck_out。输出时钟信号ck_out的占空比也等于50%,且输出时钟信号ck_out的频率为输入时钟信号ck_in的频率的两倍。

50.因此,本发明的时钟产生器仅包括一脉冲产生器及一占空比校正电路,相较于锁相环(phase-locked loop,pll)或延迟锁相环(delay-locked loop,dll)的电路结构而言,本发明的时钟产生器的结构较为简单,同时能够达到功耗低和面积小的优点。举例来说,本发明的时钟产生器可省略压控振荡器(voltage-controlled oscillator,vco)或压控延迟线所需要的大量面积。需注意的是,本发明的时钟产生器可产生的频率需限制在2的幂次方的倍数。举例来说,若输入时钟信号的频率为10百万赫兹(mhz)时,所产生的输出时钟信号的频率可以是20、40或80百万赫兹等等。

51.在一实施例中,可复制时钟产生器10的电路结构并将其依序串接以产生更高倍率的输出频率。请参考图3,图3为本发明实施例一时钟产生器30的示意图。如图3所示,时钟产生器30包括多个倍频器fd1、fd2、

…

等,其中每一倍频器的电路结构均相同于图1所示的时钟产生器10。也就是说,每一倍频器都包括一脉冲产生器及一占空比校正电路。双倍的频率可通过一个倍频器产生,四倍的频率可通过两个倍频器产生,八倍的频率可通过三个倍频器产生,并以此类推。

52.图4为图3中的时钟产生器30的信号波形图,其示出了输入时钟信号ck_in、脉冲信号ck_p1及ck_p2、以及输出时钟信号ck_out1及ck_out2的波形。更明确来说,藉由输入时钟信号ck_in的接收,倍频器fd1可产生脉冲信号ck_p1,并产生具有双倍频率的输出时钟信号ck_out1。藉由输出时钟信号ck_out1的接收,倍频器fd2可产生脉冲信号ck_p2,并产生具有四倍频率的输出时钟信号ck_out2。

53.在本发明的时钟产生器中,脉冲产生器及占空比校正电路均可通过任意方式来实现。请参考图5,图5示出了脉冲产生器102的一种详细实施方式。如图5所示,脉冲产生器102包括一延迟单元d1及一异或门(exclusive-or gate)502。延迟单元d1可接收输入时钟信号ck_in,并且在输入时钟信号ck_in上加入延迟以产生一延迟信号ck_d。输入时钟信号ck_in及延迟信号ck_d可由异或门502接收,使得异或门502产生并输出具有多个脉冲的脉冲信号ck_p,其脉冲位于输入时钟信号ck_in转态的时间点。需注意,脉冲信号ck_p中每两个脉冲之间的时间间隔大致等于输入时钟信号ck_in的周期的一半。

54.在一实施例中,占空比校正电路104可藉由侦测脉冲信号ck_p中每两个脉冲之间的时间间隔长度来调整脉冲信号ck_p的占空比。请参考图6,图6示出了占空比校正电路104的一种详细实施方式。如图6所示,占空比校正电路104包括一脉冲间隔侦测器602及一sr锁存器(sr latch)604。脉冲间隔侦测器602可接收脉冲信号ck_p,并侦测脉冲信号ck_p中两相邻脉冲的间隔长度,sr锁存器604从而根据脉冲间隔侦测器602的侦测结果来产生输出时钟信号ck_out。

55.详细来说,脉冲间隔侦测器602可包括一第一延迟电路612、一控制逻辑614及一第二延迟电路616。第一延迟电路612及第二延迟电路616都包括多个延迟单元。优选地,延迟单元的延迟时间是可以任意调整或设定的,使得延迟电路612及616可产生适当的延迟数

值。

56.图7示出了脉冲间隔侦测器602的一种详细实施方式。如图7所示,第一延迟电路612可从脉冲产生器102接收脉冲信号ck_p,且第一延迟电路612包括至少n个延迟单元,其中每一延迟单元的延迟时间等于td。因此,脉冲信号ck_p中的脉冲可通过延迟单元进行延迟,以在节点a、b、c

…

n上产生延迟脉冲,如图8所示的波形。根据延迟脉冲,控制逻辑614可判断第一延迟电路612中对应于脉冲信号ck_p中两相邻脉冲的间隔长度的延迟单元数量。举例来说,在第一延迟电路612中经过整体延迟时间为n

×

td的n个延迟单元之后,脉冲信号ck_p中的一脉冲被延迟到与下一脉冲重叠。因此,控制逻辑614可侦测出脉冲信号ck_p中两相邻脉冲的间隔长度对应于n个延迟单元。由于每一延迟单元的延迟时间为已知,因此可取得脉冲的间隔时间长度。

57.在此例中,控制逻辑614包括多个与门(and gate),其中每一与门用来对脉冲信号ck_p和其中一延迟脉冲执行“与”运算,因此,当延迟脉冲和原始脉冲信号ck_p中的下一脉冲重叠时,即可通过与门产生新的脉冲。通过这样的方式,经过n个延迟单元之后产生的延迟脉冲可重叠于原始脉冲信号ck_p中的下一脉冲,使得相应的与门输出一侦测脉冲p_d。根据由对应于节点n(即第n个节点)的与门所输出的侦测脉冲p_d,可判断脉冲之间的间隔长度等于n

×

td。需注意的是,本说明书所提出的控制逻辑614结构仅为本发明众多实施例的其中一种。在另一实施例中,控制逻辑614也可以通过其它类型的逻辑门组成,只要控制逻辑614能够找出脉冲信号ck_p中两相邻脉冲的间隔长度即可。

58.为了产生具有精准占空比50%的输出时钟信号ck_out,脉冲信号ck_p中两相邻脉冲的间隔长度须进一步除以2,即取得脉冲之间间隔长度的一半时间长,其可利用第二延迟电路616来实现。根据控制逻辑614的侦测结果,侦测脉冲p_d具有对应于n个延迟单元的延迟时间n

×

td,且延迟时间n

×

td等于两相邻脉冲的间隔长度,因此,通过延迟n/2个延迟单元可产生对应于脉冲间隔长度一半的另一延迟时间(n/2)

×

td。在此例中,第二延迟电路616可产生一输出脉冲p_out,输出脉冲p_out的延迟时间等于两相邻脉冲的间隔长度的一半,即(n/2)

×

td。为了实现一半的延迟时间,第二延迟电路616包括的延迟单元数量可以是第一延迟电路612包括的延迟单元数量的一半,且第一延迟电路612中的每两个延迟单元可对应于第二延迟电路616中的一个延迟单元,如图7所示。

59.请回头参考图6,脉冲间隔侦测器602所产生的侦测脉冲p_d及输出脉冲p_out可传送至sr锁存器604,以根据这些脉冲来产生输出时钟信号ck_out。需注意,两侦测脉冲p_d之间的间隔等于输入时钟信号ck_in的半周期的时间,可据此产生具有双倍频率的输出时钟信号ck_out。也就是说,输出脉冲p_out及侦测脉冲p_d之间的间隔等于(n/2)

×

td,意即输出时钟信号ck_out的占空比为50%。

60.本发明实施例的延迟单元可通过任意方式实现。举例来说,延迟功能可采用任何类型的逻辑门来实现,例如与门、或门(or gate)、与非门(nand gate)、或非门(nor gate)、异或非门(exclusive-nor gate)、异或门或反向器等,且延迟单元可包括以上任一逻辑门或多个逻辑门的组合。图9示出了可用来实现延迟单元的一种示例性反向器,需注意,一延迟单元可藉由偶数个串接的反向器来实现。

61.如图9所示,反向器包括晶体管t1及t2、电流源c1及c2、以及一驱动单元dc1。晶体管t1及t2的漏极端互相耦接且栅极端互相耦接,以实现反向器结构。电流源c1及c2为分别

耦接于晶体管t1及t2源极端的可控制电流源,可用来接收相同或不同的控制信号以输出适当的电流值,从而根据输出电流来调整延迟大小。驱动单元dc1可提供充足的驱动能力以提升反向器的输出信号的压摆率(slew rate)。

62.因此,根据用于电流源c1及c2的控制信号,反向器的延迟时间为可设定且可调整的。在一实施例中,可根据系统需求将延迟时间调整为适当的数值。举例来说,当时钟产生器10用来处理频率较高的时钟信号时,由于所接收的时钟信号具有较短的周期,应对每一延迟单元设定较小的延迟时间,以更精确地取得侦测脉冲的位置。当时钟产生器10用来处理频率较低的时钟信号时,由于所接收的时钟信号具有较长的周期且脉冲之间的间隔也较长,应对每一延迟单元设定较大的延迟时间,以在延迟电路中有限的延迟单元数量之下顺利找到重叠的脉冲位置。系统可对时钟频率进行侦测,从而产生用于延迟单元的适当控制信号以实现适当的延迟时间。

63.值得注意的是,本发明的目的在于提供一种可产生倍频输出时钟的时钟产生器。本领域技术人员当可据此进行修饰或变化,而不限于此。举例来说,在脉冲间隔侦测器602中,控制逻辑614中的与门可通过具有脉冲侦测能力的其它类型逻辑门来取代。此外,在图6的占空比校正电路104中,sr锁存器604也可由其它类型的正反器或任意逻辑门的组合来取代,以在输出时钟信号ck_out中实现适当的频率及占空比50%。在另一实施例中,占空比校正电路104也可通过其它方式来实现,或者具有不同的电路结构。

64.请参考图10,图10示出了占空比校正电路104的另一种详细实施方式,其可接收脉冲信号ck_p并调整脉冲信号ck_p的占空比来产生输出时钟信号ck_out。如图10所示,占空比校正电路104包括一放大器1002、滤波器f1及f2、以及一运算元1004。滤波器f1耦接于放大器1002的第一输入端,滤波器f2耦接于放大器1002的第二输入端。运算元1004耦接于滤波器f1,也同时耦接于放大器1002的输出端。滤波器f1可接收脉冲信号ck_p,并且对脉冲信号ck_p进行滤波以产生一滤波信号v_f。滤波器f2可接收一参考时钟ck_ref,并且对参考时钟ck_ref进行滤波以产生一参考电压v_ref。放大器1002从而根据滤波信号v_f及参考电压v_ref来产生一反馈信号v_err,反馈信号v_err可通过负反馈的路径传送至运算元1004。因此,运算元1004可根据脉冲信号ck_p及反馈信号v_err,产生输出时钟信号ck_out,例如将脉冲信号ck_p减去反馈信号v_err以产生输出时钟信号ck_out,从而通过反馈机制来调整脉冲信号ck_p的占空比。

65.具有负反馈结构的放大器1002搭配滤波器f1及f2可用来将脉冲信号ck_p的占空比调整为50%。若占空比大于50%时,藉由滤波(即通过滤波器f1)产生的滤波信号v_f可逐渐下降;若占空比小于50%时,藉由滤波产生的滤波信号v_f可逐渐上升。放大器1002的反馈机制使得占空比达到50%,从而实现恒定的滤波信号v_f。

66.在此例中,参考时钟ck_ref可以是具有精准占空比50%的时钟信号,因此参考时钟ck_ref可藉由滤波(即通过滤波器f2)转换为准确的参考电压v_ref。在另一实施例中,参考电压v_ref也可由外部电压源或电压产生器直接提供,如此可省略滤波器f2的使用。或者,参考电压v_ref仍可通过滤波器f2进行滤波以改善稳定性。

67.请参考图11,图11示出了占空比校正电路104的又一种详细实施方式。图11所示的占空比校正电路104的电路结构类似于图10所示的占空比校正电路104的电路结构,故功能相似的信号或组件都以相同符号表示,两者的差异在于,图11所示的占空比校正电路104采

用一单端转差分转换器(single-to-differential converter,sdc)1100将脉冲信号ck_p转换为差分信号,以取代外部的参考时钟或参考电压。如此一来,差分信号可分别通过滤波器f1及f2进行滤波以产生滤波信号v_f1及v_f2,其可传送至放大器1002的两输入端。放大器1002从而根据滤波信号v_f1及v_f2来产生反馈信号v_err。藉由放大器1002的负反馈机制,使调整或修正后的占空比达到50%。

68.在另一实施例中,单端转差分转换器1100可由一反向器(inverter)1200取代,如图12所示,也可以实现类似的占空比修正效果。反向器1200可根据所接收的脉冲信号ck_p来产生一反向脉冲信号ck_p’。反向脉冲信号ck_p’及脉冲信号ck_p分别通过滤波器f1及f2进行滤波,随后传送至放大器1002的输入端。关于图12中占空比校正电路104的其它详细实施方式及运作方式可参考前述说明,在此不赘述。

69.根据负反馈结构,可藉由参考电压将脉冲信号ck_p的占空比准确修正为50%。图10显示参考电压v_ref藉由对接收到的参考时钟进行滤波而产生;或者,可通过一外部电路接收参考电压v_ref。此外,图11显示参考电压可通过单端转差分转换器1100产生;图12显示参考电压可通过反向器1200产生。在此情况下,可省略外部的参考时钟或参考电压。

70.综上所述,本发明提供了一种可用于倍频的时钟产生器,此时钟产生器包括一脉冲产生器及一占空比校正电路。根据本发明的实施例,脉冲产生器可根据所接收的输入时钟信号来产生一脉冲信号,其中,脉冲信号包括多个脉冲,其位于输入时钟信号转态的时间点上。接着,占空比校正电路将脉冲信号的占空比调整为50%,以产生输出时钟信号。在一实施例中,占空比校正电路可利用具有延迟电路的脉冲间隔侦测器来侦测脉冲信号中两脉冲之间的间隔,以取得脉冲间隔并控制脉冲的宽度以达到占空比50%。在另一实施例中,占空比校正电路可采用放大器的反馈机制将脉冲信号的占空比修正为50%,以产生输出时钟信号。另外,在一实施例中,可利用由脉冲产生器及占空比校正电路组成的时钟产生器来产生具有双倍频率的输出时钟信号。而在其它实施例中,可将多个倍频器串接而形成一时钟产生器,其中每一倍频器具有一脉冲产生器及一占空比电路,此时钟产生器可用来输出具有2的幂次方倍数频率的时钟信号。如此一来,可避免使用电路结构复杂的锁相环或延迟锁相环,从而节省时钟产生器的功耗及电路面积。

71.以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1