与非门逻辑电路及其制备方法

1.本发明实施例涉及半导体技术,尤其涉及一种与非门逻辑电路及其制备方法。

背景技术:

2.与非门逻辑电路是数字逻辑电路的基本单元之一,在控制电路以及存储器等领域具有广泛的应用。

3.然而,现有的与非门逻辑电路的尺寸较大,控制电路以及存储器电路中又需要大量的与非门逻辑电路,导致控制电路和存储器电路的尺寸较大,不利于提高集成度。

技术实现要素:

4.本发明提供一种与非门逻辑电路及其制备方法,以减小与非门逻辑电路的尺寸。

5.第一方面,本发明实施例提供了一种与非门逻辑电路,所述与非门逻辑电路包括:

6.耗尽型晶体管,所述耗尽型晶体管的第一端用于接入电源,所述耗尽型晶体管的控制端与所述耗尽型晶体管的第二端电连接,所述耗尽型晶体管的第二端作为所述与非门逻辑电路的输出端;

7.增强型的双栅晶体管,所述双栅晶体管的第一端与所述耗尽型晶体管的第二端电连接,所述双栅晶体管的第二端接地,所述双栅晶体管的第一控制端作为所述与非门逻辑电路的第一输入端,所述双栅晶体管的第二控制端作为所述与非门逻辑电路的第二输入端。

8.可选地,所述耗尽型晶体管为gan晶体管,所述双栅晶体管为gan晶体管。

9.可选地,所述双栅晶体管包括依次层叠的衬底、沟道层和氮化铝镓外延层,所述氮化铝镓外延层远离所述沟道层的表面设置有第一凹槽和第二凹槽,所述氮化铝镓外延层远离所述沟道层的表面设置有第一源极金属、第一漏极金属和介电层,其中,所述介电层覆盖所述第一凹槽及所述第二凹槽;

10.所述双栅晶体管还包括第一栅极金属和第二栅极金属,所述第一栅极金属设置于所述介电层远离所述沟道层的一侧且填充所述第一凹槽;

11.所述第二栅极金属设置于所述介电层远离所述沟道层的一侧且填充所述第二凹槽。

12.可选地,所述介电层的材料为氧化铝。

13.可选地,所述第一源极金属及所述第一漏极金属与所述氮化铝镓外延层均为欧姆接触。

14.第二方面,本发明实施例还提供了一种与非门逻辑电路的制备方法,所述与非门逻辑电路包括:耗尽型晶体管,所述耗尽型晶体管的第一端用于接入电源,所述耗尽型晶体管的控制端与所述耗尽型晶体管的第二端电连接,所述耗尽型晶体管的第二端作为所述与非门逻辑电路的输出端;增强型的双栅晶体管,所述双栅晶体管的第一端与所述耗尽型晶体管的第二端电连接,所述双栅晶体管的第二端接地,所述双栅晶体管的第一控制端作为

所述与非门逻辑电路的第一输入端,所述双栅晶体管的第二控制端作为所述与非门逻辑电路的第二输入端;

15.所述制备方法包括:

16.形成所述双栅晶体管及所述耗尽型晶体管;

17.将所述双栅晶体管的第一端与所述耗尽型晶体管的第二端电连接。

18.可选地,形成所述双栅晶体管及所述耗尽型晶体管包括:

19.于衬底上外延形成层叠的沟道层和氮化铝镓外延层,所述与非门逻辑电路具有耗尽型晶体管区和双栅晶体管区;

20.于所述氮化铝镓外延层远离所述沟道层且位于所述双栅晶体管区的表面形成第一凹槽和第二凹槽;

21.于所述氮化铝镓外延层远离所述沟道层且位于所述双栅晶体管区的表面形成第一源极金属和第一漏极金属,并于所述氮化铝镓外延层远离所述沟道层且位于所述耗尽型晶体管区的表面形成第二源极金属和第二漏极金属;其中,所述第一源极金属作为所述双栅晶体管的第二端,所述第一漏极金属作为所述双栅晶体管的第一端,所述第二源极金属作为所述耗尽型晶体管的第二端,所述第二漏极金属作为所述耗尽型晶体管的第一端;

22.于所述氮化铝镓外延层远离所述沟道层的表面形成介电层,其中,所述介电层覆盖所述第一凹槽及所述第二凹槽;

23.于所述第一凹槽内形成第一栅极金属,并于所述第二凹槽内形成第二栅极金属,并于所述介电层远离所述氮化铝镓外延层且位于所述耗尽型晶体管区的部分形成第三栅极金属。

24.可选地,于所述氮化铝镓外延层远离所述沟道层的表面形成第一凹槽和第二凹槽包括:

25.于所述氮化铝镓外延层远离所述沟道层的表面形成氮化硅牺牲层;

26.于所述氮化硅牺牲层对应所述第一凹槽及所述第二凹槽的部分开孔暴露出所述氮化铝镓外延层;

27.刻蚀所述开孔暴露出的所述氮化铝镓外延层以形成所述第一凹槽及所述第二凹槽;

28.去除剩余的氮化硅牺牲层。

29.可选地,所述于所述氮化铝镓外延层远离所述沟道层且位于所述双栅晶体管区的表面形成第一源极金属和第一漏极金属,并于所述氮化铝镓外延层远离所述沟道层且位于所述耗尽型晶体管区的表面形成第二源极金属和第二漏极金属包括:

30.采用电子束蒸发生长所述第一源极金属、所述第二源极金属、所述第一漏极金属及所述第二漏极金属,并对所述第一源极金属、所述第二源极金属、所述第一漏极金属及所述第二漏极金属退火形成欧姆接触。

31.可选地,将所述双栅晶体管的第一端与所述耗尽型晶体管的第二端电连接包括:

32.整面形成覆盖所述第一源极金属、第二源极金属、所述第一漏极金属及所述第二漏极金属的钝化层;

33.于所述钝化层上开孔以分别暴露出所述第一源极金属、所述第二源极金属、所述第一漏极金属、所述第二漏极金属、所述第一栅极金属、所述第二栅极金属及所述第三栅极

金属;

34.分别形成与所述第一漏极金属、所述第二漏极金属、所述第一栅极金属、所述第二栅极金属及所述第三栅极金属接触的电极金属;

35.形成与所述第二源极金属对应的电极金属及所述第一漏极金属对应的电极金属均接触的连接金属。

36.本发明本实施例的技术方案,采用的与非门逻辑电路包括:耗尽型晶体管,耗尽型晶体管的第一端用于接入电源,耗尽型晶体管的控制端与耗尽型晶体管的第二端电连接,耗尽型晶体管的第二端作为与非门逻辑电路的输出端;增强型的双栅晶体管,双栅晶体管的第一端与耗尽型晶体管的第二端电连接,双栅晶体管的第二端接地,双栅晶体管的第一控制端作为与非门逻辑电路的第一输入端,双栅晶体管的第二控制端作为与非门逻辑电路的第二输入端。采用一个双栅晶体管来构成与非门逻辑电路,而不是采用两个独立的晶体管,相当于将两个独立的晶体管进行了源漏极的合并,从而能够极大地减小与非门逻辑电路的尺寸。

附图说明

37.图1为本发明实施例提供的一种与非门逻辑电路的电路结构示意图;

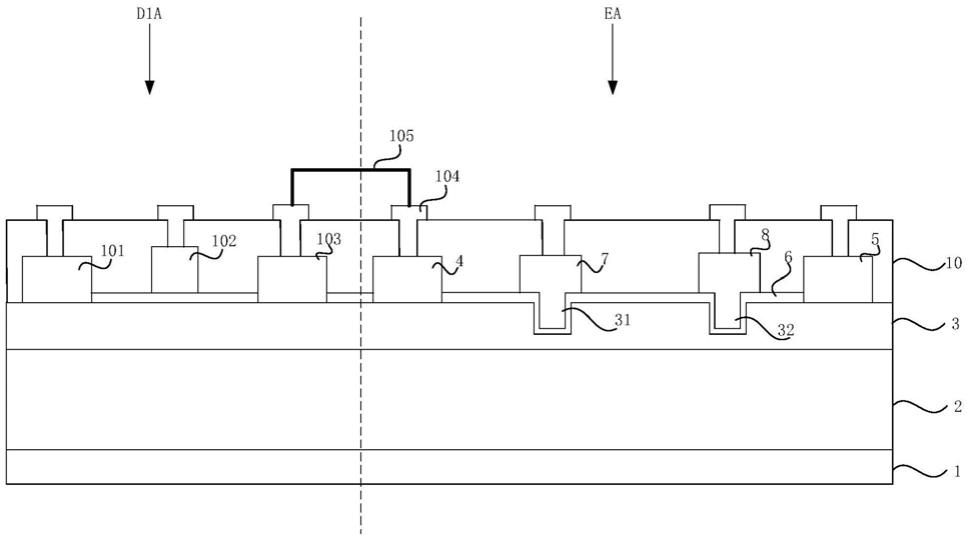

38.图2为本发明实施例提供的一种双栅晶体管的结构示意图;

39.图3为本发明实施例提供的一种与非门逻辑电路的制备方法的流程图。

具体实施方式

40.下面结合附图和实施例对本发明作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本发明,而非对本发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本发明相关的部分而非全部结构。

41.图1为本发明实施例提供的一种与非门逻辑电路的电路结构示意图,参考图1,与非门逻辑电路包括:耗尽型晶体管d1,耗尽型晶体管d1的第一端用于接入电源vdd,耗尽型晶体管d1的控制端与耗尽型晶体管d1的第二端电连接,耗尽型晶体管d1的第二端作为与非门逻辑电路的输出端vout;增强型的双栅晶体管e,双栅晶体管e的第一端与耗尽型晶体管d1的第二端电连接,双栅晶体管e的第二端接地,双栅晶体管e的第一控制端作为与非门逻辑电路的第一输入端v1,双栅晶体管e的第二控制端作为与非门逻辑电路的第二输入端v2。

42.具体地,与非门逻辑电路的逻辑表达式为其中,y为与非门逻辑电路的输出,a和b为与非门逻辑电路的输入,当a为0,b为0时,y为1;当a为0,b为1时,y为1;当a为1,b为0时,y为1;当a为1,b为1时,y为零;在本实施例中,耗尽型晶体管d1和增强型的双栅晶体管e均为n型晶体管,且耗尽型晶体管d1在其栅极偏压为0时,仍能够导通,也即当施加上电源vdd时,耗尽型晶体管d1始终处于导通状态,此时与非门逻辑电路的输出端vout与电源vdd导通,当第一输入端v1与第二输入端v2中至少一个为低电平时,双栅晶体管e始终为关断状态,也即此时与非门逻辑电路的输出端vout始终输出高电平信号,且双栅晶体管e为增强型,当其栅极偏压为0时,不能够导通,避免双栅晶体管发生误导通而导致与非门逻辑电路产生逻辑错误;当第一输入端v1与第二输入端v2均为高电平时,双栅晶体管e处于导通状态,此时与非门逻辑电路的输出端vout被拉低,也即只有在第一输入端v1和第二输入端v2

均为高电平时,与非门逻辑电路的输出端vout才会输出低电平,从而实现了逻辑与非的功能;且在本实施例中,采用一个双栅晶体管e来构成与非门逻辑电路,而不是采用两个独立的晶体管,相当于将两个独立的晶体管进行了源漏极的合并,从而能够极大地减小与非门逻辑电路的尺寸;同时由于简化了接地端到输出端vout之间的电路,双栅晶体管的通态电阻较小,能够进一步降低与非门逻辑电路输出端逻辑低电平的电位,提高抗噪声能力;另外还能够缩小第一输入端v1和第二输入端v2之间的距离,还能够显著减小电路的复杂性。

43.本实施例的技术方案,采用的与非门逻辑电路包括:耗尽型晶体管,耗尽型晶体管的第一端用于接入电源,耗尽型晶体管的控制端与耗尽型晶体管的第二端电连接,耗尽型晶体管的第二端作为与非门逻辑电路的输出端;增强型的双栅晶体管,双栅晶体管的第一端与耗尽型晶体管的第二端电连接,双栅晶体管的第二端接地,双栅晶体管的第一控制端作为与非门逻辑电路的第一输入端,双栅晶体管的第二控制端作为与非门逻辑电路的第二输入端。采用一个双栅晶体管来构成与非门逻辑电路,而不是采用两个独立的晶体管,相当于将两个独立的晶体管进行了源漏极的合并,从而能够极大地减小与非门逻辑电路的尺寸。

44.可选地,耗尽型晶体管d1为gan晶体管,双栅晶体管e为gan晶体管。

45.具体地,gan材料具有宽禁带等物理特性,gan晶体管通过algan外延层和gan层之间由压电和极化效应产生的高浓度二维电子气(2deg)导电,具有迁移率高,导通电阻小等特点。采用gan晶体管作为耗尽型晶体管d1以及双栅晶体管e,能够极大地提高耗尽型晶体管d1以及双栅晶体管e的开关速度,从而提高与非门逻辑电路的运算速度。

46.可选地,图2为本发明实施例提供的一种双栅晶体管的结构示意图,参考图2,双栅晶体管包括依次层叠的衬底1、沟道层2和氮化铝镓外延层3,氮化铝镓外延层3远离沟道层2的表面设置有第一凹槽31和第二凹槽32,氮化铝镓外延层3远离沟道层2的表面设置有第一源极金属4、第一漏极金属5和介电层6,其中,介电层6覆盖第一凹槽31和第二凹槽32;双栅晶体管还包括第一栅极金属7和第二栅极金属8,第一栅极金属7设置于介电层6远离沟道层3的一侧且填充第一凹槽31;第二栅极金属8设置于介电层6远离沟道层3的一侧且填充第二凹槽32。

47.具体地,衬底1例如可以是si衬底,衬底1和沟道层2之间还可设置氮化镓缓冲层,沟道层2例如可以是氮化镓沟道层,介电层6例如可以是氧化铝介电层,利用挖槽型增强型器件作为双栅极器件,第一源极金属4作为双栅晶体管的第一端,第一漏极金属5作为双栅晶体管的第二端;第一栅极金属7作为双栅晶体管的第一控制端,第二栅极金属8作为双栅晶体管的第二控制端,只有当第一栅极金属7和第二栅极金属8均施加高电平时,第一源极金属4和第一漏极金属5之间才会形成导电沟道,使得双栅晶体管导通,双栅晶体管的两个栅极(第一栅极金属7和第二栅极金属8)能够互不干扰地实现输入功能,从而实现与非门的逻辑功能。

48.可选地,第一源极金属4及第一漏极金属5与氮化铝镓外延层3均为欧姆接触。

49.具体地,可通过快速退火的方式使得第一源极金属4及第一漏极金属5与氮化铝镓外延层3形成欧姆接触,使得接触阻抗较小,双栅晶体管的通态电阻较小,能够降低与非门逻辑电路输出端逻辑低电平的电位,提高抗噪声能力。

50.图3为本发明实施例提供的一种与非门逻辑电路的制备方法的流程图,与非门逻

辑电路包括本发明任意实施例提供的与非门逻辑电路,与非门逻辑电路的制备方法包括:

51.步骤s101,形成双栅晶体管及耗尽型晶体管;

52.具体地,双栅晶体管和耗尽型晶体管可分别形成,例如可以先形成双栅晶体管,后形成耗尽型晶体管,或者也可以先形成耗尽型晶体管,再形成双栅晶体管,或者也可以同时形成双栅晶体管和耗尽型晶体管。

53.步骤s102,将双栅晶体管的第一端与耗尽型晶体管的第二端电连接。

54.具体地,双栅晶体管的第二端可以与金属地电连接从而实现接地连接,将双栅晶体管与耗尽型晶体管连接之后,实现与非门逻辑电路的电气连接。需要说明的是,在制作完成后还可对与非门逻辑电路进行测试和封装,最终完成与非门逻辑电路的制作。

55.采用本发明实施例的与非门逻辑电路的制备方法,制备出的与非门逻辑电路利用一个双栅晶体管来构成与非门逻辑电路,而不是采用两个独立的晶体管,相当于将两个独立的晶体管进行了源漏极的合并,从而能够极大地减小与非门逻辑电路的尺寸。

56.可选地,形成双栅晶体管及耗尽型晶体管包括:

57.于衬底上外延形成层叠的沟道层和氮化铝镓外延层;

58.具体地,可先在si衬底上外延形成氮化镓沟道层和氮化铝镓外延层,如图2所示,与非门逻辑电路具有耗尽型晶体管区d1a和双栅晶体管区ea。

59.于氮化镓外延层远离沟道层且位于双栅晶体管区ea的表面形成第一凹槽31和第二凹槽32;

60.具体地,可通过先在在氮化铝镓外延层远离沟道层的表面形成氮化硅牺牲层,可以通过pecvd(plasma enhanced chemical vapor deposition,等离子体增强化学的气相沉积法)沉积氮化硅牺牲层;随后对氮化硅牺牲层进行刻蚀,将对应第一凹槽及第二凹槽的部分刻蚀掉,也即于氮化硅牺牲层对应第一凹槽及第二凹槽的部分进行开孔,从而暴露出氮化铝镓外延层;随后刻蚀开孔暴露出的氮化铝镓外延层以形成第一凹槽和第二凹槽,具体可利用湿法刻蚀(氧气刻蚀加盐酸浸泡)的方法对被开孔暴露出的氮化铝镓外延层进行刻蚀,制作出第一凹槽和第二凹槽;第一凹槽和第二凹槽刻蚀完成后再将剩余的氮化硅牺牲层进行去除。

61.于氮化铝镓外延层远离沟道层且位于双栅晶体管区的表面形成第一源极金属4和第一漏极金属7,并于氮化铝镓外延层远离沟道层且位于耗尽型晶体管区的表面形成第二源极金属101和第二漏极金属103;其中,第一源极金属作为双栅晶体管的第二端,第一漏极金属作为双栅晶体管的第一端,第二源极金属作为耗尽型晶体管的第二端,第二漏极金属作为耗尽型晶体管的第一端;

62.具体地,可在氮化铝镓外延层远离沟道层的表面的两端分别形成第一源极金属4、第一漏极金属5、第二源极金属101和第二漏极金属103,例如可采用电子束蒸发生长第一源极金属4、第一漏极金属5、第二源极金属101和第二漏极金属103,并快速退火以实现欧姆接触。

63.于氮化铝镓外延层远离沟道层的表面形成介电层,介电层覆盖第一凹槽及第二凹槽;

64.具体地,可通过ald(atomic layer deposition,原子层沉积)的方式沉积氧化铝层,作为介电层。

65.于第一凹槽内形成第一栅极金属,并于第二凹槽内形成第二栅极金属,并于介电层远离氮化铝镓外延层且位于耗尽型晶体管区的部分形成第三栅极金属102。

66.具体地,在介电层制作完成后,可利用电子束蒸发的方式同时形成第一栅极金属7、第二栅极金属8和第三栅极金属102,第一栅极金属作为双栅晶体管的第一控制端,第二栅极金属作为双栅晶体管的第二控制端,第三栅极金属102作为耗尽型晶体管的控制端。

67.可选地,将双栅晶体管的第一端与耗尽型晶体管的第二端电连接包括:

68.整面形成覆盖第一源极金属4、第二源极金属101、第一漏极金属5及第二漏极金属103的钝化层10;例如可以通过pecvd的方式生长形成氮化硅钝化层。

69.于钝化层10上开孔以分别暴露出第一源极金属4、第二源极金属101、第一漏极金属5、第二漏极金属103、第一栅极金属7、第二栅极金属8及第三栅极金属102;例如可以通过四氟化碳对钝化层10进行开孔,且由于在生长介电层时,第一源极金属4、第二源极金属101、第一漏极金属5、第二漏极金属103、第一栅极金属7、第二栅极金属8及第三栅极金属102的表面会存在氧化铝层,在开孔后可利用boe(buffered oxide etch,缓冲氧化物刻蚀液)溶液去除开孔处的氧化铝,防止第一源极金属4、第二源极金属101、第一漏极金属5、第二漏极金属103、第一栅极金属7、第二栅极金属8及第三栅极金属102无法与外部进行信号传输;随后分别形成与第一漏极金属、第二漏极金属、第一栅极金属、第二栅极金属及第三栅极金属接触的电极金属104,电极金属104可以是铝;

70.形成与第二源极金属对应的电极金属及第一漏极金属对应的电极金属均接触的连接金属105;例如可以通过电子束蒸发铝进行金属和器件间的互连,也形成与非门逻辑电路电路形式。可以理解的是,最后还可对与非门逻辑电路进行测试和封装。

71.注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例,而本发明的范围由所附的权利要求范围决定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1