用于反熔丝电路中的隔离保护电路结构的制作方法

1.本发明涉及微电子技术领域,特别涉及一种用于用于反熔丝电路中的隔离保护电路结构。

背景技术:

2.反熔丝器件是一种非常重要的可编程互连单元,已被广泛地应用于用户可配置集成电路中。在具体的集成电路中,反熔丝器件在编程之前是处于关断状态的,呈现百兆欧姆以上的电阻;编程之后形成低电阻连接。

3.基于反熔丝技术的用户可配置集成电路中,低压逻辑电路的输入和输出通常都是连接在反熔丝器件组成的布线轨线上。在对反熔丝器件编程时,需要施加能够击穿反熔丝器件的高电压。由于低压逻辑电路是由低压mos晶体管组成,在反熔丝器件编程期间,低压mos晶体管很容易因高电压导致击穿而损坏,造成电路可靠性问题。

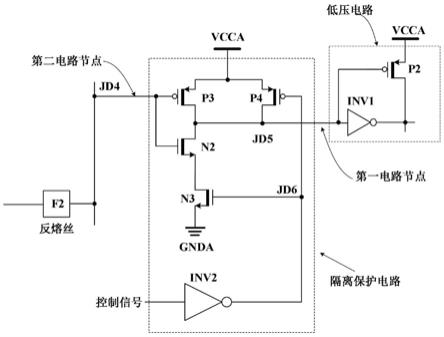

4.现有典型的高低压电路之间的隔离保护的结构如图1所示,虽然有助于防止击穿损坏的发生,但它需要电荷泵产生运行所需的栅控制电压,带来了芯片面积的增加以及设计复杂度的增加;另外这种隔离保护结构需要采用高压mos晶体管,带来了电路传输速度的降低的问题。

技术实现要素:

5.本发明的目的在于提供一种反熔丝电路中的隔离保护电路结构,以解决现有隔离保护电路需要外加电荷泵产生栅控制电压,从而造成芯片面积增加和设计难度增加、以及需要采用高压mos管带来电路传输速度降低的问题。

6.为解决上述技术问题,本发明提供了一种反熔丝电路中的隔离保护电路结构,与低压电路连接,所述低压电路包括反相器inv1和pmos管p2,反相器inv1的输入端接pmos管p2的控制栅,输出端接pmos管p2的漏端,所述隔离保护电路结构包括pmos管p3和p4、nmos管n2和n3、反相器inv2;所述反相器inv2的输入端输入控制信号,输出端连接pmos管p4的控制栅和nmos管n3的控制栅;pmos管p4的漏端连接第一电路节点jd5;pmos管p3的控制栅连接第二电路节点jd4,漏端连接第一电路节点jd5;nmos管n2的控制栅连接第二电路节点jd4,漏端接第一电路节点jd5,源端接nmos管n3的漏端,nmos管n3的控制栅接所述反相器inv2的输出端,源端接逻辑电路工作地gnda。

7.可选的,所述pmos管p3和p4的源端均接逻辑电路工作电源vcca。

8.可选的,所述反相器inv1的输入端连接第一电路节点jd5。

9.本发明还提供了一种用于反熔丝电路中的隔离保护电路结构,与低压电路连接,所述低压电路包括反相器inv1和pmos管p2,反相器inv1的输入端接pmos管p2的控制栅,输出端接pmos管p2的漏端,所述隔离保护电路结构包括pmos管p5、nmos管n4、反相器inv3;

所述反相器inv3的输入端输入控制信号,输出端连接nmos管n4的源端;pmos管p5的控制栅连接第二电路节点jd7,源端连接逻辑电路工作电源vcca,漏端连接第一电路节点jd8;nmos管n4的控制栅连接第二电路节点jd7,源端连接反相器inv3的输出端,漏端连接第一电路节点jd8。

10.可选的,所述反相器inv1的输入端连接第一电路节点jd8。

11.本发明还提供了一种用于反熔丝电路中的隔离保护电路结构,与低压电路连接,所述低压电路包括反相器inv1和pmos管p2,反相器inv1的输入端接pmos管p2的控制栅,输出端接pmos管p2的漏端,所述隔离保护电路结构包括pmos管p6和p7、nmos管n5、反相器inv4和inv5;反相器inv4的输入端输入控制信号,输出端连接nmos管n5的源原和反相器inv5的输入端;反相器inv5的输出端连接pmos管p7的控制栅;pmos管p6的控制栅连接到第二电路节点jd10,源端连接逻辑电路工作电源vcca,漏端连接到第一电路节点jd11;nmos管n5的控制栅连接第二电路节点jd10,源端连接反相器inv4的输出端和反相器inv5的输入端,漏端连接到第一电路节点jd11;pmos管p7的控制栅连接反相器inv5的输出端,源端连接逻辑电路工作电源vcca,漏端连接到第一电路节点jd11。

12.可选的,所述反相器inv1的输入端连接第一电路节点jd11。

13.在本发明提供的用于反熔丝电路中的隔离保护电路结构,在反熔丝器件编程期间,控制信号为逻辑“高”,该隔离保护电路结构能够将低压电路与编程反熔丝器件用的高压电路隔离开来。在正常工作模式下,控制信号为逻辑“低”,该隔离保护电路结构能够实现逻辑信号的正常传输,有效地保护了低压逻辑电路免遭高电压的击穿而损坏,解决了可靠性问题,同时解决了已知现有典型的高低压电路之间隔离保护电路结构存在的芯片面积以及电荷泵问题,而且没有引入新的问题。

附图说明

14.图1为现有典型的将低压电路节点与高压编程电路节点进行隔离保护的电路结构示意图;图2为本发明实施例一提供的将低压电路节点与高压编程电路节点进行隔离保护电路结构示意图;图3为本发明实施例二提供的将低压电路节点与高压编程电路节点进行隔离保护电路结构示意图;图4为本发明实施例三提供的将低压电路节点与高压编程电路节点进行隔离保护电路结构示意图。

具体实施方式

15.以下结合附图和具体实施例对本发明提出的一种反熔丝电路中的隔离保护电路结构作进一步详细说明。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说

明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

16.为了叙述的更清楚,说明如下:在本领域中,不管是反熔丝器件编程期间还是正常工作模式下,vcca均是逻辑电路工作电压,所叙述电路中的任何mos晶体管器件不会因vcca导致击穿损坏;隔离保护电路右边的电路节点,是低压逻辑电路的输入,这里称之为第一电路节点;隔离保护电路左边的电路节点,连接到反熔丝器件组成的布线轨线,在反熔丝器件编程期间,这个电路节点的电压是可以击穿反熔丝器件和低压mos晶体管的高电压,在正常的工作模式下,这个节点的电压是逻辑电路工作电压vcca,不会对低压mos晶体管造成击穿损坏,这个节点称之为第二电路节点。

17.实施例一本实施例一提供了一种反熔丝电路中的隔离保护电路结构,与低压电路连接。所述低压电路包括反相器inv1和pmos管p2,反相器inv1的输入端接pmos管p2的控制栅,输出端接pmos管p2的漏端。所述隔离保护电路结构如图2所示,包括pmos管p3和p4、nmos管n2和n3、反相器inv2;所述反相器inv2的输入端输入控制信号,输出端连接pmos管p4的控制栅和nmos管n3的控制栅;pmos管p4的漏端连接第一电路节点jd5;pmos管p3的控制栅连接第二电路节点jd4,漏端连接第一电路节点jd5;nmos管n2的控制栅连接第二电路节点jd4,漏端接第一电路节点jd5,源端接nmos管n3的漏端,nmos管n3的控制栅接所述反相器inv2的输出端,源端接逻辑电路工作地gnda;所述pmos管p3和p4的源端均接逻辑电路工作电源vcca。所述反相器inv1的输入端连接第一电路节点jd5。pmos管p3和nmos管n2的栅氧层厚度采用厚栅氧进行工艺制造;pmos管p4和nmos管n3以及反相器inv2的栅氧层厚度根据实际需要,选择薄栅氧或者厚栅氧。

18.所述隔离保护电路结构将第一电路节点jd5与第二电路节点jd4进行了有效的隔离保护,也就是将低压逻辑电路的输入与高压编程信号进行了有效的隔离保护,其隔离保护原理如下:在反熔丝器件f2编程期间,第二电路节点jd4施加用于反熔丝器件f2编程高电压,控制信号为逻辑“高”,那么电路节点jd6就是低电压0v。由于第二电路节点jd4为高电压,从而pmos管p3关断,nmos管n2开启;由于电路节点jd6是低电压0v,从而pmos管p4开启,nmos管n3关断。所以第一电路节点jd5,也就是所述隔离保护电路结构的输出就是逻辑电路工作电压vcca。同时,pmos管p3的源端和漏端之间、pmos管p4的源端和漏端之间承受的电压均是0v,nmos管n2的源端和漏端之间承受的电压也是0v,nmos管n3的源端和漏端之间承受的电压是逻辑电路工作电压vcca。根据以上所述,在反熔丝器件编程期间,本实施例一提供的隔离保护电路结构中,除了pmos管p3和nmos管n2的控制栅承受了反熔丝器件f2编程时所加的高电压,其它地方都工作在逻辑电路工作电压vcca下。

19.在正常工作模式期间,第二电路节点jd4传输的正常的逻辑信号,这时控制信号为逻辑“低”,那么电路节点jd6就是逻辑“高”。由于电路节点jd6是逻辑“高”,从而pmos管p4关断,nmos管n3开启,形成了第二电路节点jd4到第一电路节点jd5之间的逻辑信号通路,这时所述隔离保护电路就是一个普通的与非门结构,不会影响信号的传输速度,也就是不会降低电路的性能。

20.本实施例一提供的隔离保护电路结构中,不需要电荷泵,所以消除了图1中已知现

有典型的隔离保护电路结构中电荷泵带来的问题,也没有引入新的问题。

21.实施例二图3为本实施例二提供的将低压电路与高压编程电路节点进行隔离保护的第二个电路结构。该隔离保护电路结构与低压电路连接,所述低压电路包括反相器inv1和pmos管p2,反相器inv1的输入端接pmos管p2的控制栅,输出端接pmos管p2的漏端。如图3所示,所述隔离保护电路结构包括pmos管p5、nmos管n4、反相器inv3;所述反相器inv3的输入端输入控制信号,输出端连接nmos管n4的源端;pmos管p5的控制栅连接第二电路节点jd7,源端连接逻辑电路工作电源vcca,漏端连接第一电路节点jd8;nmos管n4的控制栅连接第二电路节点jd7,源端连接反相器inv3的输出端,漏端连接第一电路节点jd8。所述反相器inv1的输入端连接第一电路节点jd8。pmos管p5和nmos管n4的栅氧层厚度采用厚栅氧进行工艺制造;反相器inv3的栅氧层厚度根据实际需要,选择薄栅氧或者厚栅氧。

22.本实施例二提供的隔离保护电路结构将第一电路节点jd8与第二电路节点jd7进行了有效的隔离保护,也就是将低压逻辑电路的输入与高压编程信号进行了有效的隔离保护,其隔离保护原理如下:在反熔丝器件f3编程期间,第二电路节点jd7施加用于反熔丝器件f3编程高电压,控制信号为逻辑“低”,那么电路节点jd9就是逻辑“高”。由于第二电路节点jd7为高电压,从而pmos管p5关断,nmos管n4开启;由于电路节点jd9是逻辑“高”,也就是说电路节点jd9电压是逻辑电路工作电压vcca,从而第一电路节点jd8,也就是所述隔离保护电路结构输出节点的电压是逻辑电路工作电压vcca。同时,pmos管p5和nmos管n4的源端和漏端之间承受的电压均是0v。根据以上所述,在反熔丝器件编程期间,除了pmos管p5和nmos管n4的控制栅承受了反熔丝器件f3编程时所加的高电压,其它地方都工作在逻辑电路工作电压vcca下。

23.在正常工作模式期间,第二电路节点jd7传输的正常的逻辑信号,这时控制信号为逻辑“高”,那么电路节点jd9就是逻辑“低”,也就是电路节点jd9的电压是0v,形成了第二电路节点jd7到第一电路节点jd8之间的逻辑信号通路。这时本实施例二的隔离保护电路就是一个普通的反相器结构,不会影响信号的传输速度,也就是不会降低电路的性能。

24.本实施例二的隔离保护电路结构中,不需要电荷泵,所以消除了图1中已知现有典型的隔离电路结构中电荷泵带来的问题,也没有引入新的问题。

25.实施例三图4为本实施例三提供的将低压电路与高压编程电路节点进行隔离保护的第三个电路结构。该隔离保护电路结构与低压电路连接,所述低压电路包括反相器inv1和pmos管p2,反相器inv1的输入端接pmos管p2的控制栅,输出端接pmos管p2的漏端。如图4所示,所述隔离保护电路结构包括pmos管p6和p7、nmos管n5、反相器inv4和inv5;反相器inv4的输入端输入控制信号,输出端连接nmos管n5的源原和反相器inv5的输入端;反相器inv5的输出端连接pmos管p7的控制栅;pmos管p6的控制栅连接到第二电路节点jd10,源端连接逻辑电路工作电源vcca,漏端连接到第一电路节点jd11;nmos管n5的控制栅连接第二电路节点jd10,源端连接反相器inv4的输出端和反相器inv5的输入端,漏端连接到第一电路节点jd11;pmos管p7的控制栅连接反相器inv5的输出端,源端连接逻辑电路工作电源vcca,漏端连接到第一电路节点jd11。所述反相器inv1的输入端连接第一电路节点jd11。pmos管p6和nmos管n5的栅氧层厚度采用厚栅氧进行工艺制造;pmos管p7和反相器inv4以及反相器inv5的栅

氧层厚度根据实际需要,选择薄栅氧或者厚栅氧。

26.本实施例三提供的隔离保护电路结构将将第一电路节点jd11与第二电路节点jd10进行了有效的隔离保护,也就是将低压逻辑电路的输入与高压编程信号进行了有效的隔离保护,其隔离保护原理如下:在反熔丝器件f4编程期间,第二电路节点jd10施加用于反熔丝器件f4编程高电压,控制信号为逻辑“低”,那么电路节点jd13就是逻辑“高”,电路节点jd12就是逻辑“低”,也就是说电路节点jd13的电压是逻辑电压vcca,电路节点jd12的电压是0v;另外由于第二电路节点jd10为高电压,从而pmos管p6关断,pmos管p7和nmos管n5开启。所以第一电路节点jd11,也就是所述隔离保护电路结构的输出就是逻辑电路工作电压vcca。同时,pmos管p6的源端和漏端之间、pmos管p7的源端和漏端之间承受的电压均是0v,nmos管n5的源端和漏端之间承受的电压也是0v。

27.根据以上叙述,在反熔丝器件编程期间,除了pmos管p6和nmos管n5的控制栅承受了反熔丝器件f4编程时所加的高电压,其它地方都工作在逻辑电路工作电压vcca下。

28.在正常工作模式期间,第二电路节点jd10传输的正常的逻辑信号,这时控制信号为逻辑“高”,那么电路节点jd13就是逻辑“低”,电路节点jd12就是逻辑“高”,也就是说电路节点jd13的电压是0v,电路节点jd12的电压是逻辑电路工作电压vcca,形成了第二电路节点jd10到第一电路节点jd11之间的逻辑信号通路。这时本实施例三的隔离保护电路就是一个普通的反相器结构,不会影响信号的传输速度,也就是不会降低电路的性能。

29.本实施例三的隔离保护电路结构中,不需要电荷泵,所以消除了图1中已知现有典型的隔离的电路结构中电荷泵带来的问题,也没有引入新的问题。

30.上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1