一种用于离散型Sigma-Delta调制器的防过载无源加法器

一种用于离散型sigma-delta调制器的防过载无源加法器

技术领域

1.本发明是一种用于离散型sigma-delta调制器的防过载无源加法器,属于模拟集成电路技术领域,主要应用于离散型前馈sigma-delta模数转换器。

背景技术:

2.sigma-delta adc作为一种高精度模数转换器被广泛应用在现代通信、医疗、便携式电子系统中。随着集成电路制造工艺向着深亚微米方向不断演进,电源电压降低以及应用系统,尤其是生物医学系统对功率消耗的要求越来越高,高精度sigma-delta adc的设计面临着越来越复杂的挑战,成为近年来学术界和工业界所关注的非常活跃的领域之一。sigma-delta adc是现代语音频带和高分辨率精密测量领域应用最广泛的转换器。它利用过采样和噪声整形技术,用速度换取精度,以较低的模拟电路复杂度达到了更高的精度。因此,如何在实现高精度转换的同时降低系统的功耗成为当下主流的研究热点。

3.当前sigma-delta调制器主要由两大基本结构,反馈结构与前馈结构组成。其中,前馈结构更利于实现低功耗。虽然反馈结构可以获得较好的信号传输函数,但它需要较大的积分器电压幅度范围,这就要求每级积分器中的跨导运放实现高压摆率与大摆幅,增大了功耗;而前馈结构大大降低了积分器的电压幅度范围,从而降低了每级积分器中跨导运放的设计要求。因此,低功耗sigma-delta调制器多采用前馈型系统,而前馈型系统一般都会用到加法器。

4.然而sigma-delta调制器的问题之一是整体电路的稳定性。调制器通常需要多级积分器进行级联,在输入信号幅度较大时,调制器很容易进入过载状态,即各级积分器的输出超过其输出摆幅,甚至一端电压高到电源电压,一端电压低到地电位,此时调制器输出信号的信噪比大幅度下降,发生严重失真现象。

5.因此,对于sigma-delta调制器而言,在设计时要考虑整体系统稳定性的问题,调整好每级积分器的系数,同时在输入信号摆幅较大的情况下,仍要保证整个调制器处在稳定状态,避免过载现象发生。

技术实现要素:

6.本发明的目的是克服已有技术不足之处,提出一种用于离散型sigma-delta调制器的防过载无源加法器,通过简单的电路改进,实现多路信号求和功能,同时通过控制调制器中积分器的采样电容值,解决了调制器在大输入信号幅度下的过载问题,可以广泛应用于离散型前馈sigma-delta调制器中。

7.实现本发明目的技术方案是:

8.一种用于离散型sigma-delta调制器的的防过载无源加法器,包括非交叠时钟发生源,用于产生两相不交叠时钟;开关电容电路,用于实现多路信号求和功能;电压比较器和或门,用于根据加法器的输出电压和参考电压vref的值产生控制积分器采样电容值的极性信号。

9.其中,第一开关sw1一端接第一输入端口vip1,另一端接第一电容ca1的左端;第二开关sw2一端接第二输入端口vip2,另一端接第二电容ca2的左端;第三开关sw3一端接第三输入端口vin2,另一端接第三电容ca3的左侧;第四开关sw4一端接第四输入端口vin1,另一端接第四电容ca4的左侧。

10.第五开关sw5一端接参考电压vcm,另一端接第一电容ca1的左端;第六开关sw6一端接参考电压vcm,另一端接第二电容ca2的左端;第七开关sw7一端接参考电压vcm,另一端接第三电容ca3的左端,第八开关sw8一端接参考电压vcm,另一端接第四电容ca4的左端;第九开关sw9一端接参考电压vcm,另一端接第二电容ca2的右端;第十开关sw10一端接参考电压vcm,另一端接第三电容ca3的左端。

11.第一比较器com1正端输入接加法器第一输出端口vop,负端输入接参考电压vref;第二比较器com2正端输入接加法器第二输出端口von,负端输入接参考电压vref;第一比较器com1,第二比较器com2的输出接或门or输入端,或门的输出为加法器的第三输出端口vc。

12.一种用于离散型sigma-delta调制器的防过载无源加法器,该电路的工作步骤简述如下。

13.步骤一:在ck2的高相位中,开关sw5、sw6、sw7、sw8、sw9、sw10闭合,开关sw1、sw2、sw3、sw4断开,电容ca1、ca2、ca3、ca4上的电荷被清零,在ck1的高相位中,开关sw1、sw2、sw3、sw4闭合,开关sw5、sw6、sw7、sw8、sw9、sw10断开,根据输入信号vip1、vip2、vin1、vin2以及电容ca1、ca2、ca3、ca4的值,得到开关电容电路的多路信号求和电压vop,von。

14.步骤二:步骤一中,多路信号求和电压vop,von和参考电压vref分别接到比较器com1和com2的正端和负端。比较将判断求和电压和参考电压之差的极性,两个比较器的输出信号最后通过或门or输出相应的逻辑电平vc,最后用信号vc控制积分器的采样电容值来避免调制器工作在过载状态。

附图说明

15.图1为用于本发明的非交叠时钟产生子模块示意图。

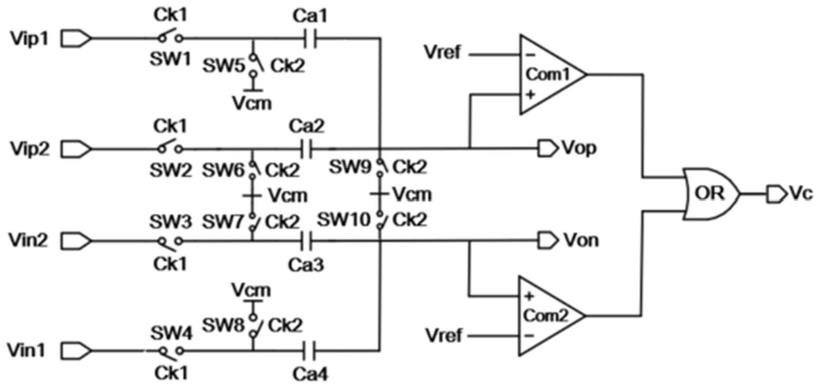

16.图2为本发明提出的防过载无源加法器电路结构图。

17.图3为本发明提出的防过载无源加法器用于一种调制器的示例电路结构图。

具体实施方式

18.为了使本发明的目的和技术优点更加清楚明白,以下结合附图及示例对本发明进行进一步的详细说明。以下示例用于说明本发明,但不是限制本发明的应用范围。

19.如图2所示为本发明的电路结构图,一种用于离散型sigma-delta调制器的的防过载无源加法器,包括非交叠时钟发生源,用于产生两相不交叠时钟;开关电容电路,用于实现多路信号求和功能;电压比较器和或门,用于根据加法器的输出电压和参考电压vref的值产生控制加法器中开关和积分器电容值的极性信号。

20.其中,第一开关sw1一端接第一输入端口vip1,另一端接第一电容ca1的左端;第二开关sw2一端接第二输入端口vip2,另一端接第二电容ca2的左端;第三开关sw3一端接第三输入端口vin2,另一端接第三电容ca3的左侧;第四开关sw4一端接第四输入端口vin1,另一端接第四电容ca4的左侧。

21.第五开关sw5一端接参考电压vcm,另一端接第一电容ca1的左端;第六开关sw6一端接参考电压vcm,另一端接第二电容ca2的左端;第七开关sw7一端接参考电压vcm,另一端接第三电容ca3的左端,第八开关sw8一端接参考电压vcm,另一端接第四电容ca4的左端;第九开关sw9一端接参考电压vcm,另一端接第二电容ca2的右端;第十开关sw10一端接参考电压vcm,另一端接第三电容ca3的左端。

22.第一比较器com1正端输入接加法器第一输出端口vop,负端输入接参考电压vref;第二比较器com2正端输入接加法器第二输出端口von,负端输入接参考电压vref;第一比较器com1,第二比较器com2的输出接或门or输入端,或门的输出为加法器的第三输出端口vc。

23.该电路采用两相不交叠时钟工作:

24.在ck2的高相位中,开关sw5、sw6、sw7、sw8、sw9、sw10闭合,开关sw1、sw2、sw3、sw4断开,电容ca1、ca2、ca3、ca4上的电荷被清零,加法器的输出电压vop=vcm,von=vcm。

25.在ck1的高相位中,开关sw1、sw2、sw3、sw4闭合,开关sw5、sw6、sw7、sw8、sw9、sw10断开,根据输入信号vip1、vip2、vin1、vin2以及电容ca1、ca2、ca3、ca4的值,得到开关电容电路的多路信号求和电压:

[0026][0027][0028]

多路信号求和电压vop,von和参考电压vref分别接到比较器com1和com2的正端和负端。比较将判断求和电压和参考电压之差的极性,两个比较器的输出信号最后通过或门or输出相应的逻辑电平vc,最后用信号vc控制第一级积分器的开关来改变积分器的采样电容值,避免调制器工作在过载状态。

[0029]

如图3所示为本发明应用于sigma-delta调制器的示例图。

[0030]

当加法器的求和电压vop和von的值小于参考电压vref时,极性信号vc为低电平,其值为地端电压,表示整个调制器工作正常,第一级积分器的采样电容值保持cs1+cs3不变,当加法器的求和电压vop或von大于参考电压vref时,加法器输出的极性信号vc为高电平,其值为电源电压,表示输入信号幅度过大,调制器已经工作在过载状态,控制信号vc将第一级积分器的采样电容值调整为cs1,减小第一级积分器的系数,使整个调制器在此输入幅度下摆脱过载状态,回到稳定,避免了输出信号信噪比大幅度下降的现象发生。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1