一种加速起振LC振荡器的制作方法

一种加速起振lc振荡器

技术领域

1.本发明涉及一种lc振荡器。

背景技术:

2.对于模拟电路,lc振荡器是一个重要模块,它可以产生稳定的时钟信号,而时钟信号是时序电路不可或缺的一部分。对于某一个芯片而言,上电时间是一个非常重要的指标,常常需要尽可能的缩短上电时间来使得芯片更快速响应。在很多应用中,上电时间取决于lc振荡器的起振时间,因此缩短lc振荡器的起振时间对改善电子系统的应用至关重要。

3.如图1所示,传统lc振荡器在起振时,其初始能量来自于电路在接入电源时瞬间产生的扰动和器件自身的噪声,然而由于lc网络中电感的高品质因素,其等效于一个带宽很窄的带通滤波器,噪声能量只有极少部分能灌输到lc谐振腔,因此其振荡的幅值正反馈累积的比较慢,需要较长一段时间才能到稳定状态。因此对高q值的振荡器,其上电时间比较慢,这给很多应用的上电时间带来了不利。

4.对于谐振回路的快速起振,现有方法中有通过加入各种频谱分量的脉冲以加快起振速度,也有通过输入与谐振频率一致的周期电流信号以加速起振,还可以在lc谐振回路的两端施加大电压差以加速起振。然而,以上方法的实现都需要额外的信号激励,这样就要求电路在产生所需时钟信号的同时还要产生其他信号,无疑会增大电路的复杂度,也增加了功耗。

技术实现要素:

5.发明目的:针对上述现有技术,提出一种加速起振lc振荡器,在不用额外的信号激励的情况下,解决传统振荡器起振速度慢的问题。

6.技术方案:一种加速起振lc振荡器,包括传统lc振荡电路和辅助快速起振电路;所述辅助快速起振电路包括峰值检测电路和品质因数控制电路,所述峰值检测电路用于对所述传统lc振荡电路起振时的实时最大幅值进行检测,所述品质因数控制电路用于在所述传统lc振荡电路起振时串入电阻来减小谐振回路的品质因数,从而加速振荡器起振。

7.进一步的,所述辅助快速起振电路还包括能量注入电路,用于在谐振回路中串入电阻时为谐振电路注入能量,补偿加入电阻后带来的环路增益减小。

8.进一步的,所述品质因数控制电路包括运算放大器m2、pmos管q7和电阻r1;电阻r1串联在谐振回路中,运算放大器m2的正输入端接入所述峰值检测电路的输出电压,运算放大器m2的负输入端接入参考电压vref;运算放大器m2的输出端与pmos管q7的栅端相连,pmos管q7的源端和漏端并接在电阻r1两端。

9.进一步的,所述峰值检测电路包括二极管d1与电容c2,二极管d1的正极连接谐振回路,二极管d1的负极作为峰值检测电路的输出,电容c2连接在二极管d1的负极和地之间。

10.进一步的,所述能量注入电路包括运算放大器m1和pmos管q6;运算放大器m1的正输入端接入参考电压vref,运算放大器m1的负输入端接入所述峰值检测电路的输出电压;

运算放大器m1的输出端与pmos管q6的栅端相连,pmos管q6的源端接地,pmos管q6的漏端与所述传统lc振荡电路的差分放大电路连接。

11.有益效果:本发明的一种加速起振lc振荡器,通过降低起振阶段谐振回路的品质因数以达到加速起振的目的,在不需要额外产生信号源的情况下可以有效加快lc振荡电路的起振速度,从而提高电子系统的上电速度,改善了时延特性。具体的,在信号起振时,给电感串联电阻降低回路的品质因数,使得更多的噪声注入谐振腔以加速起振,同时给电路产生负阻的尾电流源注入谐振电路以补偿串联电阻带来的负阻降低,保证回路能够起振的同时达到快速起振的目的。

附图说明

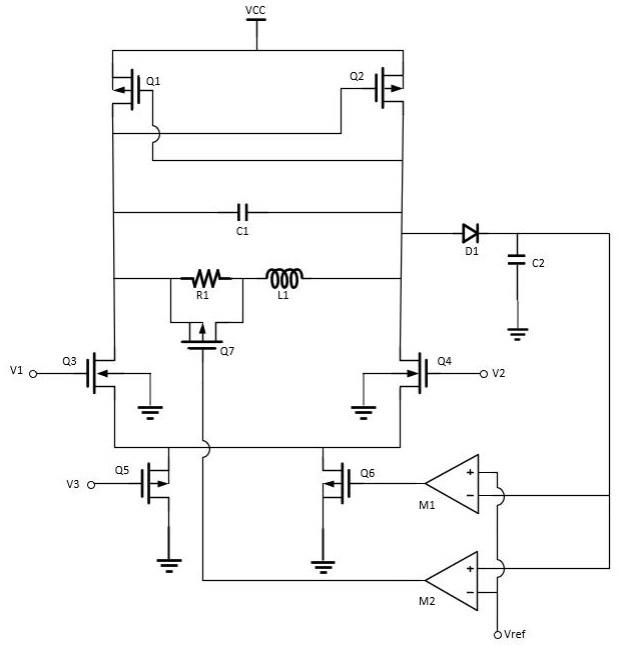

12.图1为传统lc振荡器的电路结构图;图2为本发明加速起振lc振荡器的电路结构图。

具体实施方式

13.下面结合附图对本发明做更进一步的解释。

14.一种加速起振lc振荡器,包括传统lc振荡电路和辅助快速起振电路。传统lc振荡电路包括交叉耦合电路、谐振回路以及差分放大电路。辅助快速起振电路包括峰值检测电路、品质因数控制电路以及能量注入电路。峰值检测电路用于对传统lc振荡电路起振时的实时最大幅值进行检测,为后续判断能量注入电路与品质因数控制电路是否开始工作做准备;品质因数控制电路用于在传统lc振荡电路起振时串入电阻来减小谐振回路的品质因数,从而加速振荡器起振;能量注入电路用于在谐振回路中串入电阻时为谐振电路注入能量,补偿加入电阻后带来的环路增益减小。

15.如图2所示,本实施例中,加速起振lc振荡器中的传统lc振荡电路包括pmos管q1、pmos管q2、pmos管q5、nmos管q3、nmos管q4、电容c1以及电感l1。pmos管q1和pmos管q2源端接供电电压vcc,栅端与对方的漏端相连,形成交叉耦合电路,提供负阻;pmos管q1和pmos管q2的漏端又分别与nmos管q3和nmos管q4的漏端相连,nmos管q3和nmos管q4的栅端分别接输入电压v1与v2,以提供电压,nmos管q3和nmos管q4的源端都与pmos管q5的漏端相连,构成差分放大器电路;pmos管q5的栅极接输入电压v3,为差分放大器提供电流,pmos管q5的源端接地;电容c1与电感l1并接于pmos管q1、pmos管q2的漏端以及nmos管q3、nmos管q4的漏端之间,形成谐振回路。当电路上电时产生的细微扰动会作为激励在谐振回路中不断振荡放大,直至形成稳定的信号。

16.峰值检测电路包括二极管d1与电容c2,二极管d1的正极连接谐振回路,二极管d1的负极作为峰值检测电路的输出,电容c2连接在二极管d1的负极和地之间。

17.品质因数控制电路包括运算放大器m2、pmos管q7和电阻r1。电阻r1串联在谐振回路中,运算放大器m2的正输入端接入峰值检测电路的输出电压,负输入端接入参考电压vref;运算放大器m2的输出端与pmos管q7的栅端相连,pmos管q7的源端和漏端并接在电阻r1两端。当峰值检测电路输出电压小于参考电压vref时,pmos管q7处于关断状态,此时电阻r1接入谐振回路,品质因数降低,起振速度加快。当峰值检测电路输出电压大于参考电压vref时,pmos管q7打开,此时电阻r1相当于短路,电阻r1不再串接入谐振回路。

18.能量注入电路包括运算放大器m1和pmos管q6。运算放大器m1的正输入端接入参考电压vref,运算放大器m1的负输入端接入峰值检测电路的输出电压。运算放大器m1的输出端与pmos管q6的栅端相连,pmos管q6的源端接地,pmos管q6的漏端与nmos管q3以及nmos管q4的源端相连。当峰值检测电路输出电压小于参考电压vref时,运算放大器m1输出电压为pmos管q6供电,形成尾电流源为谐振电路注入能量,补偿加入电阻后带来的环路增益减小。当峰值检测电路输出电压大于参考电压vref时,运算放大器m1没有输出电压,谐振回路也就不再有能量注入,此时品质因数控制电路串入的电阻r1也被短路,电路的各个参数恢复初值,谐振回路回到传统振荡状态。

19.以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1