转移状态输出装置、时间数字转换器以及A/D转换电路的制作方法

转移状态输出装置、时间数字转换器以及a/d转换电路

技术领域

1.本发明涉及转移状态输出装置、时间数字转换器以及a/d转换电路。

背景技术:

2.在专利文献1中记载了如下时间数字转换器:具有连接有多个延迟元件的多级延迟线、逻辑电路以及状态机,具备基于触发信号开始状态转移的状态转移部、与基准信号同步地从状态转移部获取并保持表示内部状态的状态信息的转移状态获取部、和基于状态信息而算出与内部状态的转移次数相对应的时间数字值的运算部。

3.专利文献1:日本特开2020-178153号公报

4.专利文献1所记载的时间数字转换器起因于针对状态转移部所包括的多级延迟线、逻辑电路、状态机等的每个结构要素而延迟时间、动作速度不同,因而各内部状态持续的时间会产生比较大的差异。因此,为了改善时间数字值相对于内部状态的转移次数的线性,而预先作成对各内部状态的持续时间进行测量而得到的校正信息并存储在存储部,通过使用了该校正信息的数值运算来校正内部状态的转移次数。因此,在专利文献1所记载的时间数字转换器中,需要用于改善线性的校正电路,并且需要花费作成校正电路的运算所需要的校正信息的精力。

技术实现要素:

5.本发明的转移状态输出装置的一方式,具备:环状振荡电路,基于触发信号开始振荡;状态机,根据所述环状振荡电路的状态变化而状态发生变化;转移状态获取部,与基准信号同步地获取并保持包括从所述环状振荡电路输出的信号和从所述状态机输出的信号的状态信息;以及内部状态算出部,基于所述转移状态获取部保持的所述状态信息,算出与所述环状振荡电路的状态变化的次数相对应的内部状态,从所述内部状态从第一内部状态转移到第二内部状态起到再次转移到所述第一内部状态为止的时间比更新所述转移状态获取部保持的所述状态信息的时间的间隔长。

6.本发明的时间数字转换器的一方式,具备:所述转移状态输出装置的一方式;以及运算部,对所述内部状态的转移次数进行运算,并基于所述转移次数算出与所述触发信号的时间事件对应的时间数字值。

7.本发明的a/d转换电路的一方式,是将输入的模拟信号转换为数字信号并输出的a/d转换电路,具备:所述时间数字转换器的一方式;基准波形信号生成电路,基于所述基准信号生成基准波形信号;以及比较器,对所述模拟信号的电压和所述基准波形信号的电压进行比较并输出所述触发信号,所述a/d转换电路输出基于所述时间数字值的所述数字信号,由所述时间数字转换器算出所述时间数字值。

8.本发明的a/d转换电路的一方式,是将输入的模拟信号转换为数字信号并输出的a/d转换电路,具备:所述时间数字转换器的一方式;采样保持电路,对所述模拟信号的电压进行采样并保持;基准波形信号生成电路,基于所述基准信号生成基准波形信号;以及比较

器,对所述采样保持电路保持的电压和所述基准波形信号的电压进行比较并输出所述触发信号,所述a/d转换电路输出基于所述时间数字值的所述数字信号,由所述时间数字转换器算出所述时间数字值。

附图说明

9.图1是示出第一实施方式的时间数字转换器的功能结构的图。

10.图2是示出第一实施方式中的转移状态输出装置的结构例的图。

11.图3是示出解码器的真值表的一例的图。

12.图4是示出解码器的真值表的另一例的图。

13.图5是示出转移状态输出装置的动作的一例的时序图。

14.图6是示出运算部的结构例的图。

15.图7是示出计数部的结构例的图。

16.图8是示出计数值保持部以及累加部的结构例的图。

17.图9是示出相位差pd与时间数字值td的关系的图。

18.图10是示出相位差pd与时间数字值td的关系的图。

19.图11是第二实施方式的时间数字转换器的功能框图。

20.图12是示出第二实施方式中的转移状态输出装置的结构例的图。

21.图13是示出解码器的真值表的一例的图。

22.图14是示出解码器的真值表的一例的图。

23.图15是示出转移状态输出装置的动作的一例的时序图。

24.图16是示出转移状态输出装置的动作的一例的时序图。

25.图17是示出解码器的真值表的另一例的图。

26.图18是示出解码器的真值表的另一例的图。

27.图19是示出转移状态输出装置的动作的一例的时序图。

28.图20是示出解码器的真值表的另一例的图。

29.图21是示出解码器的真值表的另一例的图。

30.图22是示出转移状态输出装置的动作的一例的时序图。

31.图23是示出第三实施方式中的转移状态输出装置的结构例的图。

32.图24是示出转移状态输出装置的动作的一例的时序图。

33.图25是示出计数部的结构例的图。

34.图26是示出相位差pd与时间数字值td的关系的图。

35.图27是示出第四实施方式中的转移状态输出装置的结构例的图。

36.图28是示出转移状态输出装置的动作的一例的时序图。

37.图29是第五实施方式的时间数字转换器的功能框图。

38.图30是第五实施方式的时间数字转换器的另一功能框图。

39.图31是示出运算部的结构例的图。

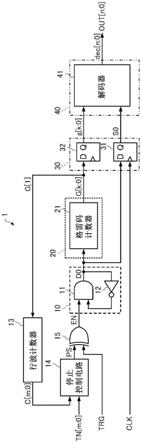

40.图32是示出第一实施方式的a/d转换电路的结构的图。

41.图33是示出各种信号的波形的一例的图。

42.图34是示出第二实施方式的a/d转换电路的结构的图。

43.图35是示出各种信号的波形的一例的图。

44.附图标记说明:

[0045]1…

转移状态输出装置,10

…

环状振荡电路,11

…

逻辑与电路;12

…

逻辑反转电路,13

…

行波计数器,14

…

停止控制电路,15

…

异或电路,20

…

状态机,21

…

格雷码计数器,30

…

转移状态获取部,31、31-0~31-q

…

d触发器,32

…

寄存器,40

…

内部状态算出部,41

…

解码器,42

…

解码器,50

…

运算部,60

…

计数部,61

…

寄存器,62

…

减法器,63

…

累加器,64

…

乘法器,65

…

虚拟化部,70

…

计数值保持部,71

…

寄存器,80

…

累加部,81

…

加法器,82

…

寄存器,90

…

转换部,92

…

时间数字值生成部,100

…

时间数字转换器,101

…

采样保持电路,102

…

基准波形信号生成电路,103

…

比较器,200

…

多级延迟线,201-1~201-q

…

延迟元件,300

…

a/d转换电路。

具体实施方式

[0046]

以下,使用附图对本发明的优选的实施方式详细进行说明。另外,在以下说明的实施方式并不对权利要求所记载的本发明的内容不当地进行限定。此外,在以下说明的所有结构并不一定都是本发明的必须结构要件。

[0047]

1.时间数字转换器

[0048]

1-1.第一实施方式

[0049]

1-1-1.时间数字转换器的结构

[0050]

图1是第一实施方式的时间数字转换器的功能框图。如图1所示,第一实施方式的时间数字转换器100具备转移状态输出装置1和运算部50。转移状态输出装置1具备环状振荡电路10、状态机20、转移状态获取部30和内部状态算出部40。

[0051]

环状振荡电路10基于触发信号trg开始振荡。

[0052]

状态机20根据环状振荡电路10的状态变化而状态发生变化。

[0053]

转移状态获取部30与基准信号clk同步地对包括从环状振荡电路10输出的信号和从状态机20输出的信号在内的状态信息进行获取并保持。

[0054]

内部状态算出部40基于转移状态获取部30保持的状态信息,算出与环状振荡电路10的状态变化的次数相对应的内部状态。

[0055]

转移状态输出装置1输出内部状态算出部40算出的表示内部状态的n+1位(bit)的状态信号out[n:0]。n是0以上的任意整数。

[0056]

运算部50基于状态信号out[n:0]对内部状态的转移次数进行运算,并基于该转移次数算出与触发信号trg的时间事件对应的时间数字值td。运算部50例如由mpu、fpga等构成。mpu是micro processing unit(微处理单元)的缩略。此外,fpga是field programmable gate array(现场可编程门阵列)的缩略。如后述的那样,在本实施方式中,运算部50基于时间经过而对状态转移次数加权,并对加权后的状态转移次数进行累加,从而生成与基准信号clk的时间事件和触发信号trg的时间事件的相位差对应的时间数字值td。

[0057]

触发信号trg的时间事件是指触发信号trg发生变化的定时(timing),例如可以是触发信号trg的上升沿或下降沿,也可以是触发信号trg的上升沿以及下降沿。同样地,基准信号clk的时间事件是指基准信号clk发生变化的定时,例如,可以是基准信号clk的上升沿或下降沿,也可以是基准信号clk的上升沿以及下降沿。

[0058]

另外,在以下,设为触发信号trg的时间事件是上升沿以及下降沿、基准信号clk的时间事件是上升沿来进行说明。

[0059]

1-1-2.转移状态输出装置1的结构

[0060]

图2是示出转移状态输出装置1的结构例的图。在图2的例子中,转移状态输出装置1具备逻辑与电路11、逻辑反转电路12、行波计数器13、停止控制电路14、异或电路15、格雷码计数器21、d触发器31、寄存器32以及解码器41。

[0061]

逻辑与电路11输出从异或电路15输出的使能信号en与从逻辑反转电路12输出的信号的逻辑与信号。从逻辑与电路11输出的信号在使能信号en为低电平时变为低电平,在使能信号en为高电平时变为与从逻辑反转电路12输出的信号相同的逻辑电平。

[0062]

逻辑反转电路12将从逻辑与电路11输出的信号的逻辑电平反转而得的信号输出。因此,在使能信号en为高电平时,从逻辑与电路11输出的信号的逻辑电平交替地重复低电平和高电平。即,由逻辑与电路11和逻辑反转电路12构成环状振荡电路10,环状振荡电路10将从逻辑与电路11输出的信号作为振荡信号d0输出。能够认为振荡电路d0的逻辑电平的变化相当于环状振荡电路10的状态的变化。

[0063]

格雷码计数器21对从环状振荡电路10输出的振荡信号d0的两边沿进行计数,输出与计数值相对应的k+1位的格雷码信号g[k:0]。格雷码信号g[k:0]是2位以上不会同时发生变化的信号。由于能够认为定时地格雷码信号g[k:0]的值的变化相当于格雷码计数器21的状态的变化,因此由格雷码计数器21构成状态机20。由格雷码计数器21构成的状态机20在从任意状态转移到下一个状态时,格雷码信号g[k:0]的k+1位中仅1位发生变化。即,状态机20的状态转移前后的汉明距离是1。

[0064]

行波计数器13对从格雷码计数器21输出的格雷码信号g[k:0]的位1的信号g[1]的上升沿的数量进行计数,输出m+1位的计数信号c[m:0]。m是0以上的任意整数。另外。行波计数器13可以对信号g[1]的下降沿的数量进行计数,也可以对信号g[1]的逻辑电平的反转次数进行计数。此外,行波计数器13可以对振荡信号d0的上升沿或下降沿的数量进行计数,也可以对振荡信号d0的逻辑电平的反转次数进行计数。

[0065]

停止控制电路14输出如下的停止控制信号ps:在每当从行波计数器13输出的计数信号c[m:0]的值的增量与m+1位的停止设定信号tn[m:0]的值一致时,进行反转的停止控制信号ps。

[0066]

异或电路15输出触发信号trg与从停止控制电路14输出的停止控制信号ps的异或信号ex即使能信号en。使能信号en在触发信号trg的逻辑电平与停止控制信号ps的逻辑电平不同时变为高电平,在触发信号trg的逻辑电平与停止控制信号ps的逻辑电平相同时变为低电平。

[0067]

d触发器31与基准信号clk的上升沿同步地获取振荡信号d0,并保持与振荡信号d0的值相对应的信号s0。

[0068]

寄存器32是由k+1个d触发器构成的k+1位的寄存器,与基准信号clk的上升沿同步地获取格雷码信号g[k:0],并保持与格雷码信号g[k:0]的值相对应的信号g[k:0]。

[0069]

由于振荡信号d0表示环状振荡电路10的状态,格雷码信号g[k:0]表示构成状态机20的格雷码计数器21的状态,因此由d触发器31和寄存器32构成转移状态获取部30。

[0070]

解码器41对由d触发器31保持的信号s0和寄存器32保持的信号g[k:0]构成的k+2

位的信号进行解码,输出n+1位的解码信号dec[n:0]。n是1以上的任意整数。

[0071]

由于信号s0表示基准信号clk的上升沿的定时处的环状振荡电路10的状态,信号g[k:0]表示基准信号clk的上升沿的定时处的状态机20的状态,因此能够认为对由信号s0和信号g[k:0]构成的信号解码而得的解码信号dec[n:0]相当于表示基准信号clk的上升沿的定时处的转移状态输出装置1的内部状态的信号。即,由解码器41构成内部状态算出部40。

[0072]

而且,转移状态输出装置1将解码信号dec[n:0]作为状态信号out[n:0]输出。

[0073]

图3是示出解码器41的真值表的一例的图。在图3的例子中,k=2、n=3。在图3中,0表示低电平,1表示高电平。由于解码信号dec[3:0]相当于表示基准信号clk的上升沿的内部状态的信号,因此在图3的例子中,每当状态机20的状态发生变化时,内部状态的值从0逐一增加到15,内部状态的值在15的下一个返回到0。即,在图3的例子中,定义十六个内部状态。而且,十六个内部状态在振荡信号d0的逻辑电平发生变化的定时和解码信号dec[n:0]的值发生变化的定时的任一方时依次转移。由于振荡信号d0的周期大致恒定,不依赖于解码信号dec[n:0]的值而解码器41的延迟时间大致恒定,因此能够缩小十六个内部状态的持续时间的差异。只是,当解码器41的延迟时间比振荡信号d0的周期的1/4的时间大时,解码信号dec[n:0]的值为奇数的八个内部状态的持续时间变得相对长,易于被转移状态获取部30获取。另一方面,解码信号dec[n:0]的值为偶数的八个内部状态的持续时间变得相对短,不易被转移状态获取部30获取。因此,期望使解码器41的延迟时间与振荡信号d0的周期的1/4的时间一致,但在其有困难的情况下,在图3的例子中,由转移状态获取部30获取的内部状态的频率会产生偏差。与此相对,如果使内部状态与振荡信号d0的逻辑电平反转的定时、即环状振荡电路10的状态发生变化的定时同步地发生变化,则能够与解码器41的延迟时间无关地使各内部状态的持续时间之差极其缩小。

[0074]

图4是示出定义这样的内部状态的解码器41的真值表的一例的图。在图4的例子中,k=2、n=2。在图4中,0表示低电平,1表示高电平。在图4的例子中,每当环状振荡电路10的状态发生变化时,内部状态的值从0逐一增加到7,内部状态的值在7的下一个返回到0。即,在图4的例子中,定义八个内部状态。而且,由于内部状态必定在振荡信号d0的逻辑电平反转的定时进行转移,因此八个内部状态的持续时间与振荡信号d0的半周期的时间一致,其差极其小。因此,在图4的例子中,虽然被定义的内部状态的数量比图3的例子少,但是由转移状态获取部30获取的内部状态的频率不会产生偏差。

[0075]

图5是示出转移状态输出装置1的动作的一例的时序图。在图5的例子中,每当触发信号trg的逻辑电平反转时,使能信号en从低电平转移到高电平,环状振荡电路10的振荡开始。这之后,每当计数信号c[m:0]的值的增量与停止设定信号tn[m:0]的值即2一致时,使能信号en从高电平转移到低电平,环状振荡电路10的振荡停止。具体而言,在第一次的使能信号en为高电平的期间内,当内部状态转移二十次时,环状振荡电路10的振荡停止,在第二次以后的使能信号en为高电平的期间内,当内部状态转移三十二次时,环状振荡电路10的振荡停止。即,在第二次以后的使能信号en为高电平的期间内,当转移状态输出装置1的状态转移次数达到上限值即32时,停止状态转移。

[0076]

在解码器41的真值表为图3的情况下,输出case(事件)1的状态信号out[3:0],在解码器41的真值表为图4的情况下,输出case2的状态信号out[2:0]。在图5的例子中,基准信号clk的周期是振荡信号d0的周期的2.5倍。而且,在图3的例子中,由于内部状态在振荡

信号d0的一个周期的期间内转移四次,因此内部状态在基准信号clk的一个周期的期间内转移十次。因此,在使能信号en为高电平的期间内,在基准信号clk的上升沿的定时,case1的状态信号out[3:0]的值逐十发生变化。此外,在图4的例子中,由于内部状态在振荡信号d0的一个周期的期间内转移两次,因此内部状态在基准信号clk的一个周期的期间内转移五次。因此,在使能信号en为高电平的期间内,在基准信号clk的上升沿的定时,case2的状态信号out[2:0]的值逐五发生变化。

[0077]

在本实施方式中,从内部状态从任意第一内部状态转移到第二内部状态起到再次转移到第一内部状态为止的时间比更新转移状态获取部30保持的状态信息的时间的间隔长。到再次转移到第一内部状态为止的时间也可以称为到再次出现第一内部状态为止的时间。例如,在图3的例子中,当将振荡信号d0为低电平且所有格雷码信号g[2:0]的位为低电平的状态作为第一内部状态时,振荡信号d0为高电平且所有格雷码信号g[2:0]的位为低电平的状态是第二内部状态。此外,在图4的例子中,当将振荡信号d0为低电平且所有格雷码信号g[2:0]的位1、0均为低电平的状态作为第一内部状态时,振荡信号d0为高电平且格雷码信号g[2:0]的位2、1均为低电平的状态是第二内部状态。此外,更新转移状态获取部30保持的状态信息的时间的间隔是基准信号clk的一个周期的时间。因此,在图3的例子中,由于存在十六个内部状态,因此内部状态转移十五次所需的时间比基准信号clk的一个周期的时间长,在图4的例子中,由于存在八个内部状态,因此内部状态转移七次所需的时间比基准信号clk的一个周期的时间长。

[0078]

通过满足从内部状态从任意第一内部状态转移到第二内部状态起到再次转移到第一内部状态为止的时间比更新转移状态获取部30保持的状态信息的时间的间隔长这一条件,从而转移状态输出装置1的后一级的运算部50能够简单地求出基准信号clk的一个周期的期间的内部状态的转移次数。与此相对,假如不满足该条件,则运算部50需要确定内部状态循环一遍的次数,并通过规定的计算式求出基准信号clk的一个周期的期间的内部状态的转移次数。

[0079]

1-1-3.运算部的结构

[0080]

图6是示出运算部50的结构例的图。如图6所示,运算部50具有计数部60、计数值保持部70、累加部80以及转换部90。

[0081]

计数部60基于状态信号out[n:0],输出与触发信号trg对应的计数值cnt。

[0082]

计数值保持部70与基准信号clk同步地读入从计数部60输出的计数值cnt,并作为计数值dcnt保持。

[0083]

累加部80通过与基准信号clk同步地对保持在计数值保持部70的计数值dcnt进行累加,从而生成与基准信号clk的时间事件和触发信号trg的各自的时间事件的相位差对应的时间数字值td。另外,计数值保持部70以及累加部80例如通过被输入未图示的复位信号等而被初始化。

[0084]

转换部90将从累加部80输出的时间数字值td转换为时间数字值tdx。例如,转换部90可以对时间数字值td进行规定的缩放而转换为时间数字值tdx,也可以按照规定的转换式或者表信息将时间数字值td转换为时间数字值tdx。另外,运算部50也可以不包括转换部90。

[0085]

而且,由运算部50运算出的时间数字值td或者时间数字值tdx经由未图示的端子

而从时间数字转换器100向外部输出。

[0086]

图7是示出计数部60的结构例的图。计数部60具有寄存器61、减法器62、累加器63以及乘法器64。

[0087]

寄存器61由n+1个d触发器构成,与基准信号clk的上升沿同步地读入并保持状态信号out[n:0]。

[0088]

减法器62从状态信号out[n:0]的值减去寄存器61保持的信号的值。在此,从减法器62输出的信号c1的值相当于在基准信号clk的最近一个周期的时间内转移状态输出装置1的内部状态转移的次数。

[0089]

累加器63与基准信号clk的上升沿同步地对常数值a进行累加。因此,累加器63输出权重系数信号wc,该权重系数信号wc具有对基准信号clk的上升沿进行计数而得的值的a倍的值。权重系数信号wc的值随触发信号trg的上升沿或下降沿产生后的经过时间,值单调增加或单调减少。具体而言,如果常数值a是正数,则权重系数信号wc的值随经过时间单调增加,如果常数值a是负数,则权重系数信号wc的值随经过时间单调减少。

[0090]

乘法器64将信号c1的值与权重系数信号wc的值相乘,算出计数值cnt。计数值cnt从计数部60输出。

[0091]

在图7中,省略了图示以及说明,但在转移状态输出装置1的状态转移停止的情况下等,也可以向寄存器61以及累加器63输入将保持的值初始化为0的复位信号。

[0092]

另外,在本实施方式中,通过将在基准信号clk的最近一个周期的时间内转移状态输出装置1的内部状态转移的次数与权重系数信号wc的值相乘,来算出计数值cnt,但也可以通过将在从向时间数字转换器100输入触发信号trg起到转移状态输出装置1输出状态信号out[n:0]为止的期间内转移状态输出装置1的内部状态转移的次数与权重系数信号wc的值相乘,来算出计数值cnt。

[0093]

图8是示出计数值保持部70以及累加部80的结构例的图。如图8所示,计数值保持部70包括由多个d触发器构成的寄存器71。寄存器71与基准信号clk的上升沿同步地获取从计数部60输出的计数值cnt,并作为计数值dcnt保持。

[0094]

累加部80包括加法器81和由多个d触发器构成的寄存器82。加法器81将寄存器71保持的计数值dcnt和从寄存器82输出的值相加。寄存器82与基准信号clk的上升沿同步地读入从加法器81输出的值,并作为时间数字值td保持。

[0095]

另外,在图8中省略图示,但也可以向寄存器71以及寄存器82分别输入将保持的值初始化为0的复位信号。由此,时间数字值td也被初始化为0。

[0096]

在本实施方式中,基准信号clk的时间事件与触发信号trg的时间事件被独立地设定。即,基准信号clk的时间事件与触发信号trg的时间事件是不同步的。而且,时间数字值td对应于基准信号clk的时间事件和触发信号trg的时间事件的相位差pd。例如,时间数字值td或者时间数字值tdx被作为针对以基准信号clk的时间事件为基准的触发信号trg的时间事件的时间戳而使用。

[0097]

1-1-4.基准信号与触发信号的相位差与时间数字值的关系

[0098]

图9是示出基准信号clk的时间事件与触发信号trg的时间事件的相位差pd与时间数字值td的关系的图。在图9中还示出了状态信号out的值、c1的值、权重系数信号wc的值、计数值cnt以及计数值dcnt。此外,在图9的例子中,转移状态输出装置1的状态转移次数的

上限值是64,常数值a是1。此外,t是基准信号clk的一个周期的时间。

[0099]

如图9所示,每当产生基准信号clk的时间事件时,基于状态信号out、信号c1以及权重系数信号wc生成计数值cnt,将保持有计数值cnt的计数值dcnt累加,而时间数字值td增加。在将基准信号clk的时间事件作为第0个上升沿时,在相位差pd是t

×

1.5的情况下,在第十个上升沿,表示产生触发信号trg的时间事件后的转移状态输出装置1的内部状态的转移次数的状态信号out的值达到上限值即64。而且,在基准信号clk的第十二个上升沿以后,时间数字值td变为377。

[0100]

此外,在相位差pd是t

×

1.7的情况下,在基准信号clk的第十个上升沿,状态信号out的值达到上限值即64,在基准信号clk的第十二个上升沿以后,时间数字值td变为391。

[0101]

此外,在相位差pd是t

×

2.7的情况下,在基准信号clk的第十一个上升沿,状态信号out的值达到上限值即64,在基准信号clk的第十三个上升沿以后,时间数字值td变为455。

[0102]

此外,在相位差pd是t

×

3.7的情况下,在基准信号clk的第十二个上升沿,状态信号out的值达到上限值即64,在基准信号clk的第十四个上升沿以后,时间数字值td变为519。

[0103]

图10是示出在图9中相位差pd与在转移状态输出装置1的状态转移次数达到上限值后的时间数字值td的关系的图。如图10所示,相位差pd为t

×

1.5、t

×

1.7、t

×

2.7、t

×

3.7情况下的时间数字值td,分别是377、391、455、519,时间数字值td的差值δtd分别是+14、+64、+64。在图9的例子中,由于常数值a是正数,因此越随着时间的经过,则权重系数信号wc的值越变大。而且,由于相位差pd越大,则转移状态输出装置1的状态转移次数达到上限值即64的时间越迟,因此当相位差pd仅增加基准信号clk的一个周期的时间t时,时间数字值td仅增加状态转移次数的上限值即64。

[0104]

1-1-5.作用效果

[0105]

在以上所说明的第一实施方式的时间数字转换器100中,在转移状态输出装置1中,由于环状振荡电路10是极其简单的结构,因此状态变化的周期大致恒定。此外,由于状态机20不包括在环状振荡电路10的振荡环中,且根据环状振荡电路10的状态变化而状态发生变化,因此状态机20的状态变化的周期也大致恒定。因此,环状振荡电路10、状态机20的各状态持续的时间大致恒定。因此,根据第一实施方式的时间数字转换器100,在转移状态输出装置1中,由于能够降低从包括从环状振荡电路10输出的信号和从状态机20输出的信号的状态信息得到的各内部状态持续的时间的差异,因此运算部50不进行校正内部状态的转移次数的运算,而能够算出较高的精度的时间数字值td。此外,由于运算部50不需要进行校正运算,因此从输入触发信号trg起到算出时间数字值td为止的时间变短,并且不需要花费作成校正运算所需要的校正信息的精力。

[0106]

此外,在第一实施方式的时间数字转换器100中,在转移状态输出装置1中,如果使内部状态与环状振荡电路10的状态发生变化的定时同步地发生变化,则环状振荡电路10的状态发生变化的定时与内部状态发生变化的定时一对一地对应。因此,根据第一实施方式的时间数字转换器100,在转移状态输出装置1中,由于环状振荡电路10的状态变化的周期大致恒定,因此各内部状态持续的时间大致恒定,能够进一步降低各内部状态持续的时间的差异。

[0107]

此外,在第一实施方式的时间数字转换器100中,在转移状态输出装置1中,由于从内部状态从第一内部状态转移到第二内部状态起到再次转移到第一内部状态为止的时间比更新转移状态获取部30保持的状态信息的时间的间隔长,因此转移状态获取部30能够在状态转移循环一遍之前获取状态信息。因此,根据第一实施方式的时间数字转换器100,运算部50不需要确定内部状态在从转移状态获取部30获取状态信息起到获取下一个状态信息为止的期间内循环一遍的次数,因此能够简化运算部50的处理。

[0108]

此外,在第一实施方式的时间数字转换器100中,在转移状态输出装置1中,由于内部状态的转移前后的状态信息的汉明距离是1,因此转移状态获取部30能够获取与状态转移前后的两个状态的任一方对应的状态信息。因此,根据第一实施方式的时间数字转换器100,在转移状态输出装置1中,降低获取错误的状态信息的可能性,运算部50能够高精度地算出时间数字值td。

[0109]

此外,在第一实施方式的时间数字转换器100中,每当产生触发信号trg的时间事件时,由于在运算部50中计数部60、计数值保持部70以及累加部80不进行复位而能够无死区期间地动作,因此发挥基于δ∑调制的较高的噪声修整效果。因此,根据第一实施方式的时间数字转换器100,在转移状态输出装置1中,由于起因于各内部状态持续的时间的较小的差异等而产生的噪声分量通过噪声修整效果移位到高频侧,因此运算部50能够算出s/n比的较高的时间数字值td。

[0110]

1-2.第二实施方式

[0111]

以下,关于第二实施方式的时间数字转换器,对与第一实施方式同样的结构要素标注相同的附图标记,省略或简略与第一实施方式重复的说明,主要对与第一实施方式不同的内容进行说明。

[0112]

图11是示出第二实施方式的时间数字转换器100的功能框图。如图11所示,与第一实施方式同样,第二实施方式的时间数字转换器100具备转移状态输出装置1和运算部50,生成与基准信号clk的时间事件和触发信号trg的时间事件的相位差对应的时间数字值td。

[0113]

转移状态输出装置1具备环状振荡电路10、状态机20、转移状态获取部30、内部状态算出部40和多级延迟线200。由于环状振荡电路10以及状态机20的功能与第一实施方式是同样的,因此省略说明。

[0114]

与第一实施方式同样,环状振荡电路10基于触发信号trg开始振荡,状态机20根据环状振荡电路10的状态变化而状态发生变化。

[0115]

多级延迟线200构成为连接有多个延迟元件。向多级延迟线200输入从环状振荡电路10输出的信号。输入到多级延迟线200的信号在多个延迟元件中传输。

[0116]

转移状态获取部30与基准信号clk同步地对包括从环状振荡电路10输出的信号、从状态机20输出的信号和从多级延迟线200输出的信号的状态信息进行获取并保持。

[0117]

与第一实施方式同样,内部状态算出部40基于转移状态获取部30保持的状态信息,算出与环状振荡电路10的状态变化的次数相对应的内部状态。而且,转移状态输出装置1输出表示内部状态算出部40算出的内部状态的n+1位的状态信息out[n:0]。n是0以上的任意整数。

[0118]

与第一实施方式同样,运算部50基于状态信号out[n:0]来运算内部状态的转移次数,并基于该转移次数而算出与触发信号trg的时间事件对应的时间数字值td。另外,由于

运算部50的结构与第一实施方式是同样的,因此省略其图示以及说明。

[0119]

图12是示出第二实施方式的时间数字转换器100具备的转移状态输出装置1的结构例的图。在图12的例子中,转移状态输出装置1具备逻辑与电路11、逻辑反转电路12、行波计数器13、停止控制电路14、异或电路15、格雷码计数器21、q+1个d触发器31-0~31-q、寄存器32、解码器41、解码器42以及q个延迟元件201-1~201-q。q是2以上的整数。

[0120]

由于逻辑与电路11、逻辑反转电路12、行波计数器13、停止控制电路14、异或电路15、格雷码计数器21、寄存器32以及解码器41的功能与第一实施方式是同样的,因此省略其说明。

[0121]

q个延迟元件201-1~201-q呈链状连接,构成多级延迟线200。多级延迟线200具有一个输入端和q个输出端。这样的多级延迟线200也被称为带抽头的延迟线。延迟元件201-1~201-q分别是缓冲元件、逻辑反转元件。由于期望延迟元件201-1~201-q的延迟时间大致相等,因此作为延迟元件201-1~201-q使用相同的种类的元件。在以下,将所有延迟元件201-1~201-q作为缓冲元件来进行说明。

[0122]

多级延迟线200的最先的延迟元件201-1的输入端成为多级延迟线200的输入端。此外,延迟元件201-1~201-q的各自的输出端成为多级延迟线200的q个输出端。信号d1~dq从多级延迟线200的输入端侧起按顺序从多级延迟线200的q个输出端输出。

[0123]

向多级延迟线200的输入端输入振荡信号d0。振荡信号d0从低电平变化为高电平,高电平的信号d0在延迟元件201-1中传输,从而信号d1从低电平变化为高电平。而且,对于1以上、q以下的各整数i,高电平的信号di-1在延迟元件201-i中传输,从而信号di从低电平变化为高电平。即,高电平的信号依次在延迟元件201-1~201-q中传输下去,信号d1~dq依次从低电平变化为高电平。

[0124]

同样地,振荡信号d0从高电平变化为低电平,低电平的信号d0在延迟元件201-1中传输,从而信号d1从高电平变化为低电平。而且,对于1以上、q以下的各整数i,低电平的信号di-1在延迟元件201-i中传输,从而信号di从高电平变化为低电平。即,低电平的信号依次在延迟元件201-1~201-q中传输下去,信号d1~dq依次从高电平变化为低电平。

[0125]

d触发器31-0与基准信号clk的上升沿同步地获取振荡信号d0,并保持与振荡信号d0的值相对应的信号s0。此外,对于1以上、q以下的各整数i,d触发器31-i与基准信号clk的上升沿同步地获取从延迟元件201-i输出的信号di,并保持与信号di的值相对应的信号si。由于振荡信号d0表示环状振荡电路10的状态,q个信号d1~dq表示多级延迟线200的状态,格雷码信号g[k:0]表示构成状态机20的格雷码计数器21的状态,因此通过d触发器31-0~31-q和寄存器32构成转移状态获取部30。

[0126]

解码器42对由q+1个d触发器31-0~31-q分别保持的信号s0~sq和从解码器41输出的p+1位的解码信号dec[p:0]构成的p+q+2位的信号进行解码,输出n+1位的解码信号dec2[n:0]。p、n分别是1以上的任意整数。

[0127]

由于信号s0表示基准信号clk的上升沿的定时处的环状振荡电路10的状态,信号g[k:0]表示基准信号clk的上升沿的定时处的状态机20的状态,因此将由信号s0和解码信号dec[p:0]构成的信号解码而得的解码信号dec2[n:0]相当于表示基准信号clk的上升沿的定时处的转移状态输出装置1的内部状态的信号。即,由解码器41以及解码器42构成内部状态算出部40。

[0128]

而且,转移状态输出装置1将解码信号dec2[n:0]作为状态信号out[n:0]输出。

[0129]

图13以及图14是示出解码器42的真值表的一例的图。在图13以及图14的例子中,p=2、q=7、n=5。图13是解码信号dec2[5:0]的值为0到31的真值表,图14是解码信号dec2[5:0]的值为32到63的真值表。在图13以及图14中,0表示低电平,1表示高电平。此外,设为解码信号dec[2:0]的值是按照图4所示的真值表得到的。此外,p0是将信号s1~s7中逻辑电平与信号s0一致的信号的数量返回的函数,设为解码信号dec0[2:0]的值是通过函数p0得到的。

[0130]

在图13以及图14的例子中,解码信号dec2[5:0]的值为使解码信号dec[2:0]的值八倍并加上解码信号dec0[2:0]的值而得的值。解码信号dec2[5:0]相当于表示基准信号clk的上升沿的内部状态的信号,每当环状振荡电路10的状态或多级延迟线200的状态发生变化时,内部状态的值从0逐一增加到63,内部状态的值在63的下一个返回到0。即,在图13以及图14的例子中,相对于图4的例子,定义八倍的六十四个内部状态。

[0131]

而且,在图13以及图14的例子中,六十四个内部状态在振荡信号d0的逻辑电平发生变化的定时和从多级延迟线200输出的信号d1~d7的逻辑电平发生变化的定时的任一方时依次转移。由于振荡信号d0的周期大致恒定,q个延迟元件201-1~201-q的延迟时间大致相等,因此能够缩小六十四个内部状态的持续时间的差异。只是,当从多级延迟线200的最后一级的延迟元件201-q的逻辑电平发生变化的状态转移起到环状振荡电路10转移到下一个状态为止的时间较大时,解码信号dec2[n:0]的值为7、15、23、31、39、47、55、63的八个内部状态的持续时间比其他五十六个内部状态长。因此,由转移状态获取部30获取的内部状态的频率会产生偏差。因此,从多级延迟线200的最后一级的延迟元件201-q的状态转移起到环状振荡电路10转移到下一个状态为止的时间,优选在多级延迟线200所包括的多个延迟元件201-1~201-q的延迟时间的平均值以下。在延迟元件201-1~201-q的延迟时间相等的情况下,平均值与延迟元件201-1~201-q的各延迟时间相等。特别是,在该时间与多个延迟元件201-1~201-q的延迟时间的平均值一致时,六十四个内部状态的计测时间大致相等,由转移状态获取部30获取的内部状态的频率几乎不会产生偏差。

[0132]

另外,图13以及图14的真值表以多级延迟线200的延迟时间比振荡信号d0的半周期小为条件而成立。多级延迟线200的延迟时间是从振荡信号d0的逻辑电平发生变化起到根据振荡信号d0的逻辑电平的变化而从最后一级的延迟元件201-q输出的信号dq的逻辑电平发生变化为止的时间。

[0133]

图15以及图16是示出图13以及图14的真值表成立的情况下的转移状态输出装置1的动作的一例的时序图。图15的例子是到环状振荡电路10转移到下一个状态为止的时间与延迟元件201-1~201-q的延迟时间的平均值一致的、理想的情况。此外,图16的例子是到环状振荡电路10转移到下一个状态为止的时间比延迟元件201-1~201-q的延迟时间的平均值大的情况。在图15以及图16的例子中,基准信号clk的周期是振荡信号d0的周期的2.5倍。而且,由于内部状态在振荡信号d0的一个周期的期间内转移十六次,因此内部状态在基准信号clk的一个周期的期间内转移四十次。因此,在图15的例子和图16的例子中,虽然状态信号out[5:0]的值不同,但是在使能信号en为高电平的期间内,在基准信号clk的上升沿的定时,状态信号out[5:0]的值逐四十发生变化。

[0134]

这样,在图15以及图16中,状态信号out[5:0]的值的变化量相对于图5的例子成为

八倍即40。因此,运算部50生成的时间数字值td的分辨率提升八倍。一般而言,多级延迟线200包括q个延迟元件201-1~201-q,从而时间数字值td的分辨率变为不包括多级延迟线200的情况下的q+1倍。

[0135]

不过,在不满足多级延迟线200的延迟时间比振荡信号d0的半周期小这一条件的情况下,即、在多级延迟线200的延迟时间在振荡信号d0的半周期以上的情况下,在相比根据振荡信号d0的逻辑电平的变化而从最后一级的延迟元件201-q输出的信号dq的逻辑电平发生变化之前,振荡信号d0的逻辑电平再次发生变化。

[0136]

图17以及图18是示出定义这样的内部状态的解码器42的真值表的一例的图。在图17以及图18的例子中,p=2、q=7、n=6。图17是解码信号dec2[6:0]的值为1到32的真值表,图18是解码信号dec2[5:0]的值为33到64的真值表。在图17以及图18中,0表示低电平,1表示高电平。此外,设为解码信号dec[2:0]的值是按照图4所示的真值表得到的。此外,p0是将信号s1~s3中逻辑电平与信号s0一致的信号的数量返回的函数,p4是将信号s5~s7中逻辑电平与信号s4一致的信号的数量返回的函数,x4是在信号s0与信号s4的逻辑电平一致时返回4,不一致时返回0的函数。而且,设为解码信号dec0[3:0]的值是通过函数p0、函数p4与函数x4之和而得到的。

[0137]

在图17以及图18的例子中,解码信号dec2[6:0]的值为使解码信号dec[2:0]的值八倍并加上解码信号dec0[3:0]的值而得的值。解码信号dec2[6:0]相当于表示基准信号clk的上升沿的内部状态的信号,每当环状振荡电路10的状态或多级延迟线200的状态发生变化时,内部状态的值从0逐一增加到64,内部状态的值在63的下一个返回到0。即,在图17以及图18的例子中,也与图13以及图14的例子同样,定义六十四个内部状态。

[0138]

另外,在根据振荡信号d0的逻辑电平的变化而从延迟元件201-5输出的信号d5的逻辑电平发生变化起到从延迟元件201-6输出的信号d6的逻辑电平发生变化为止的期间内,图17以及图18的真值表以振荡信号d0的逻辑电平再次发生变化为条件而成立。

[0139]

图19是示出图17以及图18的真值表成立的情况下的转移状态输出装置1的动作的一例的时序图。在图19的例子中,基准信号clk的周期是振荡信号d0的周期的2.5倍。而且,由于内部状态在振荡信号d0的一个周期的期间内转移十六次,因此内部状态在基准信号clk的一个周期的期间内转移四十次。因此,在使能信号en为高电平的期间内,在基准信号clk的上升沿的定时,状态信号out[6:0]的值逐四十发生变化。

[0140]

不过,由于环状振荡电路10、多级延迟线200具有温度特性,因此根据温度而振荡信号d0的周期、延迟元件201-1~201-q的延迟时间发生变化。因此,在保证时间数字转换器100的动作的温度范围较宽的情况下,不满足根据温度在根据振荡信号d0的逻辑电平的变化而在从信号d5的逻辑电平发生变化起到信号d6的逻辑电平发生变化为止的期间内振荡信号d0的逻辑电平再次发生变化这一条件,图17以及图18的真值表不成立。

[0141]

例如,在为某一温度时,振荡信号d0的周期、延迟元件201-1~201-7的延迟时间变短,在信号d0~d5为低电平且信号d6、d7为高电平的内部状态下,当在信号d0变化为高电平之前信号d6变化为低电平时,转移到信号d0~d6为低电平且信号d7为高电平的内部状态。图17以及图18的真值表不包括该转移后的内部状态。然而,如图17以及图18的例子那样,如果解码信号dec2[6:0]的值为使解码信号dec[2:0]的值八倍并加上通过函数p0、函数p4与函数x4之和得到的解码信号dec0[2:0]的值而得的值,则不会产生问题。例如,在解码信号

dec[2:0]的值为0、信号d0~d5为低电平且信号d6、d7为高电平的内部状态时,当基准信号clk的上升沿到来时,解码信号dec2[6:0]的值变为8。此外,在解码信号dec[2:0]的值为0、信号d0~d6为低电平且信号d7为高电平的下一个内部状态时,当基准信号clk的上升沿到来时,解码信号dec2[6:0]的值变为9。此外,在解码信号dec[2:0]的值为0、信号d0为高电平、信号d1~d6为低电平且信号d7为高电平的下下一个内部状态时,当基准信号clk的上升沿到来时,解码信号dec2[6:0]的值变为10。因此,在转移状态获取部30获取到转移前后的任一方的内部状态的情况下,由于解码信号dec2[6:0]的值之差必定为1,因此运算部50能够正确地进行状态转移数的运算,因此不会产生问题。即使振荡信号d0的周期、延迟元件201-1~201-7的延迟时间进一步变短,也同样地不会产生问题。

[0142]

这样,根据温度变化,在多级延迟线200的最后一级的延迟元件201-q的状态转移之前的任意定时,即使环状振荡电路10转移到下一个状态,也能够不产生问题。进一步,如果环状振荡电路10在延迟元件201-q的状态转移之前转移到下一个状态,则由转移状态获取部30获取的内部状态的频率的偏差也较小。因此,即使产生温度变化,也期望环状振荡电路10必定在多级延迟线200的最后一级的延迟元件201-q的状态转移之前转移为下一个状态。

[0143]

另外,当振荡信号d0的周期、延迟元件201-1~201-7的延迟时间进一步变短时,根据振荡信号d0的逻辑电平的变化,在信号d7的逻辑电平发生变化之后,振荡信号d0的逻辑电平再次发生变化。换言之,多级延迟线200的延迟时间比振荡信号d0的半周期小。在该情况下,代替图17以及图18的真值表,定义有图20以及图21的真值表。在图20以及图21的例子中,每当环状振荡电路10的状态或多级延迟线200的状态发生变化时,内部状态的值从3逐一增加到66,内部状态的值在66的下一个返回到3。即,在图20以及图21的例子中,也与图17以及图18的例子同样,定义六十四个内部状态,且由于当内部状态进行一个转移时,解码信号dec2[6:0]的值增加一个,因此即使假如环状振荡电路10在多级延迟线200的最后一级的延迟元件201-7的状态转移之后转移到下一个状态,也不会产生问题。

[0144]

图22是示出图20以及图21的真值表成立的情况下的转移状态输出装置1的动作的一例的时序图。在图22的例子中,基准信号clk的周期是振荡信号d0的周期的2.5倍。而且,由于内部状态在振荡信号d0的一个周期的期间内转移十六次,因此内部状态在基准信号clk的一个周期的期间内转移四十次。因此,在使能信号en为高电平的期间内,在基准信号clk的上升沿的定时,状态信号out[6:0]的值逐四十发生变化。

[0145]

只是,当根据温度变化而振荡信号d0的周期、延迟元件201-1~201-q的延迟时间变长时,可能会产生问题。在为某一温度时,振荡信号d0的周期、延迟元件201-1~201-7的延迟时间变长,在信号d0~d4为低电平且信号d5~d7为高电平的内部状态下,当在信号d5变化为低电平之前信号d0变化为高电平时,转移到信号d1~d4为低电平且信号d0、d5~d7为高电平的内部状态。例如,在解码信号dec[2:0]的值为0的情况下,在为转移前的内部状态时,当基准信号clk的上升沿到来时,解码信号dec2[6:0]的值变为7,在为转移后的内部状态时,当基准信号clk的上升沿到来时,解码信号dec2[6:0]的值变为8,由于其差为1,因此不会产生问题。然而,在为某一温度时,振荡信号d0的周期、延迟元件201-1~201-7的延迟时间进一步变长,在信号d0~d3为低电平且信号d4~d7为高电平的内部状态下,当在信号d4变化为低电平之前信号d0变化为高电平时,转移到信号d1~d3为低电平且信号d0、d4

~d7为高电平的内部状态。例如,由于在为转移前的内部状态时,在解码信号dec[2:0]的值为0的情况下,当基准信号clk的上升沿到来时,解码信号dec2[6:0]的值变为6,在为转移后的内部状态时,解码信号dec[2:0]的值变为1,因此当基准信号clk的上升沿到来时,解码信号dec2[6:0]的值变为15,由于其差为9,因此会产生问题。

[0146]

通过以上的考察,例如,在保证时间数字转换器100的动作的温度范围内,在多级延迟线200的延迟时间变为最大时,如图17以及图18的真值表成立那样,如果调整多级延迟线200的延迟时间,则不会产生问题。

[0147]

根据在以上所说明的第二实施方式的时间数字转换器100,起到与第一实施方式的时间数字转换器100同样的效果。

[0148]

进一步,根据第二实施方式的时间数字转换器100,在转移状态输出装置1中,由于能够根据多级延迟线200所包括的延迟元件的数量来增加内部状态的数量,因此能够提升运算部50算出的时间数字值td的分辨率。

[0149]

此外,在第二实施方式的时间数字转换器100中,在转移状态输出装置1中,多级延迟线200不包括在环状振荡电路10的振荡环中,且根据环状振荡电路10的状态变化而状态发生变化。因此,如果将多个延迟元件201-1~201-q的延迟时间设为大致恒定,则多级延迟线200的各状态持续的时间大致恒定。因此,根据第二实施方式的时间数字转换器100,在转移状态输出装置1中,能够降低从包括从环状振荡电路10输出的信号、从状态机20输出的信号和从多级延迟线200输出的信号的状态信息得到的各内部状态持续的时间的差异。

[0150]

此外,根据第二实施方式的时间数字转换器100,在转移状态输出装置1中,如果使从多级延迟线200的最后一级的延迟元件201-q的状态转移起到环状振荡电路10转移到下一个状态为止的时间在多级延迟线200所包括的多个延迟元件201-1~201-q的延迟时间的平均值以下,则由于环状振荡电路10的状态即将发生变化之前的内部状态持续的时间不会比其他内部状态的持续时间长,因此能够进一步降低各内部状态持续的时间的差异。

[0151]

此外,根据第二实施方式的时间数字转换器100,在转移状态输出装置1中,如果在多级延迟线200的最后一级的延迟元件201-q的状态转移之前使环状振荡电路10转移到下一个状态,则通过对内部状态算出部40的运算下工夫,从而即使起因于温度变化等而环状振荡电路10的状态变化的周期、多级延迟线200的状态变化的周期发生变化,也能够正确地算出内部状态。

[0152]

1-3.第三实施方式

[0153]

以下,关于第三实施方式的时间数字转换器,对与第一实施方式或第二实施方式同样的结构要素标注相同的附图标记,省略或简略与第一实施方式或第二实施方式重复的说明,主要对与第一实施方式以及第二实施方式不同的内容进行说明。

[0154]

由于第三实施方式的时间数字转换器100的结构例与图1是同样的,因此省略了其图示。即,在第三实施方式的时间数字转换器100中,转移状态输出装置1的结构与第一实施方式是同样的。只是,在第三实施方式的时间数字转换器100中,与第一实施方式的时间数字转换器100不同,在输入触发信号trg之后,环状振荡电路10不停止,而在转移状态输出装置1的内部状态的转移次数超过阈值th的情况下,将该转移次数作为阈值th来算出时间数字值td。

[0155]

图23是示出第三实施方式的时间数字转换器100具备的转移状态输出装置1的结

构例的图。在图23的例子中,转移状态输出装置1具备逻辑与电路11、逻辑反转电路12、格雷码计数器21、d触发器31、寄存器32以及解码器41。

[0156]

逻辑与电路11输出触发信号trg与从逻辑反转电路12输出的信号的逻辑与信号。从逻辑与电路11输出的信号在触发信号trg为低电平时变为低电平,在触发信号trg为高电平时变为与从逻辑反转电路12输出的信号相同的逻辑电平。

[0157]

逻辑反转电路12输出将从逻辑与电路11输出的信号的逻辑电平反转而得的信号。因此,在触发信号trg为高电平时,从逻辑与电路11输出的信号的逻辑电平交替地重复低电平和高电平。即,由逻辑与电路11和逻辑反转电路12构成环状振荡电路10,环状振荡电路10将从逻辑与电路11输出的信号作为振荡信号d0输出。

[0158]

由于格雷码计数器21、d触发器31、寄存器32以及解码器41的功能与第一实施方式是同样的,因此省略其说明。

[0159]

图24是示出转移状态输出装置1的动作的一例的时序图。在图24的例子中,当触发信号trg从低电平变化为高电平时,使能信号en从低电平转移到高电平,环状振荡电路10的振荡开始。这之后,在触发信号trg为高电平的期间内,环状振荡电路10的振荡持续进行,当触发信号trg从高电平变化为低电平时,振荡停止。

[0160]

在解码器41的真值表为图3的情况下,输出case1的状态信号out[3:0],在解码器41的真值表为图4的情况下,输出case2的状态信号out[2:0]。在图24的例子中,基准信号clk的周期是振荡信号d0的周期的2.5倍。而且,在图3的例子中,由于内部状态在振荡信号d0的一个周期的期间内转移四次,因此内部状态在基准信号clk的一个周期的期间内转移十次。因此,在使能信号en为高电平的期间内,在基准信号clk的上升沿的定时,case1的状态信号out[3:0]的值逐十发生变化。此外,在图4的例子中,由于内部状态在振荡信号d0的一个周期的期间内转移两次,因此内部状态在基准信号clk的一个周期的期间内转移五次。因此,在使能信号en为高电平的期间内,在基准信号clk的上升沿的定时,case2的状态信号out[2:0]的值逐五发生变化。

[0161]

图25是示出在第三实施方式的时间数字转换器100中运算部50具备的计数部60的结构例的图。计数部60具有寄存器61、减法器62、累加器63、乘法器64以及虚拟化部65。

[0162]

由于寄存器61、减法器62以及累加器63的功能与第一实施方式是同样的,因此省略其说明。

[0163]

向虚拟化部65输入从减法器62输出的信号c1。正如上述那样,从减法器62输出的信号c1的值相当于在基准信号clk的最近一个周期的时间内转移状态输出装置1的内部状态转移的次数。虚拟化部65通过与基准信号clk同步地累加信号c1的值,从而算出产生触发信号trg的上升沿或下降沿后转移状态输出装置1的内部状态转移的次数。而且,在算出的转移次数不超过阈值th的情况下,虚拟化部65将状态信号out直接虚拟化为信号out’,并输出相当于信号out’的差值的信号c2。在该情况下,信号c1和信号c2的值相等。

[0164]

在算出的转移次数超过阈值th的情况下,虚拟化部65将状态信号out虚拟化为置换为阈值th后的信号out’,并输出相当于信号out’的差值的信号c2。

[0165]

乘法器64将从虚拟化部65输出的信号c2的值与从累加器63输出的权重系数信号wc的值相乘,算出计数值cnt。计数值cnt从计数部60输出。

[0166]

在图25中,省略了图示以及说明,但在转移状态输出装置1的状态转移停止的情况

下等,也可以向寄存器61以及累加器63输入将保持的值初始化为0的复位信号。

[0167]

图26是示出基准信号clk的时间事件与触发信号trg的时间事件的相位差pd与时间数字值td的关系的图。在图26中还示出了状态信号out的值、c1的值、out’的值、c2的值、权重系数信号wc的值、计数值cnt以及计数值dcnt。此外,在图26的例子中,阈值th是64,常数值a是1。此外,t是基准信号clk的一个周期的时间。

[0168]

如图26所示,每当产生基准信号clk的时间事件时,基于状态信号out以及信号c1,生成信号out’以及信号c2。进一步,基于信号c2以及权重系数信号wc生成计数值cnt,将保持有计数值cnt的计数值dcnt累加,而时间数字值td增加。在将基准信号clk的时间事件作为第0个上升沿时,在相位差pd是t

×

1.5的情况下,在第十个上升沿以后,表示产生触发信号trg的时间事件后的转移状态输出装置1的内部状态的转移次数的状态信号out的值超过阈值th即64。因此,在基准信号clk的第十个上升沿以后,信号out’是64,在基准信号clk的第十一个上升沿以后,信号c2是0。而且,在基准信号clk的第十二个上升沿以后,时间数字值td变为377。

[0169]

此外,在相位差pd是t

×

1.7的情况下,在基准信号clk的第十个上升沿以后,由于状态信号out的值超过阈值th即64,因此信号out’是64,在基准信号clk的第十一个上升沿以后,信号c2是0。而且,在基准信号clk的第十二个上升沿以后,时间数字值td变为391。

[0170]

此外,在相位差pd是t

×

2.7的情况下,在基准信号clk的第十一个上升沿以后,由于状态信号out的值超过阈值th即64,因此信号out’是64,在基准信号clk的第十二个上升沿以后,信号c2是0。而且,在基准信号clk的第十三个上升沿以后,时间数字值td变为455。

[0171]

此外,在相位差pd是t

×

3.7的情况下,在基准信号clk的第十二个上升沿以后,由于状态信号out的值超过阈值th即64,因此信号out’是64,在基准信号clk的第十三个上升沿以后,信号c2是0。而且,在基准信号clk的第十四个上升沿以后,时间数字值td变为519。

[0172]

将图26与图9进行比较,在相位差pd是t

×

1.5、t

×

1.7、t

×

2.7、t

×

3.7的任一方的情况下,时间数字值td也均相同。因此,即使在第三实施方式的时间数字转换器100中,如图10所示,时间数字值td的差值δtd也分别是+14、+64、+64,当相位差pd只增加基准信号clk的一个周期的时间t时,时间数字值td只增加阈值th即64。

[0173]

根据在以上所说明的第三实施方式的时间数字转换器100,起到与第一实施方式的时间数字转换器100同样的效果。

[0174]

进一步,根据第三实施方式的时间数字转换器100,由于在转移状态输出装置1的内部状态的转移次数超过阈值th的情况下,运算部50将该转移次数作为阈值th来算出时间数字值td,因此能够使时间数字值td的位数降低。此外,在转移状态输出装置1中,由于不需要用于使环状振荡电路10的振荡停止的电路,因此能够使转移状态输出装置1的尺寸降低。

[0175]

1-4.第四实施方式

[0176]

以下,关于第四实施方式的时间数字转换器,对与第一实施方式~第三实施方式的任一方同样的结构要素标注相同的附图标记,省略或简略与第一实施方式~第三实施方式的任一方重复的说明,主要对与第一实施方式~第三实施方式的任一方都不同的内容进行说明。

[0177]

由于第四实施方式的时间数字转换器100的结构例与图11是同样的,因此省略了其图示。只是,在第四实施方式的时间数字转换器100中,与第二实施方式的时间数字转换

器100不同,在输入触发信号trg之后,环状振荡电路10不停止,在转移状态输出装置1的内部状态的转移次数超过阈值th的情况下,将该转移次数作为阈值th来算出时间数字值td。

[0178]

即,在第四实施方式的时间数字转换器100中,转移状态输出装置1的结构与第二实施方式是同样的,运算部50与第三实施方式是同样的。

[0179]

图27是示出第四实施方式的时间数字转换器100具备的转移状态输出装置1的结构例的图。在图27的例子中,转移状态输出装置1具备逻辑与电路11、逻辑反转电路12、格雷码计数器21、q+1个d触发器31-0~31-q、寄存器32、解码器41、解码器42以及q个延迟元件201-1~201-q。q是2以上的整数。

[0180]

逻辑与电路11输出触发信号trg与从逻辑反转电路12输出的信号的逻辑与信号。从逻辑与电路11输出的信号在触发信号trg为低电平时变为低电平,在触发信号trg为高电平时变为与从逻辑反转电路12输出的信号相同的逻辑电平。

[0181]

逻辑反转电路12输出将从逻辑与电路11输出的信号的逻辑电平反转而得的信号。因此,在触发信号trg为高电平时,从逻辑与电路11输出的信号的逻辑电平交替地重复低电平和高电平。即,由逻辑与电路11和逻辑反转电路12构成环状振荡电路10,环状振荡电路10将从逻辑与电路11输出的信号作为振荡信号d0输出。

[0182]

由于格雷码计数器21的功能与第一实施方式以及第二实施方式是同样的,因此省略其说明。由于d触发器31-0~31-q、寄存器32、解码器41、解码器42以及延迟元件201-1~201-q的功能与第二实施方式是同样的,因此省略其说明。此外,由于运算部50的结构与第三实施方式是同样的,因此省略其说明。

[0183]

图28是示出转移状态输出装置1的动作的一例的时序图。在图28的例子中,当触发信号trg从低电平变化为高电平时,使能信号en从低电平转移到高电平,环状振荡电路10的振荡开始。这之后,在触发信号trg为高电平的期间内,环状振荡电路10的振荡持续进行,当触发信号trg从高电平变化为低电平时,振荡停止。

[0184]

在图28的例子中,基准信号clk的周期是振荡信号d0的周期的2.5倍。而且,由于内部状态在振荡信号d0的一个周期的期间内转移十六次,因此内部状态在基准信号clk的一个周期的期间内转移四十次。因此,在图28的例子中,在使能信号en为高电平的期间内,在基准信号clk的上升沿的定时,状态信号out[5:0]的值逐四十发生变化。

[0185]

根据在以上所说明的第四实施方式的时间数字转换器100,起到与第二实施方式的时间数字转换器100同样的效果。

[0186]

进一步,根据第四实施方式的时间数字转换器100,由于在转移状态输出装置1的内部状态的转移次数超过阈值th的情况下,运算部50将该转移次数作为阈值th来算出时间数字值td,因此能够使时间数字值td的位数降低。此外,在转移状态输出装置1中,由于不需要用于使环状振荡电路10的振荡停止的电路,因此能够使转移状态输出装置1的尺寸降低。

[0187]

1-5.第五实施方式

[0188]

以下,关于第五实施方式的时间数字转换器,对与第一实施方式~第四实施方式的任一方同样的结构要素标注相同的附图标记,省略或简略与第一实施方式~第四实施方式的任一方重复的说明,主要对与第一实施方式~第四实施方式的任一方都不同的内容进行说明。

[0189]

图29是第五实施方式的时间数字转换器100的功能框图。此外,图30是第五实施方

式的时间数字转换器100的另一功能框图。如图29以及图30所示,第五实施方式的时间数字转换器100具备转移状态输出装置1和运算部50。图29中的转移状态输出装置1与第一实施方式或第三实施方式中的转移状态输出装置1是同样的。此外,图30中的转移状态输出装置1与第二实施方式或第四实施方式中的转移状态输出装置1是同样的。

[0190]

向时间数字转换器100输入n个触发信号trg1~trgn和基准信号clk。n是2以上的整数。另外,触发信号trg1~trgn的各时间事件按其顺序以规定的时间以上的间隔到来。

[0191]

转移状态输出装置1基于各个触发信号trg1~trgn开始状态转移,与基准信号clk的时间事件同步地输出状态信号out[n:0]。向运算部50输入各个状态信号out[n:0]。

[0192]

运算部50基于各个状态信号out[n:0]来运算转移状态输出装置1的内部状态的转移次数,基于该转移次数来算出与触发信号trg1~trgn的时间事件对应的n个时间数字值td1~tdn。而且,运算部50分别算出时间数字值td1~tdn中的任两个的差值即m个时间数字值tdy1~tdym。m是1以上的整数。

[0193]

图31是示出运算部50的结构例的图。如图31所示,运算部50具有计数部60、计数值保持部70、累加部80以及时间数字值生成部92。

[0194]

对于1以上、n以下的各整数i,触发信号trgi的时间事件到达,从而计数部60输出与触发信号trgi对应的计数值cnt。在计数部60输出与触发信号trgi对应的计数值cnt后,保持于计数部60的计数值cnt被初始化为0。这之后,伴随着触发信号trg

i+1

的时间事件的到来,计数部60输出与触发信号trg

i+1

对应的计数值cnt。

[0195]

计数值保持部70与基准信号clk同步地逐一读入从计数部60依次输出的计数值cnt,并作为计数值dcnt保持。

[0196]

累加部80通过与基准信号clk同步地对在计数值保持部70中依次保持的各个计数值dcnt逐一累加,从而依次生成与基准信号clk的时间事件和触发信号trg1~trgn的各自的时间事件的相位差对应的n个时间数字值td1~tdn。另外,计数值保持部70以及累加部80例如通过被输入未图示的复位信号等而被初始化。

[0197]

时间数字值生成部92与基准信号clk同步地基于与触发信号trg1~trgn对应的n个时间数字值td1~tdn,生成与触发信号trg1~trgn的至少两个的时间事件的时间间隔对应的时间数字值tdy1~tdym。

[0198]

例如,m=n-1,时间数字值tdyi也可以是与触发信号trg

i+1

对应的时间数字值td

i+1

和与触发信号trgi对应的时间数字值tdi的差值。

[0199]

此外,时间数字值生成部92可以对时间数字值tdy1~tdym进行规定的缩放并输出,也可以按照规定的转换式或者表信息将时间数字值tdy1~tdym进行转换并输出。

[0200]

另外,触发信号trg1~trgn中的任一个触发信号trgj是“第一触发信号”的一例,触发信号trg1~trgn中的其他任一个触发信号trgk是“第二触发信号”的一例。此外,根据触发信号trgj而从转移状态输出装置1输出的状态信号out[n:0]是“第一状态信息”的一例,根据触发信号trgk而从转移状态输出装置1输出的状态信号out[n:0]是“第二状态信息”的一例。此外,根据触发信号trgj而从累加部80输出的时间数字值tdj是“第一时间数字值”的一例,根据触发信号trgk而从累加部80输出的时间数字值tdk是“第二时间数字值”的一例。

[0201]

在本实施方式中,基准信号clk的时间事件与触发信号trg1~trgn的时间事件被独立地设定。即,基准信号clk的时间事件与触发信号trg1~trgn的时间事件是不同步的。而

且,时间数字值tdy1~tdym分别与触发信号trg1~trgn中的任两个的时间事件的相位差对应。例如,时间数字值tdy1~tdym被作为针对触发信号trg1~trgn中的任两个的时间事件的时间间隔的时间戳而使用。

[0202]

根据在以上所说明的第五实施方式的时间数字转换器100,起到与第一实施方式~第四实施方式的时间数字转换器100同样的效果。

[0203]

进一步,根据第五实施方式的时间数字转换器100,能够算出与触发信号trg1~trgn的至少两个的时间间隔对应的时间数字值tdy1~tdym。此外,由于对触发信号trg1~trgn共用计数部60、计数值保持部70以及累加部80来生成时间数字值tdy1~tdym,因此能够实现运算部50的小型化。

[0204]

2.a/d转换电路

[0205]

2-1.第一实施方式

[0206]

图32是示出第一实施方式的a/d转换电路300的结构的图。如图32所示,第一实施方式的a/d转换电路300包括基准波形信号生成电路102、比较器103以及时间数字转换器100。而且,a/d转换电路300将所输入的模拟信号ain转换为数字信号dout并输出。

[0207]

基准波形信号生成电路102基于基准信号clk生成基准波形信号ref。基准波形信号ref是电压以与基准信号clk相同的周期发生变化的信号,例如,也可以是三角波信号、斜坡波信号、正弦波信号、余弦波信号等。此外,基准波形信号生成电路102也可以基于对基准信号clk进行分频而得的信号来生成基准波形信号ref。在该情况下,基准波形信号ref也可以是电压以对基准信号clk进行分频而得的周期发生变化的信号。通过基于对基准信号clk进行分频而得的信号来生成基准波形信号ref,并抑制生成定时的波动,从而时间数字转换器100中的计时精度提升,其结果,a/d转换的精度以及分辨率提高。

[0208]

比较器103对模拟信号ain的电压和基准波形信号生成电路102生成的基准波形信号ref的电压进行比较,并输出触发信号trg。

[0209]

正如上述那样,时间数字转换器100算出基准信号clk的时间事件与触发信号trg的时间事件的相位差,即、与基准信号clk的时间事件和触发信号trg的时间事件的时间间隔对应的时间数字值td。

[0210]

而且,a/d转换电路300输出基于时间数字值td的数字信号dout。例如,a/d转换电路300可以将时间数字值td作为数字信号dout输出,也可以将时间数字值td转换为具有相对于模拟信号ain的电压发生线性变化的值的数字信号dout并输出。

[0211]

图33是示出第一实施方式的a/d转换电路300中的各种信号的波形的一例的图。在图33的例子中,基准波形信号ref是在基准信号clk的上升沿变为最小电压、在基准信号clk的下降沿变为最大电压的三角波信号。此外,如果模拟信号ain的电压比基准波形信号ref的电压高,则触发信号trg变为高电平,如果模拟信号ain的电压比基准波形信号ref的电压低,则变为低电平。

[0212]

在图33的例子中,模拟信号ain的电压的值是va、vb、vc时的、基准信号clk的上升沿与触发信号trg的上升沿的时间间隔分别变为ta、tb、tc。而且,对于va《vb《vc,ta《tb《tc,基准信号clk的上升沿与触发信号trg的上升沿的时间间隔相对于模拟信号ain的电压发生线性变化。因此,a/d转换电路300能够输出作为具有与ta、tb、tc对应的时间数字值td的数字信号dout。

[0213]

根据第一实施方式的a/d转换电路300,通过使用时间数字转换器100,能够实现高精度、高分辨率、高速处理、低功耗、小型化等。

[0214]

2-2.第二实施方式

[0215]

图34是示出第二实施方式的a/d转换电路300的结构的图。如图34所示,第二实施方式的a/d转换电路300包括采样保持电路101、基准波形信号生成电路102、比较器103以及时间数字转换器100,将所输入的模拟信号ain转换为数字信号dout并输出。

[0216]

采样保持电路101与基准信号clk同步地对模拟信号ain的电压进行采样并保持。

[0217]

基准波形信号生成电路102基于基准信号clk生成基准波形信号ref。基准波形信号ref是电压以与基准信号clk相同的周期发生变化的信号,例如,也可以是三角波信号、斜坡波信号、正弦波信号、余弦波信号等。此外,基准波形信号生成电路102也可以基于对基准信号clk进行分频而得的信号来生成基准波形信号ref。在该情况下,基准波形信号ref也可以是电压以对基准信号clk进行分频而得的周期发生变化的信号。通过基于对基准信号clk进行分频而得的信号来生成基准波形信号ref,并抑制生成定时的波动,从而时间数字转换器100中的计时精度提升,其结果,a/d转换的精度以及分辨率提高。

[0218]

比较器103对采样保持电路101保持的电压vh和基准波形信号生成电路102生成的基准波形信号ref的电压进行比较,并输出触发信号trg。

[0219]

正如上述那样,时间数字转换器100算出基准信号clk的时间事件与触发信号trg的时间事件的相位差,即、与基准信号clk的时间事件和触发信号trg的时间事件的时间间隔对应的时间数字值td。

[0220]

而且,a/d转换电路300输出基于时间数字值td的数字信号dout。例如,a/d转换电路300可以将时间数字值td作为数字信号dout输出,也可以将时间数字值td转换为具有相对于模拟信号ain的电压发生线性变化的值的数字信号dout并输出。

[0221]

图35是示出第二实施方式的a/d转换电路300中的各种信号的波形的一例的图。在图35的例子中,在基准信号clk的每个上升沿对模拟信号ain的电压进行采样并保持。此外,基准波形信号ref是在基准信号clk的上升沿变为最小电压、在基准信号clk的下降沿变为最大电压的三角波信号。此外,如果电压vh比基准波形信号ref的电压高,则触发信号trg变为高电平,如果电压vh比基准波形信号ref的电压低,则变为低电平。

[0222]

在图35的例子中,在保持有模拟信号ain的电压的电压vh的值是va、vb、vc时,基准信号clk的上升沿与触发信号trg的上升沿的时间间隔分别变为ta、tb、tc。而且,对于va《vb《vc,ta《tb《tc,基准信号clk的上升沿与触发信号trg的上升沿的时间间隔相对于模拟信号ain的电压发生线性变化。因此,a/d转换电路300能够输出作为具有与ta、tb、tc对应的时间数字值td的数字信号dout。

[0223]

根据第二实施方式的a/d转换电路300,通过使用时间数字转换器100,从而能够实现高精度、高分辨率、高速处理、低功耗、小型化等。此外,根据第二实施方式的a/d转换电路300,由于通过采样保持电路101将采样定时保持为恒定,因此能够减轻a/d转换定时的波动。

[0224]

本发明并不限定于本实施方式,在本发明的要旨的范围内能够进行各种变形实施。

[0225]

上述的实施方式以及变形例是一例,并非限定于此。例如,也可以对各实施方式以

及各变形例进行适当组合。

[0226]

本发明包括与在实施方式中所说明的结构实质上相同的结构,例如,功能、方法以及结果相同的结构、或者目的以及效果相同的结构。此外,本发明包括对在实施方式中所说明的结构的非本质部分进行了置换的结构。此外,本发明包括能够起到与在实施方式中所说明的结构相同的作用效果的结构或达到相同目的的结构。此外,本发明包括在实施方式中所说明的结构中附加了公知技术的结构。

[0227]

从上述的实施方式以及变形例导出以下的内容。

[0228]

转移状态输出装置的一方式,具备:环状振荡电路,基于触发信号开始振荡;状态机,根据所述环状振荡电路的状态变化而状态发生变化;转移状态获取部,与基准信号同步地获取并保持包括从所述环状振荡电路输出的信号和从所述状态机输出的信号的状态信息;以及内部状态算出部,基于所述转移状态获取部保持的所述状态信息而算出与所述环状振荡电路的状态变化的次数相对应的内部状态,从所述内部状态从第一内部状态转移到第二内部状态起到再次转移到所述第一内部状态为止的时间比更新所述转移状态获取部保持的所述状态信息的时间的间隔长。

[0229]

在该转移状态输出装置中,由于环状振荡电路是极其简单的结构,因此状态变化的周期大致恒定。此外,状态机不包括在环状振荡电路的振荡环中,且根据环状振荡电路的状态变化而状态发生变化,因此状态机的状态变化的周期也大致恒定。因此,环状振荡电路、状态机的各状态持续的时间大致恒定。因此,根据该转移状态输出装置,能够降低从包括从环状振荡电路输出的信号和从状态机输出的信号的状态信息得到的各内部状态持续的时间的差异。

[0230]

此外,根据该转移状态输出装置,由于从内部状态从第一内部状态转移到第二内部状态起到再次转移到第一内部状态为止的时间比更新转移状态获取部保持的状态信息的时间的间隔长,因此转移状态获取部能够在状态转移循环一遍之前获取状态信息。

[0231]

在所述转移状态输出装置的一方式中,也可以与所述环状振荡电路的状态发生变化的定时同步地,所述内部状态发生变化。

[0232]

根据该转移状态输出装置,由于环状振荡电路的状态发生变化的定时与内部状态发生变化的定时一对一地对应,环状振荡电路的状态变化的周期大致恒定,因此各内部状态持续的时间大致恒定。因此,根据该转移状态输出装置,能够进一步降低各内部状态持续的时间的差异。

[0233]

所述转移状态输出装置的一方式,也可以所述转移状态输出装置具备多级延迟线,所述多级延迟线连接有多个延迟元件,向所述多级延迟线输入从所述环状振荡电路输出的信号,所述状态信息包括从所述多级延迟线输出的信号。

[0234]

根据该转移状态输出装置,能够根据多级延迟线所包括的延迟元件的数量来增加内部状态的数量。

[0235]

此外,在该转移状态输出装置中,多级延迟线不包括在环状振荡电路的振荡环中,且根据环状振荡电路的状态变化而状态发生变化。因此,如果将多个延迟元件的延迟时间设为大致恒定,则多级延迟线的各状态持续的时间大致恒定。因此,根据该转移状态输出装置,能够降低从包括从环状振荡电路输出的信号、从状态机输出的信号和从多级延迟线输出的信号的状态信息得到的各内部状态持续的时间的差异。

[0236]

在所述转移状态输出装置的一方式中,从所述多级延迟线的最后一级的所述延迟元件的状态转移起到所述环状振荡电路转移到下一个状态为止的时间也可以在所述多级延迟线所包括的所述多个延迟元件的延迟时间的平均值以下。

[0237]

根据该转移状态输出装置,由于环状振荡电路的状态即将发生变化之前的内部状态持续的时间不会比其他内部状态的持续时间长,因此能够进一步降低各内部状态持续的时间的差异。

[0238]

在所述转移状态输出装置的一方式中,也可以在所述多级延迟线的最后一级的所述延迟元件的状态转移之前,所述环状振荡电路转移到下一个状态。

[0239]

根据该转移状态输出装置,通过对内部状态算出部的运算下工夫,从而即使起因于温度变化等而环状振荡电路的状态变化的周期、多级延迟线的状态变化的周期发生变化,也能够正确地算出内部状态。

[0240]

时间数字转换器的一方式,具备:所述转移状态输出装置的一方式;以及运算部,对所述内部状态的转移次数进行运算,并基于所述转移次数算出与所述触发信号的时间事件对应的时间数字值。

[0241]

根据该时间数字转换器,由于具备能够降低各内部状态持续的时间的差异的转移状态输出装置,因此运算部不进行校正内部状态的转移次数的运算,而能够算出较高的精度的时间数字值。此外,由于运算部不需要进行校正运算,因此从输入触发信号起到算出时间数字值为止的时间变短,并且不需要花费作成校正运算所需要的校正信息的精力。

[0242]

此外,在该时间数字转换器中,在转移状态输出装置中,由于转移状态获取部能够在状态转移循环一遍之前获取状态信息,因此运算部不需要确定内部状态在从转移状态获取部获取状态信息起到获取下一个状态信息为止的期间内循环一遍的次数。因此,根据该时间数字转换器,能够简化运算部的处理。

[0243]

在时间数字转换器的一方式中,在所述内部状态的所述转移次数超过阈值的情况下,所述运算部也可以将该转移次数作为阈值来算出所述时间数字值。

[0244]

根据该时间数字转换器,由于在内部状态的转移次数超过阈值的情况下将该转移次数作为阈值来算出时间数字值,因此能够使时间数字值的位数降低。此外,由于不需要用于使环状振荡电路的振荡停止的电路,因此能够使转移状态输出装置的尺寸降低。

[0245]

在时间数字转换器的一方式中,也可以将所述触发信号作为第一触发信号,将所述状态信息作为第一状态信息,将所述时间数字值作为第一时间数字值,所述环状振荡电路基于第二触发信号开始振荡,在向所述环状振荡电路输入所述第二触发信号之后,所述转移状态获取部与所述基准信号同步地获取并保持包括从所述环状振荡电路输出的信号和从所述状态机输出的信号的第二状态信息,所述内部状态算出部基于所述转移状态获取部保持的所述第二状态信息来算出与所述环状振荡电路的状态变化的次数相对应的所述内部状态,所述运算部对所述内部状态的转移次数进行运算,并基于所述转移次数来算出与所述第二触发信号的时间事件对应的第二时间数字值,所述运算部算出所述第一时间数字值与所述第二时间数字值的差值。

[0246]

根据该时间数字转换器,能够算出与第一触发信号与第二触发信号的时间间隔对应的时间数字值。

[0247]

a/d转换电路的一方式,将所输入的模拟信号转换为数字信号并输出,所述a/d转

换电路具备:所述时间数字转换器的一方式;基准波形信号生成电路,基于所述基准信号生成基准波形信号;以及比较器,对所述模拟信号的电压和所述基准波形信号的电压进行比较并输出所述触发信号,所述a/d转换电路输出所述数字信号,所述数字信号基于所述时间数字转换器算出的所述时间数字值。

[0248]

根据该a/d转换电路,通过使用时间数字转换器,从而能够实现高精度、高分辨率、高速处理、低功耗、小型化等。

[0249]

a/d转换电路的一方式,将所输入的模拟信号转换为数字信号并输出,所述a/d转换电路具备:所述时间数字转换器的一方式;采样保持电路,对所述模拟信号的电压进行采样并保持;基准波形信号生成电路,基于所述基准信号生成基准波形信号;以及比较器,对所述采样保持电路保持的电压和所述基准波形信号的电压进行比较并输出所述触发信号,所述a/d转换电路输出所述数字信号,所述数字信号基于所述时间数字转换器算出的所述时间数字值。

[0250]

根据该a/d转换电路,通过使用时间数字转换器,从而能够实现高精度、高分辨率、高速处理、低功耗、小型化等。此外,由于通过采样保持电路将采样定时保持为恒定,因此能够减轻a/d转换定时的波动。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1