施密特触发器的制作方法

本发明涉及集成电路,特别涉及一种施密特触发器。

背景技术:

1、在电子学中,施密特触发器(英语:schmitt trigger)是包含正反馈的比较器电路。施密特触发器有两个稳定状态,与一般触发器不同的是,施密特触发器采用电位触发方式,其状态由输入信号电位维持;对于负向递减和正向递增两种不同变化方向的输入信号,施密特触发器有不同的阈值电压。

2、对于标准施密特触发器,如图1所示,当输入电压高于正向阈值电压,输出为高;当输入电压低于负向阈值电压,输出为低;当输入在正负向阈值电压之间,输出不改变,也就是说输出由高电准位翻转为低电准位,或是由低电准位翻转为高电准位时所对应的阈值电压是不同的。只有当输入电压发生足够的变化时,输出才会变化,因此将这种元件命名为触发器。这种双阈值动作被称为迟滞现象,表明施密特触发器有记忆性。从本质上来说,施密特触发器是一种双稳态多谐振荡器。但施密特触发器有闩锁效应(latch-up),其中闩锁效应是指cmos晶片中,在电源vdd与地线gnd(vss)之间由于寄生的pnp和npn双极性bjt相互影响而产生低阻抗通路,该低阻抗通路的存在会使vdd与gnd之间产生大电流,这种大电量会严重影响施密特触发器的可靠性。

技术实现思路

1、本发明的目的在于提供一种施密特触发器,以解决闩锁效应(latch-up)严重影响施密特触发器可靠性的问题。

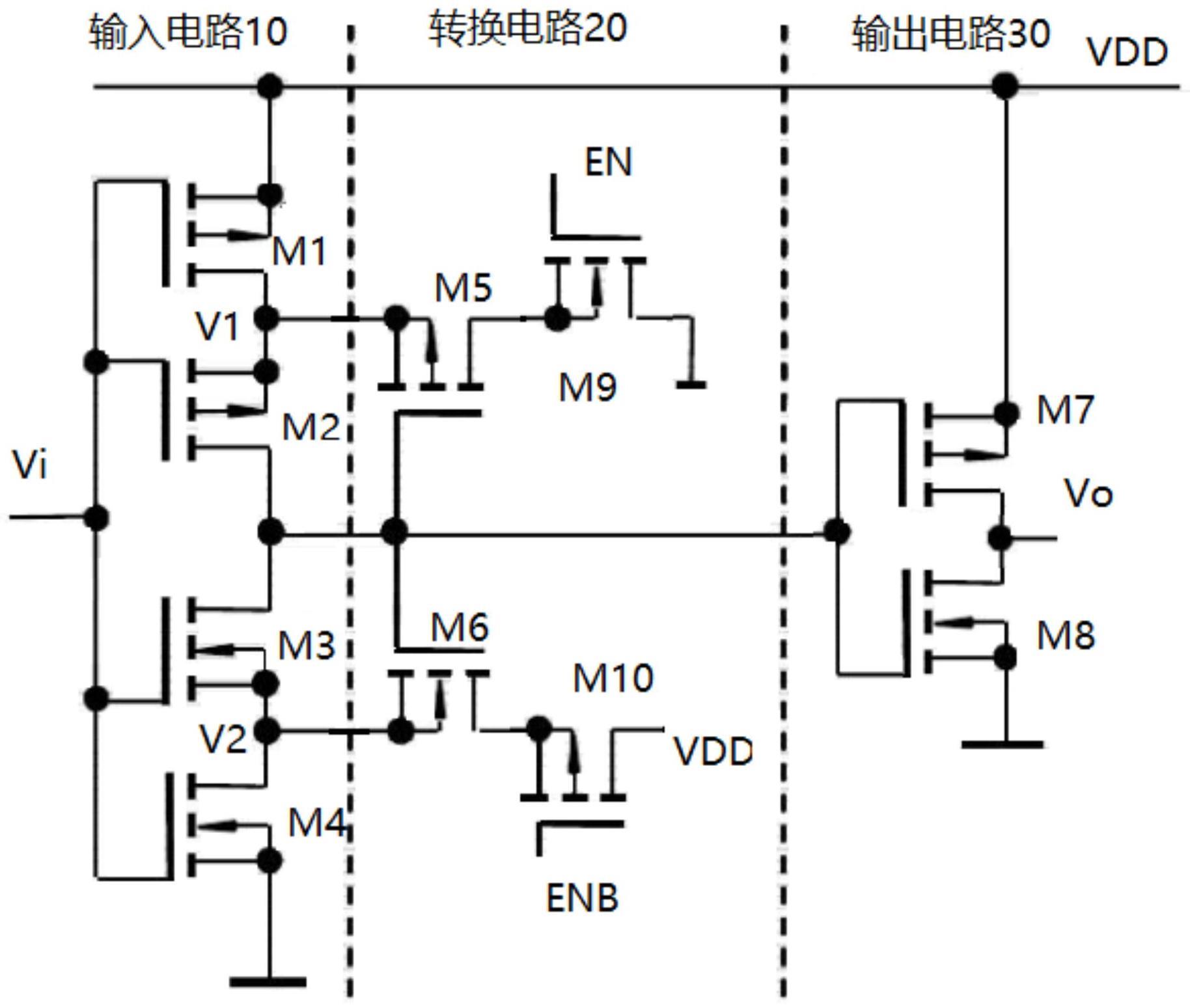

2、为解决上述技术问题,本发明提供一种施密特触发器,包括:

3、输入电路,被配置为根据输入电压生成转换电位,并将转换电位提供至转换电路;

4、转换电路,被配置为根据转换电位生成用于输出电路的输出电压,所述转换电路包括:

5、第一转换晶体管和第二转换晶体管,被配置为根据转换电位向输出电路提供输出电压;

6、第一防闩锁晶体管,连接在第一转换晶体管和地之间;以及

7、第二防闩锁晶体管,连接在第二转换晶体管和电源电压之间;以及

8、输出电路,被配置为根据输出电压输出最终输出电位值。

9、可选的,在所述的施密特触发器中,所述输入电路包括:

10、第一晶体管,被配置为栅极连接输入电压,源极连接电源电压,漏极连接第一转换电位;

11、第二晶体管,被配置为栅极连接输入电压,源极连接第一转换电位,漏极连接输出电路;

12、第三晶体管,被配置为栅极连接输入电压,源极连接第二转换电位,漏极连接输出电路;以及

13、第四晶体管,被配置为栅极连接输入电压,源极接地,漏极连接第二转换电位。

14、可选的,在所述的施密特触发器中,所述转换电路包括:

15、第一转换晶体管,还被配置为栅极连接输出电路,源极连接第一转换电位,漏极连接第一防闩锁晶体管的源极;

16、第一防闩锁晶体管,还被配置为栅极连接第一控制端,漏极接地;

17、第二转换晶体管,还被配置为栅极连接输出电路,源极连接第二转换电位,漏极连接第二防闩锁晶体管的源极;

18、第二防闩锁晶体管,还被配置为栅极连接第二控制端,漏极连接电源电压;

19、输入电压高于正向阈值电压时,第一转换晶体管和第二转换晶体管向输出电路提供的输出电压为高电平;

20、输入电压高于负向阈值电压时,第一转换晶体管和第二转换晶体管向输出电路提供的输出电压为低电平。

21、可选的,在所述的施密特触发器中,所述输出电路包括:

22、第七晶体管,被配置为栅极连接第二晶体管和第三晶体管的漏极、以及第一转换晶体管和第二转换晶体管的栅极,源极连接电源电压,漏极连接最终输出电位值;

23、第八晶体管,被配置为栅极连接第二晶体管和第三晶体管的漏极、以及第一转换晶体管和第二转换晶体管的栅极,源极接地,漏极连接最终输出电位值。

24、可选的,在所述的施密特触发器中,

25、第一晶体管、第二晶体管、第一转换晶体管、第二防闩锁晶体管、第七晶体管为pmos;

26、第三晶体管、第四晶体管、第二转换晶体管、第一防闩锁晶体管、第八晶体管为nmos。

27、可选的,在所述的施密特触发器中,

28、一个第一转换晶体管、一个第一防闩锁晶体管、一个第二转换晶体管、一个第二防闩锁晶体管组成一组调修电路;

29、第一转换晶体管、第一防闩锁晶体管、第二转换晶体管、第二防闩锁晶体管的数量为多个且相等,以使所述转换电路包括多组调修电路;

30、每组调修电路均连接一个第一控制端和一个第二控制端,分别向第一控制端和一个第二控制端提供第一控制信号和第二控制信号,以使得每组调修电路开启或关闭。

31、可选的,在所述的施密特触发器中,一组调修电路关闭时,正向阈值电压的值为第一阈值,负向阈值电压的值为第二阈值;

32、使得当该组调修电路开启时,正向阈值电压的值等于第一阈值与该组调修电路的调修值之和,负向阈值电压的值等于第二阈值与该组调修电路的调修值之差;

33、可选的,在所述的施密特触发器中,调节每组调修电路中的第一转换晶体管的w值和第二转换晶体管的w值,以调节其所对应的一组调修电路的调修值。

34、可选的,在所述的施密特触发器中,直接向第一控制端和一个第二控制端提供高电平信号和低电平信号,以使得至少一组调修电路保持开启。

35、可选的,在所述的施密特触发器中,所述第一转换晶体管和第二转换晶体管作为开关mos:vgs-vth>0、vds<<vgs-vth;

36、第一防闩锁晶体管和第二防闩锁晶体管工作在线性区以替代电阻。

37、在施密特触发器电路中,若nmos直接接电源或者pmos直接接地容易产生latch-up。为了解决latch-up问题,一般会在接电源地上加限流电阻,或者版图实现的时候增加面积以打断latch-up结构。现有技术中常见的防闩锁效应方案采用电阻保护如图2所示,在第一转换晶体管m5和地之间连接第一电阻r1,在第二转换晶体管m6和电源电压之间连接第二电阻r2,以防止闩锁效应。但本发明的发明人发现,增加电阻方式带来如下缺点:mos管和电阻属性不同,不同工艺会有不同的尺寸要求,和别的模块直接拼接也需要尺寸冗余,而用gudring打断结构则会造成占用面积大的缺点,如果没有埋层结构则需要将两个nmos直接的距离设置较大,因此采用该方法弊端较大。

38、基于以上洞察,本发明提供了一种施密特触发器,通过第一防闩锁晶体管连接在第一转换晶体管和地之间,可以实现以第一防闩锁晶体管的线性区电阻特性作为第一转换晶体管防闩锁的手段,同理第二防闩锁晶体管连接在第二转换晶体管和电源电压之间,利用第二防闩锁晶体管的线性区电阻特性作为第二转换晶体管防闩锁的手段,相比于现有技术,本发明中改进的电路具有多个相结合技术效果,由于都是晶体管,属性相同,尺寸要求工艺要求相同,可以相同的工艺步骤统一制作完成,由于都是晶体管,拼接尺寸也相差无几,不会占用额外的面积,拼接灵活,不存在nmos接电源和pmos接地的寄生风险,综上所述,多个技术效果相结合从而实现意想不到的技术优势。

- 还没有人留言评论。精彩留言会获得点赞!