基于忆阻器的平衡三值单变量逻辑电路

1.本发明属于电路设计技术领域,涉及三值数字逻辑电路结构,具体涉及18种物理可实现的基于忆阻器的平衡三值单变量逻辑电路的设计与实现。

背景技术:

2.1971年,蔡少棠教授从电路理论完备性角度,预测了除电阻、电容和电感之外,还存在第四种遗失的无源基本电路元件,表征电荷和磁通量之间的关系,并将其命名为忆阻器。忆阻器被视为下一代非易失性存储器技术,具有高速、低功耗、易集成,以及与cmos工艺兼容等优势。直到2008年,惠普实验室将忆阻器这一理论概念与tio2器件中电阻双极性转变现象联系起来,提出忆阻器的惠普模型。此外忆阻器和cmos具有良好的兼容性,结合二者优势的cmos忆阻混合设计,在非易失性存储、数字逻辑运算和神经网络等方面具有非常广阔的应用前景。

3.随着电子技术的不断发展,人们对多值逻辑,特别是三值逻辑的研究已经做了大量的工作,与传统的二值信号相比,三值信号、四值信号或更多值的信号可以提高传输线与集成电路的信息密度与处理信息的能力。在三值逻辑电路设计中,现有的采用cmos、cntfet等设计的电路结构较为复杂且难以集成,未能体现三值逻辑电路的显著优势。如今伴随着忆阻器的研究发现,在三值逻辑中,使用忆阻器来代替传统的cmos集成电路能够更好的降低电路的复杂成度且精度较高。忆阻器凭借其纳米尺寸、功耗低且与cmos技术相兼容等特点,为三值逻辑电路的发展提供了新的方向。

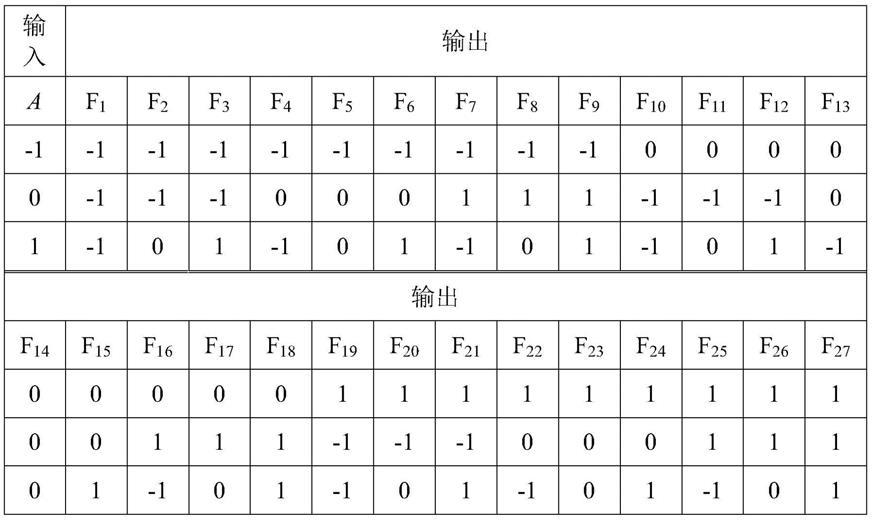

4.在三值逻辑电路的设计当中,单变量逻辑函数得到了广泛的应用。在平衡三值中,单变量函数f(a)中有三种取值-1、0和1,即a∈{-1,0,1}。当输入依次为-1、0、1时,将单变量逻辑函数在a=-1、a=0、a=1下的输出值g-1

、g0、g1按三值三位数g-1

g0g1的顺序进行排序,那么平衡三值单变量逻辑函数的输出可记为f1={-1,-1,-1}、f2={-1,-1,0}、f3={-1,-1,1}、f4={-1,0,-1}、

…

、f

26

={1,1,0}、f

27

={1,1,1},共27种。借助忆阻器的阻值切换特性与mos管的开关特性,对上述单变量函数进行了电路实现,可为多值逻辑电路的研究提供一定的参考作用。

技术实现要素:

5.针对现有技术的不足,本发明提出了多种新的基于忆阻器的平衡三值单变量逻辑电路的设计,均能通过忆阻器和cmos混合设计实现。本发明解决技术问题所采取的技术方案如下:

6.本发明共包含18种单变量逻辑电路的技术解决方案。其中,f4、f9输出电路均只由一个忆阻器和一个nmos管所构成;f5、f

10

、f

13

、f

18

、f

23

、f

26

输出电路均由两个忆阻器和一个nmos管所构成;f3、f7输出电路均由两个忆阻器和两个nmos管所构成;f2、f

15

输出电路均由三个忆阻器和两个nmos管所构成;f

17

、f

21

、f

24

电路均由三个忆阻器和三个nmos管所构成;f

11

、f

12

输出电路均由四个忆阻器和四个nmos管所构成;f8输出电路由五个忆阻器和五个nmos管

所构成。

7.所述f4逻辑电路由第一忆阻器m1和第一nmos管t1构成。所述第一忆阻器m1的负极与第一nmos管t1的栅极相连,并且作为f4逻辑电路的输入端;第一忆阻器m1的正极与第一nmos管t1的漏极相连,并作为f4逻辑电路的输出端f4;第一nmos管t1的源极与电源-v

dd

相连。

8.所述f5逻辑电路由第二忆阻器m2、第三忆阻器m3和第二nmos管t2构成。所述第二忆阻器m2的负极与第二nmos管t2的栅极相连,并作为f5逻辑电路的输入端;第二忆阻器m2的正极与第三忆阻器m3的负极相连,并作为f5逻辑电路的输出端f5;第三忆阻器m3的正极与第二nmos管t2的漏极相连;第二nmos管t2的源极与电源-v

dd

相连。

9.所述f9逻辑电路由第四忆阻器m4和第三nmos管t3构成。所述第四忆阻器m4的负极和第三nmos管t3的栅极与电源v

dd

相连;第四忆阻器m4的正极与第三nmos管t3的漏极相连,并作为f9逻辑电路的输出端f9;第三nmos管t3的源极作为f9逻辑电路的输入端。

10.所述f

10

逻辑电路和f

13

逻辑电路电路结构一致,可由第五忆阻器m5、第六忆阻器m6和第四nmos管t4构成。第五忆阻器m5的负极与电源v

dd

相连;第五忆阻器m5的正极、第六忆阻器m6的负极与第四nmos管t4的漏极相连,并作为f

10

逻辑电路的输出端f

10

或f

13

逻辑电路的输出端f

13

;第四nmos管t4的栅极作为f

10

逻辑电路或f

13

逻辑电路的输入端;第六忆阻器m6的正极和第四nmos管t4的源极与电源-v

dd

相连。

11.所述f

18

逻辑电路由第七忆阻器m7、第八忆阻器m8和第五nmos管t5构成。第七忆阻器m7的负极和第五nmos管t5的栅极与电源v

dd

相连;第七忆阻器m7的正极与第八忆阻器m8的负极相连,并作为f

18

逻辑电路的输出端f

18

;第八忆阻器m8的正极与第五nmos管t5的漏极相连;第五nmos管t5的源极作为f

18

逻辑电路的输入端。

12.所述f

23

逻辑电路和f

26

逻辑电路电路结构一致,可由第九忆阻器m9、第十忆阻器m

10

和第六nmos管t6构成。第九忆阻器m9的负极与电源v

dd

相连;第九忆阻器m9的正极与第十忆阻器m

10

的负极相连,并作为f

23

逻辑电路的输出端f

23

或f

26

逻辑电路的输出端f

26

;第十忆阻器m

10

的正极与第六nmos管t6的漏极相连;第六nmos管t6的栅极作为f

23

逻辑电路或f

26

逻辑电路的输入端;第六nmos管t6的源极与电源-v

dd

相连。

13.所述f2逻辑电路由f

26

逻辑电路和f4逻辑电路级联构成;f

26

逻辑电路的输入端作为f2逻辑电路的输入端;f

26

逻辑电路的输出端f

26

与f4逻辑电路的输入端相连;f4逻辑电路的输出端作为f2逻辑电路的输出端f2。

14.所述f3逻辑电路由f

25

逻辑电路和f

19

逻辑电路级联构成;f

25

逻辑电路的输入端作为f3逻辑电路的输入端;f

25

逻辑电路的输出端f

25

与f

19

逻辑电路的输入端相连;f

19

逻辑电路的输出端作为f3逻辑电路的输出端f3。

15.所述f7逻辑电路由f4逻辑电路和f9逻辑电路级联构成;f4逻辑电路的输入端作为f7逻辑电路的输入端;f4逻辑电路的输出端f4与f9逻辑电路的输入端相连;f9逻辑电路的输出端作为f7逻辑电路的输出端f7。

16.所述f8逻辑电路由f

20

逻辑电路和f

22

逻辑电路级联构成;f

20

逻辑电路的输入端作为f8逻辑电路的输入端;f

20

逻辑电路的输出端f

20

与f

22

逻辑电路的输入端相连;f

22

逻辑电路的输出端作为f8逻辑电路的输出端f8。

17.所述f

11

逻辑电路由f7逻辑电路和f

16

逻辑电路级联构成;f7逻辑电路的输入端作为f

11

逻辑电路的输入端;f7逻辑电路的输出端f7与f

16

逻辑电路的输入端相连;f

16

逻辑电路的

111046617 a可查。

[0031][0032]

下面结合附图对本发明优选实施例作详细说明。

[0033]

基于忆阻器的平衡三值单变量逻辑电路中的逻辑状态为电压值,定义电压v

dd

为1v,对应逻辑“1”;gnd为0v,对应逻辑“0”;-v

dd

为-1v,对应逻辑

“‑

1”。

[0034]

如图1所示,f4逻辑电路由第一忆阻器m1和第一nmos管t1构成。所述第一忆阻器m1的负极与第一nmos管t1的栅极相连,并且作为f4逻辑电路的输入端;第一忆阻器m1的正极与第一nmos管t1的漏极相连,并作为f4逻辑电路的输出端f4;第一nmos管t1的源极与电源-v

dd

相连。

[0035]

对于f4逻辑电路,第一nmos管t1的阈值为1.5v。当输入端a接-v

dd

或接地时,即输入为逻辑

“‑

1”或逻辑“0”,第一nmos管t1截止,输出端f4通过第一忆阻器m1直接与输入端a相连,即输出分别对应于逻辑

“‑

1”、逻辑“0”;当输入端a接v

dd

时,即输入为逻辑“1”,第一nmos管t1导通,输出端f4通过第一nmos管t1连接至-v

dd

,输出为逻辑

“‑

1”。

[0036]

如图2所示,f5逻辑电路由第二忆阻器m2、第三忆阻器m3和第二nmos管t2构成。所述第二忆阻器m2的负极与第二nmos管t2的栅极相连,并作为f5逻辑电路的输入端;第二忆阻器m2的正极与第三忆阻器m3的负极相连,并作为f5逻辑电路的输出端f5;第三忆阻器m3的正极与第二nmos管t2的漏极相连;第二nmos管t2的源极与电源-v

dd

相连。

[0037]

对于f5逻辑电路,第二nmos管t2的阈值为1.5v。当输入端a接-v

dd

或接地时,即输入为逻辑

“‑

1”或逻辑“0”,第二nmos管t2截止,输出端f5通过第二忆阻器m2直接与输入端a相连,即输出分别对应于逻辑

“‑

1”、逻辑“0”;当输入端a接v

dd

时,即输入为逻辑“1”,第二nmos管t2导通,电流将通过第二忆阻器m2和第三忆阻器m3从输入端a流至-v

dd

,根据忆阻器阻值变化规律,此时第二忆阻器m2和第三忆阻器m3均切换为r

off

状态,输出端f5经第二忆阻器m2和第三忆阻器m3分压后为0v,输出为逻辑“0”。

[0038]

如图3所示,f9逻辑电路由第四忆阻器m4和第三nmos管t3构成。所述第四忆阻器m4的负极和第三nmos管t3的栅极与电源v

dd

相连;第四忆阻器m4的正极与第三nmos管t3的漏极相连,并作为f9逻辑电路的输出端f9;第三nmos管t3的源极作为f9逻辑电路的输入端。

和第十忆阻器m

10

从电源v

dd

流至电源-v

dd

,根据忆阻器阻值变化规律,此时第九忆阻器m9和第十忆阻器m

10

均切换为r

off

状态,输出端f

23

经第九忆阻器m9和第十忆阻器m

10

分压后为0v,输出为逻辑“0”。

[0047]

对于f

26

逻辑电路,其与f

23

逻辑电路结构相同,而第六nmos管t6的阈值为1.5v。当输入端a接-v

dd

或接地时,即输入为逻辑

“‑

1”或逻辑“0”,第六nmos管t6截止,输出端f

26

通过第九忆阻器m9与v

dd

相连,输出为逻辑“1”;当输入端a接v

dd

时,即输入为逻辑“1”,第六nmos管t6导通,电流将通过第九忆阻器m9和第十忆阻器m

10

从电源v

dd

流至电源-v

dd

,根据忆阻器阻值变化规律,此时第九忆阻器m9和第十忆阻器m

10

均切换为r

off

状态,输出端f

26

经第九忆阻器m9和第十忆阻器m

10

分压后为0v,输出为逻辑“0”。

[0048]

对于f2逻辑电路,其由f

26

逻辑电路和f4逻辑电路级联构成。f

26

逻辑电路的输入端作为f2逻辑电路的输入端;f

26

逻辑电路的输出端f

26

与f4逻辑电路的输入端相连;f4逻辑电路的输出端作为f2逻辑电路的输出端f2。

[0049]

当输入端a接-v

dd

或接地时,f

26

逻辑电路部分输出端f

26

为逻辑“1”,即相当于向f4逻辑电路部分输入逻辑“1”,f4逻辑电路部分输出为逻辑

“‑

1”,即f2逻辑电路的输出端f2为逻辑

“‑

1”;当输入端a接v

dd

时,f

26

逻辑电路部分输出端为逻辑“0”,即相当于向f4逻辑电路部分输入逻辑“0”,f4逻辑电路部分输出为逻辑“0”,即f2逻辑电路的输出端f2为逻辑“0”。

[0050]

对于f3逻辑电路,其由f

25

逻辑电路和f

19

逻辑电路级联构成。f

25

逻辑电路的输入端作为f3逻辑电路的输入端;f

25

逻辑电路的输出端f

25

与f

19

逻辑电路的输入端相连;f

19

逻辑电路的输出端作为f3逻辑电路的输出端f3。

[0051]

当输入端a接-v

dd

或接地时,f

25

逻辑电路部分输出端f

25

为逻辑“1”,即相当于向f

19

逻辑电路部分输入逻辑“1”,f

19

逻辑电路部分输出为逻辑

“‑

1”,即f3逻辑电路的输出端f3为逻辑

“‑

1”;当输入端a接v

dd

时,f

25

逻辑电路部分输出端为逻辑

“‑

1”,即相当于向f

19

逻辑电路部分输入逻辑

“‑

1”,f

19

逻辑电路部分输出为逻辑“1”,即f3逻辑电路的输出端f3为逻辑“1”。

[0052]

对于f7逻辑电路,其由f4逻辑电路和f9逻辑电路级联构成。f4逻辑电路的输入端作为f7逻辑电路的输入端;f4逻辑电路的输出端f4与f9逻辑电路的输入端相连;f9逻辑电路的输出端作为f7逻辑电路的输出端f7。

[0053]

当输入端a接-v

dd

或v

dd

时,f4逻辑电路部分输出端f4为逻辑

“‑

1”,即相当于向f9逻辑电路部分输入逻辑

“‑

1”,f9逻辑电路部分输出为逻辑

“‑

1”,即f7逻辑电路的输出端f7为逻辑

“‑

1”;当输入端a接地时,f4逻辑电路部分输出端为逻辑“0”,即相当于向f9逻辑电路部分输入逻辑“0”,f9逻辑电路部分输出为逻辑“1”,即f7逻辑电路的输出端f7为逻辑“1”。

[0054]

对于f8逻辑电路,其由f

20

逻辑电路和f

22

逻辑电路级联构成。f

20

逻辑电路的输入端作为f8逻辑电路的输入端;f

20

逻辑电路的输出端f

20

与f

22

逻辑电路的输入端相连;f

22

逻辑电路的输出端作为f8逻辑电路的输出端f8。

[0055]

当输入端a接-v

dd

时,f

20

逻辑电路部分输出端f

20

为逻辑“1”,即相当于向f

22

逻辑电路部分输入逻辑“1”,f

22

逻辑电路部分输出为逻辑

“‑

1”,即f8逻辑电路的输出端f8为逻辑

“‑

1”;当输入端a接地时,f

20

逻辑电路部分输出端为逻辑

“‑

1”,即相当于向f

22

逻辑电路部分输入逻辑

“‑

1”,f

22

逻辑电路部分输出为逻辑“1”,即f8逻辑电路的输出端f8为逻辑“1”;当输入端a接v

dd

时,f

20

逻辑电路部分输出端为逻辑“0”,即相当于向f

22

逻辑电路部分输入逻辑“0”,f

22

逻辑电路部分输出为逻辑“0”,即f8逻辑电路的输出端f8为逻辑“0”。

[0056]

对于f

11

逻辑电路,其由f7逻辑电路和f

16

逻辑电路级联构成。f7逻辑电路的输入端作为f

11

逻辑电路的输入端;f7逻辑电路的输出端f7与f

16

逻辑电路的输入端相连;f

16

逻辑电路的输出端作为f

11

逻辑电路的输出端f

11

。

[0057]

当输入端a接-v

dd

或v

dd

时,f7逻辑电路部分输出端f7为逻辑

“‑

1”,即相当于向f

16

逻辑电路部分输入逻辑

“‑

1”,f

16

逻辑电路部分输出为逻辑“0”,即f

11

逻辑电路的输出端f

11

为逻辑“0”;当输入端a接地时,f7逻辑电路部分输出端为逻辑“1”,即相当于向f

16

逻辑电路部分输入逻辑“1”,f

16

逻辑电路部分输出为逻辑

“‑

1”,即f

11

逻辑电路的输出端f

11

为逻辑

“‑

1”。

[0058]

对于f

12

逻辑电路,其由f

16

逻辑电路和f

22

逻辑电路级联构成。f

16

逻辑电路的输入端作为f

12

逻辑电路的输入端;f

16

逻辑电路的输出端f

16

与f

22

逻辑电路的输入端相连;f

22

逻辑电路的输出端作为f

12

逻辑电路的输出端f

12

。

[0059]

当输入端a接-v

dd

时,f

16

逻辑电路部分输出端f

16

为逻辑“0”,即相当于向f

22

逻辑电路部分输入逻辑“0”,f

22

逻辑电路部分输出为逻辑“0”,即f

12

逻辑电路的输出端f

12

为逻辑“0”;当输入端a接地时,f

16

逻辑电路部分输出端为逻辑“1”,即相当于向f

22

逻辑电路部分输入逻辑“1”,f

22

逻辑电路部分输出为逻辑

“‑

1”,即f

12

逻辑电路的输出端f

12

为逻辑

“‑

1”;当输入端a接v

dd

时,f

16

逻辑电路部分输出端为逻辑

“‑

1”,即相当于向f

22

逻辑电路部分输入逻辑

“‑

1”,f

22

逻辑电路部分输出为逻辑“1”,即f

12

逻辑电路的输出端f

12

为逻辑“1”。

[0060]

对于f

15

逻辑电路,其由f

25

逻辑电路和f

26

逻辑电路级联构成。f

25

逻辑电路的输入端作为f

15

逻辑电路的输入端;f

25

逻辑电路的输出端f

25

与f

26

逻辑电路的输入端相连;f

26

逻辑电路的输出端作为f

15

逻辑电路的输出端f

15

。

[0061]

当输入端a接-v

dd

或接地时,f

25

逻辑电路部分输出端f

25

为逻辑“1”,即相当于向f

26

逻辑电路部分输入逻辑“1”,f

26

逻辑电路部分输出为逻辑“0”,即f

15

逻辑电路的输出端f

15

为逻辑“0”;当输入端a接v

dd

时,f

25

逻辑电路部分输出端为逻辑

“‑

1”,即相当于向f

26

逻辑电路部分输入逻辑

“‑

1”,f

26

逻辑电路部分输出为逻辑“1”,即f

15

逻辑电路的输出端f

15

为逻辑“1”。

[0062]

对于f

17

逻辑电路,其由f4逻辑电路和f

16

逻辑电路级联构成。f4逻辑电路的输入端作为f

17

逻辑电路的输入端;f4逻辑电路的输出端f4与f

16

逻辑电路的输入端相连;f

16

逻辑电路的输出端作为f

17

逻辑电路的输出端f

17

。

[0063]

当输入端a接-v

dd

或v

dd

时,f4逻辑电路部分输出端f4为逻辑

“‑

1”,即相当于向f

16

逻辑电路部分输入逻辑

“‑

1”,f

16

逻辑电路部分输出为逻辑“0”,即f

17

逻辑电路的输出端f

17

为逻辑“0”;当输入端a接地时,f4逻辑电路部分输出端为逻辑“0”,即相当于向f

16

逻辑电路部分输入逻辑“0”,f

16

逻辑电路部分输出为逻辑“1”,即f

17

逻辑电路的输出端f

17

为逻辑“1”。

[0064]

对于f

21

逻辑电路,其由f

16

逻辑电路和f

25

逻辑电路级联构成。f

16

逻辑电路的输入端作为f

21

逻辑电路的输入端;f

16

逻辑电路的输出端f

16

与f

25

逻辑电路的输入端相连;f

25

逻辑电路的输出端作为f

21

逻辑电路的输出端f

21

。

[0065]

当输入端a接-v

dd

时,f

16

逻辑电路部分输出端f

16

为逻辑“0”,即相当于向f

25

逻辑电路部分输入逻辑“0”,f

25

逻辑电路部分输出为逻辑“1”,即f

21

逻辑电路的输出端f

21

为逻辑“1”;当输入端a接地时,f

16

逻辑电路部分输出端为逻辑“1”,即相当于向f

25

逻辑电路部分输入逻辑“1”,f

25

逻辑电路部分输出为逻辑

“‑

1”,即f

21

逻辑电路的输出端f

21

为逻辑

“‑

1”;当输入端a接v

dd

时,f

16

逻辑电路部分输出端为逻辑

“‑

1”,即相当于向f

25

逻辑电路部分输入逻辑

“‑

1”,f

25

逻辑电路部分输出为逻辑“1”,即f

21

逻辑电路的输出端f

21

为逻辑“1”。

[0066]

对于f

24

逻辑电路,其由f4逻辑电路和f

22

逻辑电路级联构成。f4逻辑电路的输入端作为f

24

逻辑电路的输入端;f4逻辑电路的输出端f4与f

22

逻辑电路的输入端相连;f

22

逻辑电路的输出端作为f

24

逻辑电路的输出端f

24

。

[0067]

当输入端a接-v

dd

或v

dd

时,f4逻辑电路部分输出端f4为逻辑

“‑

1”,即相当于向f

22

逻辑电路部分输入逻辑

“‑

1”,f

22

逻辑电路部分输出为逻辑“1”,即f

24

逻辑电路的输出端f

24

为逻辑“1”;当输入端a接地时,f4逻辑电路部分输出端为逻辑“0”,即相当于向f

22

逻辑电路部分输入逻辑“0”,f

22

逻辑电路部分输出为逻辑“0”,即f

24

逻辑电路的输出端f

24

为逻辑“0”。

[0068]

本领域的普通技术人员应当认识到,以上实施例仅是用来验证本发明,而并非作为对本发明的限定,只要是在本发明的范围内,对以上实施例的变化、变形都将落在本发明的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1